Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Целью изобретения является повьшение быстродействия запоминающего устройства. Устройство содержит накопитель информации на МДП-транзисторах, разрядный коммутатор, блок ключей, формирователь импульсов, ключевые элементы на транзисторах, триггер и усилитель считывания. Повышение быстродействия достигается за счет того, что при появлении информации на входахвыходах триггера ключевые транзисторы отключают его от разрядных шин. В результате триггер переключаясь в необходимое состояние, перезаряжает лишь небольшие емкости стоков ключевых транзисторов. 1 ил.

СОЮЗ СОВЕтСНИХ

РЕСПУБЛИН (59 4 G 11 С 11/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

0CYjLAPCTBEHHblA HOMHTET CCCP

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3904646/24-24 (22) 05.06.85 (46) 15.01,87. Бюл. М - 2 (72) Э.Э.Тенк (53) 681,327.6 (088.8) (56) IEEE Journal. of Solid State . Circuits, 1977, У 5, с. 497-501.

Авторское свидетельство СССР

Ф 1109804, кл. G 11 С 11/40, !984. (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродейст.,80„„1283854 А 1 вия запоминающего устройства. Устройство содержит накопитель информации на ИДП-транзисторах, разрядный коммутатор, блок ключей, формирователь импульсов, ключевые элементы на транзисторах, триггер и усилитель считывания. Повышение быстродействия достигается за счет того, что при появлении информации на входахвыходах триггера ключевые транзисторы отключают его от разрядных шин. В результате триггер переключаясь в необходимое состояние, перезаряжает лишь небольшие смкости стоков ключе" вых транзисторов ° 1 ил.

1283854

Изобретение относится к вычисли- тельной технике, в частности к устройствам памяти.

Целью изобретения является повышение быстродействия запоминающего устройства.

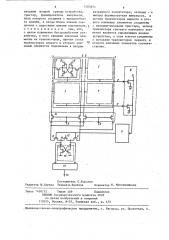

На чертеже представлена структур1 ная схема предлагаемого оперативного запоминающего устройства.

Устройство содержит накопитель, состоящий из ячеек 1 памяти, соединенных с адресными 2 и разрядными 3 шинами, разрядный коммутатор 4, пер.вый и второй ключевые элементы на транзисторах 5. Разрядные шины 3 подключены к выходам разрядного коммутатора 4, входы которого соединены со стоками пары транзисторов 5 и одновременно являются числовыми входами устройства, входы блока 6 ключей соединены с адресными шинами 2 и одновременно являются входами первой группы устройства, а выход блока 6 ключей соединен с входом формирователя 7 импульсов, выход которого соединен с затворами транзисторов 5, Стоки нагрузочных транзисторов ячеек памяти подключены к шине 8 питания. (Управляющие входы разрядного коммутатора 4 являются входами 9 второй группы устройства. Управляющим входом 10 устройства служит затвор транзистора 11 третьего ключевого элемента, сток и исток транзистора соединены с истоками транзисторов 5, входами-выходами триггера 12 и входами усилителя 13 считывания, выход 14 которого является информационным вы- 40 ходом устройства. Истоки транзисторов триггера 12 соединены с шиной 15 земли.

Устройство работает следующим образом. Я5

При отсутствии обращений разрядные шины 3 и входы разрядного коммутатора 4 заряжены от внешнего источника, а стоки транзисторов триггера

12 соединены через транзистор 11, от- о крытый сигналом по входу 10, и разряжены до напряжения, близкого к пороговому.

При обращении к устройству возбуждаются одна из адресных шин 2 и один 5 из входов 9. Далее в режиме считывания одна из разрядных шин 3 в каждом столбце матрицы разряжается через соответствующую ячейку 1 памяти, а разрядная шина 3 блока 6 ключей разряжается через один из ключей, соединенныи с возбужденной адресной шиной 2. Разряд шины 3 блока 6 (время разряда регулируется параметрами ключей блока 6) происходит значительно быстрее разряда шин 3 накопителя.

По окончании разряда шина 3 блока 6 формирователь 7 импульсов вырабатывает короткий управляющий сигнал, отпирающий транзисторы 5, подключая тем самым триггер 12 через коммутатор 4 к паре разрядных шин 3. Транзистор 11 при этом заперт, и триггер 12 после запирания транзисторов 5 устанавливается в состояние, соответствующее состоянию подключенной к нему ранее пары разрядных шин 3, за короткий промежуток времени, так как величина емкости .узла, к которому подключены сток транзистора триггера 12 и вход усилителя 13 считывания, мала по сравнению с суммарной емкостью разрядной шины 3 и входа коммутатора

4. При этом вход коммутатора 4, как и разрядная шина 3, успевают разрядиться лишь незначительно, что позволяет сократить энергию, затрачиваемую на предварительный заряд шин

3 и входов разрядного коммутатора 4.

Далее информация с входов-выходов триггера l2 через усилитель 13 считывания постулает на информационный вход-выход устройства.

В режиме записи, аналогично режиму считывания, возбуждаются одна иэ ,адресных шин 2 и один из входов 9.

Одновременно информация, имеющаяся на входах разрядного коммутатора 4, поступает через него на одну иэ пар разрядных шин 3 и устанавливает ячейку 1 памяти, подключенную к возбужденной адресной шике 2„ в необходимое состояние, Использование предлагаемого изобретения позволяет сократить время выборки адреса при считывании на lOX.

Формула изобр етения

Оперативное запоминающее устройство, содержащее матричный накопитель, адресные шины которого являются входами первой группы устройства, разрядные шины подключены к выходам разрядного коммутатора, входы которого являются числовыми входами устройства, а его управляющие входы—

1283854

Составитель С. Королев

Редактор N.Ñåðåäà Техред А.Кравчук Корректор M. Иаксимишинец

Заказ ?450/52 Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 входами второй группы устройства, триггер, формирователь импульсов, вход которого соединен с выходом блока ключей, а входы блока ключей соединены с адресными шинами накопителя, 5 о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены ключевые зле= менты на транзисторах, причем стоки транзисторов первого и второго ключевых элементов подключены к входам разрядного коммутатора, затворы — к выходу формирователя импульсов, а истоки транзисторов первого и второго ключевых элементов соединены с входами-выходами триггера, затвор транзистора третьего ключевого элемента является управляющим входом устройства, а сток и исток соединены с истоками транзисторов первого и второго ключевых элементов соответственно.