Статический регистр

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при проектировании регистров. Целью изобретения является расширение функциональных возможностей регистра за счет выполнения поразрядных логических операций. Для достижения этой цели в каждый разряд регистра введены элемент И-НЕ и элемент НЕ, а также общие для всех разрядов два элемента ИЛИ. Это позволило получать на выходах регистра функции x/Vi/;. , , , где X - состояние /-го разряда регистра , у - значение сигналана информационном входе i -ro разряда регистра. 1 ил. со о о сд СП 05

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (59 4 G 11 С 19 00

RCF-"."м

1ß о)) 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2!) 3975515/24-24 (22) 14.11.85 (46) 30.03.87. Бюл. № 12 (71) Грузинский политехнический институт им. В. И. Ленина (72) Л, Ш. Имнаишвили (53) 681.327.66 (088.8) (56) Угрюмов E. П. Элементы и узлы ЭЦВМ.

М.: Высшая школа, 1976, с. 199, рис. 10; 12в.

Авторское свидетельство СССР № 1069003, кл. G 11 С 19/00, 1981.

„„SU„„1300566 А1 (54) СТАТИЧЕСКИЙ РЕГИСТР (57) Изобретение относится к вычислительной технике и может быть использовано при проектировании регистров. Целью изобретения является расширение функциональных возможностей регистра за счет выполнения поразрядных логических операций. Для достижения этой цели в каждый разряд регистра введены элемент И-НЕ и элемент НЕ, а также общие для всех разрядов два элемента ИЛИ. Это позволило получать на выходах регистра функции х;1/у;, х;/ у;, х;1„/у;, х;/ у;, где х — состояние i-го разряда регистра, у — значение сигнала на информационном входеi-ro разряда регистра. 1 ил.

1300566

Форлиули изобретения

ЗО

Изобретение относится к вычислительной технике и может быть использовано при»роектировании регистров.

Цель изобретения — расширение функциональных возможностей регистра за счет выполнения поразрядных логических операций.

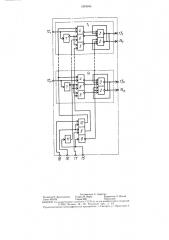

На чертеже приведена схема регистра, Статический регистр содержит в каждом разряде 1 RS-триггер, состоящий из элементов И-НЕ 2 и 3, три элемента И-НЕ 4 — 6 и элемент НЕ 7, а также общие для всех разрядов элемент НЕ 8, два элемента ИЛИ 9 и 10 и элемент 11 задержки. На чертеже показаны также информационные вход 12 и выходы 13 и 14 и четыре управляющих входа 15 — 18.

Статический регистр работает следующим образом.

Запись информации в регистр производится нарафазным кодом, поэтому не требуется его установки в исходное состояние.

Для записи информации в регистр высокий потенциал управляющего сигнала подается на второй управляющий вход 16. Управляющий сигнал, проходя через первый 9 и второй 10 элементы ИЛИ, открывает первый 4 и второй 5 элементы И НЕ. Если на входной информационной шине 12, присутствует логическая единица (высокий потенциал), то на выходной шине 13i появляется высокий потенциал, а в случае присутствия логического нуля на выходе 13, появляется низкий потенциал.

Запись информации в обратном коде происходит следующим образом.

Управляющий сигнал подается на первый управляющий вход 15. На выходе элемента

НЕ 8 устанавливается низкий потенциал, в результате чего все разряды регистра переходят в исходное состояние.

Через время т (т — время задержки сигнала в элементе задержки) управляк>щий сигнал открывает третий элемент И-HE 6.

Если на входной информационной шине 12; присутствует логический нуль, то на выходе элемента И-НЕ 6 появляется низкий потенциал, который на выходе !3; устанавливает логическую единицу. При этом на выходе

14; также присутствует логическая единица.

После снятия управляющего сигнала с входа 15 на выходе 14, устанавливается логический ноль, а на выходе 13; логическая единица остается. Время задержки сигнала в элементе 11 задержки должна быть т)3т,р, где т,-р — задержка сигнала в одном логическом элементе И-НЕ.

Если на информационном входе 12, присутствует логическая единица, то элемент

И-НЕ 6 соответствующего разряда 1 не открывается. При этом после снятия управляющего сигнала с входа 15 высокий потенциал на выходе !4; сохраняется.

В статическом регистре обеспечивается выполнение поразрядных логических операций от двух переменных.

Будем считать, что первая переменная х == xi, х2, ., х„находится в регистре, а вторая у = уь у2...., у„- — на входных информационных шинах 12i- !2, Если управляющий сигнал подать на четвертый управляющий вход 18, то открывается первый элемент И-НЕ 2 и в результате на выходе 13,: будем иметь сумму х, /у„ а на выходе 14, х;\/у,.

Если управляющий сип ал подать на третий управляющий вход 7, то на выходе 13; устанавливается у, / х„а на выходе 14; у /., В предлагаемом регистре имеется возможность инверсной записи информации, поэтому на нем можно осуществить также следующие логические операции: х /у — импликация от у к х; х/ у — запрет по у; х /у — импликация от х к и, х/,у — запрет по Х.

Таким образом, изобретение позволяет записать информацинэ в регистр в прямом и обратном коде, а также дополнительно реализовать восемь наиболее часто используемых в вычислительных машинах операций.

Статический регистр, содержащий элемент НЕ, элемент задержки и в каждом разряде RS-триггер и первый и второй элементы И-НЕ, причем первые 5- и R-входы

Я3-триггера соединены с выходами первого и второго элементов И-НЕ соответственно, первый вход первого элемента И-HE является информационным входом регистра, второй R-вход Я5-триггера каждого разряда соединен с выходом элемента НЕ, вход которого является входом з.-.писи в обратном коде, отличающийся тем, что, с целью расширения функциональных возможностей регистра за счет выполнения поразрядных логических операций, в него введены первый и второй элемен" û ИЛИ, а в каждый разряд — третий элемент И-HE и элемент НЕ, вход которого соединен с первым входом первого элемента И-НЕ, а выход -- с первыми входами второго и третьего элементов

И-НЕ, выход третьего элемента И-HE соединен с вторым,>-входом RS-триггера, вторые входы первого. второго и третьего элементов

И-HE каждого разряда соединены соответственно с выходами второго и первого элементов ИЛИ и элемента задержки, вход которого соединен с входом элемента НЕ, первые входы первого и второго элементов

ИЛИ являются входом записи в прямом коде, а вторые входы — первым и вторым входами задания вида функции.

1300566

1ZZ

741

17,7

М Ю 17 15

Соста в и тел ь А. Дерюги н

Редактор H. Киштулинец Техред И. Верес Корректор Л. Патай

Заказ 829/52 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4