Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для построения оперативных запоминающих устройств с частичным резервированием блоков памяти. Цель изобретения - упрощение и повыщение надежности устройства. Устройство содержит одноразрядные основные 1 и резервный 2 блоки памяти, коммутатор 3, блок 10 свертки по модулю два, регистр 11 и элементы И 12. При всех исправных блоках 1 и 2 блок 10 используется для контроля четности, а при одном неисправном блоке 1 - для формирования суммы по модулю два содержимого блока 2 и всех блоков 1, кроме неисправного , которая и равна содержимому неисправного блока 1.3 ил. ( со о ьо 00 to 4 Фиг.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК дц 4 G 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCXOlVIV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3920100/24-24 (22) 06.05.85 (46) 07.04.87. Бюл. № 13 (71) Институт технической кибернетики

АН БССР (72) Н. Ф. Морозов, В. А. Дубовский и М. В. Криворот (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 903973, кл. G 11 С 11/00, 1978.

Авторское свидетельство СССР № 607276, кл. G ll С 11/00, 1975. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С САМОКОНТРОЛЕМ

„„SU„„1302324 А1 (57) Изобретение относится к вычислительной технике и может быть использовано для построения оперативных запоминающих устройств с частичным резервированием блоков памяти. Цель изобретения — упрощение и повышение надежности устройства.

Устройство содержит одноразрядные основные 1 и резервный 2 блоки памяти, коммутатор 3, блок 10 свертки по модулю два, регистр 11 и элементы И- 12. При всех исправных блоках 1 и 2 блок 10 используется для контроля четности, а при одном неисправном блоке 1 — для формирования суммы по модулю два содержимого блока 2 и всех блоков 1, кроме неисправного, которая и равна содержимому неисправного блока 1.3 ил.

1302324

f5

Формула изобретения

Изобретение относится к вычислительной технике и может быть использовано для построения оперативных запоминающих устройств с частичным резервированием блоков памяти.

Цель изобретения — упрощение и повышение надежности утройства.

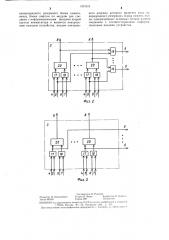

На фиг. 1 изображена структурная схема запоминающего устройства с самоконтролем; на фиг. 2 и 3 — структурные:схемы двух вариантов коммутатора.

Устройство содержит одноразрядные основные 1, резервный 2 блоки памяти, коммутатор 3, имеющий первую группу информационных входов 4, первую группу управляющих входов 5, вторую группу управляющих входов 6, вторую группу информационных входов 7, первую и вторую группы информационных выходов 8 и 9, блок 10 свертки по модулю два, регистр 11 и элементы И 12. Устройство имеет информационные входы 13, управляющий вход

14, вход 5 контрольного разряда и контрольный выход 16.

Первый вариант коммутатора 3 содержит (фиг. 2) элементы И 17 — 9 и элементы ИЛИ 20, второй вариант (фиг. 3) элементы И 17 и 18 и элементы ИЛИ 20.

Устройство работает следующим образом.

В исходном состоянии (все блоки 1 и 2 исправны) при отсутствии сигнала на входе !

4 элементы И 12 закрыты, регистр 11 установлен в нулевое состояние (на прямых выходах нулевой сигнал, а на инверсных выходах — единичный). Единичный сигнал с инверсных выходов регистра 11, поступающий на входы 5, разрешает прохождение информации с выходов блоков 1 на выходы 8 и 9 устройства, а нулевой сигнал с прямых выходов регистра 11, поступающий на входы 6, запрещает прохождение сигналов с выхода блока 10. При записи информация с входов 13 и контрольный разряд четности с входа 15 записываются в блоки 1 и 2 соответственно. При считывании информация с выходов блоков 1 поступает на выходы 8 устройства и на входы блока 10, на который также поступает с выхода блока 2 контрольный разряд четности. Если из блоков 1 и 2 поступает верная информация, то на выход 16 поступает нулевой сигнал при контроле на чет ность.

При нали ии неисправности одного из блоков 1 на вход 14 подается сигнал, который открывает элементы И 12 и с входов 13 через элементы И 12 подается код на единичные входы регистра 11, причем в коде нули соответствуют исправным блокам 1, а единица — неисправному. В результате этого все разряды регистра 11 остаются в нулевом состоянии, кроме разряда, соответствующего неисправному блоку 1. Затем сигнал снимается с входа 14 и элементы И 12 закрываются.

Записанная в соответствующий разряд регистра 11 единица приводит к подаче на соответствующий вход 5 нулевого сигнала, который запрещает прохождение информации с выхода соответствующего блока 1 на соответствующие ему выходы 8 и 9. Единичный сигнал, поступающий на соответствующий вход 6 с соответствующего разряда регистра 11, разрешает прохождение сигнала с выхода блока 10 на соответствующий выход 8. При этом сигнал контроля четности с выхода 16 не используется для контроля. В случае контроля по нечетности достаточно на входы 7 подать инвертированный выход с блока 10.

В первом варианте коммутатора 3 (фиг. 2) информация подается через элементы И 19 на выходы 9 с выходов элементов ИЛИ 20, а управление прохождением информации осушествляется входами

5 и 6 коммутатора 3, что позволяет контролировать непосредственно выходы элементов ИЛИ 20.

Во втором варианте коммутатора 3 (фиг. 3) информация подается на выходы 9 непосредственно с выходов элементов И 17, управляемых входами 5 коммутатора 3, что позволяет исключить группу элементов И 19.

Таким образом, при всех исправных блоках 1 и 2 блок 10 используется для контроля четности, а при одном неисправном блоке 1 — для формирования суммы по модулю два содержимого блока 2 и всех блоков 1, кроме неисправного, которая и равна содержимому неисправного блока 1.

Запоминающее устройство с самоконтролем, содержащее одноразрядные основные блоки памяти, одноразрядный резервный блок памяти, элементы И, коммутатор и регистр, входы которого соединены с выходами элементов И, первые входы которых являются информационными входами устройства, а вторые входы элементов И объединены и являются управляющим входом устройства, выходы одноразрядных основных блоков памяти соединены с соответствующими информационными входами первой группы коммутатора, управляющие входы первой группы коммутатора соединены с соответствующими инверсными входами регистра, прямые выходы которого соединены с соответствующими управляющими входами второй группы коммутатора, выходы первой группы которого являются информационными выходами устройства, отличающееся тем, что, с целью упрощения и повышения надежности устройства, в него введен блок свертки по модулю два, входы которого соединены с информационными выходами коммутатора второй группы и выходом

1302324

Фиг. 2

Фиг. 3

Составитель В. Рудаков

Редактор И. Николайчук Техред И. Верес Корректор Н. Король

3 а к аз 949/50 Тираж 590 Поди иснос

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 415

Производственно-полиграфическое предприятие, г. Ужгороl, ул. Проектная, 4 одноразрядного резервного блока памяти, выход блока свертки по модулю два соединен с информационными входами второй группы коммутатора и является контрольным выходом устройства, входом контрольного разряда которого является вход одноразрядного резервного блока памяти, Входы одноразрядных основных блоков памяти соединены с соответствующими информационными входами устройства.