Конвейерное вычислительное устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К A BTOPCKOMY СВИДЕТЕЛЬСТВУ (2)) 3964167/24-24 (22) 11.10.85 (46) 07.07.87. Бюл. 9 25 (71) Дагестанский политехнический институт (72) И.А. Айдемиров и Ш.-11.А. Исмаилов (53) 681.325.5(088.8) (56) Авторское свидетельство СССР

Ф 1062689, кл. С 06 F 7/50, 1982.

Авторское свидетельство СССР

Ф 1206281, кл. G 06 F 7/50, 1984. (54) КОНВЕЙЕРНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (7) Изобретение относится к вычислительной технике и предназначено для осуществления групповых операций суммирования и умножения. Целью изобретения является расширение функциональных воэможностей устройства за счет реализации операции вычисления

„„SU„, 1 22261 А1 м L сумм вида Р= 3 А ....А; + g В., где

Н вЂ” количество пар перемножаемых k разрядных чисел А,, А, L — количество одновременно суммируемых чисел в режиме умножения. Цель достигается разбиением первого яруса на Н секций, каждая из которых содержит преобразователь кода числа в двоичный код количества единиц и группу иэ К элементов И-ИЛИ. Кроме того, устройство дополнительно содержит две группы элементов ЗАПРЕТ и выходной регистр сдвига и новые связи. Это позволяет реализовать дополнительно операцию группового суммирования произведений пар чисел, которые заносятся в первый и второй регистры, соединенные с элементами И-ИЛИ каждой секции.

Данные регистры выделяются как реги" С стры множимого и множителя для каждой пары чисел. 2 ил.

)3222

Изооретение относится к вычисли тельной технике и может быть использовано в высокопроизводительных и специализированных ЭВ1"1.

Цель изобретения — расширение 5 функциональных возможностей за счет реализации операции вычисления сумм вида н L

1 21 10

11 j.1 где Н вЂ” множество пар перемножаемых

К-разрядных чисел; количество одновременно суммируемых чисел в режиме умножения. 15

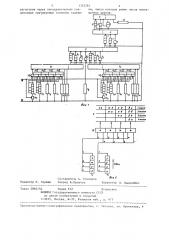

На фиг. 1 приведена структурная схема конвейерного вычислительного устройства; на фиг. 2 — иллюстрация процесса вычисления произведения.

Предлагаемое устройство, (фиг. 1) 20 предназначено для одновременного суммирования пятнадцати чисел и суммирования двух гроизведений и пяти дополнительных чисел (F1=2, L=5).

Устройство содержит входные регист-25 ры 1, блоки 2-5 преобразования кода числа в двоичный код количества единиц, организованные в четыре яруса, при этом первый ярус разбит на две секции, тактируемые элементы 6-9 задержки, соединенные последовательно, выходной регистр 10 сдвига, две груцпы 11 и 12 элементов И-ИЛИ и две группы 13 и 14 элементов 3AIIPET, а также тактовую шину 15 и шину 16 уп. равления.

Устройство работает следующим образом.

В режиме сложения на шину 16 уп — 40 равления подается уровень логического нуля. Во входные регистры 1 записынаются склацынаемые числа, которые

"-атем поступают одноименными разрядами (младшими разрядами вперед) с 45 последовательных выходон регистров

1 через логические элементы И-ИЛИ ll и 12 и ЗАПРЕТ 13 на входы блоков 2 или через тактпруемый элемент 6 задержки на один из входов 50 блока 3 преобразования. Тактируемые элементы задержки, входные регистры и выходной регистр сдвига тактируются одним и тем же тактовым сигналом.

Разрядные срезы, поступающие н тече- 55 ние каждого так га ц» входы блоков 2, рассматриваются в них как адрес потониной памяти, по которому на выход бчока ;чптынао!.ся соотн(тс!нующий

61 2 двоичный код количества единиц в поступившем разрядном срезе.

Полученные коды количества единиц в разных разрядных срезах су г ируются с учетом их веса, т.е. со сдвигом на один разряд в сторону старших разрядов относительно друг друга. Для этой цели служат блоки 2-5 преобразования и тактируемые элементы 6-8 задержки, осуществляющие сдвиг во времени кодов числа единиц. На выходе блока 5 преобразования формируется двухразрядный код, один из разрядов которого является очередной цифрой суммы, а другой — сигналом переноса.

С помощью элементов 9 задержки сигнал переноса задерживается и суммируется с кодом числа единиц слецующего разрядного среза на том же блоке 5 преобразования. Цифра суммы записывается в выходной регистр 10 сдвига. После поступления К-разрядных срезов на входы блока 2 с выходов регистров 1 устройство продолжает работать еще несколько тактов, пока не будет пропущена вся информация, запомненная в элементах задержки. В это время на входы блоков 2 и элемента 6 задержки могут поступать нуле2 вые коды.

При подаче на шину 16 управления единичного уровня элементы ЗАПРЕТ 13 и 14 закрываются, запрещая поступление тактовых импульсов с шины 15 на

cHi xpoaxoqar регистров 1 и 1> хранятся множимые, и значений выходных (младших ) разрядов этих регистров на входы блоков 2. Через элементы

И-ИЛИ ll и 12 на входы блоков 2 и

2 подаются в каждом такте коды мно». жимых со сдвигом на соответствующее число разрядов из регистров 1 и 1„ причем только через те элементы

И-ИЛИ 11 и 12, на входы которых поступают единичные уровни с соответствующих разрядов регистров 1 и 1э.

Таким образом, с выходов элементов

И-ИЛИ 11 и 12 на входы блоков 2 поступают частичные произведения, в результате суммирования которых вычисляются произведения соответствующих пар чисел. На остальные входы блоков

2 и на вход элемента 6 задержки как и ранее поступают числа, записанные во входных регистрах 1 -1, 1 + и

j« которые суммируются с частичными произведениями перемножаемых чи" сел. з !32226

Таким образом, при единичном уровне на шине 16 устройство реализует о и л

Фруу

AI+A Ь ! 1 где А„, А, А>, А „ — числа, записанрегистрах !., 1> 1 ответственно, В, — числа, записанные в остальных регистрах 1.

При соответствующем увеличении числа входов устройство реализует формулу

P =, А,, А .+,» В., 1 где Н вЂ” количество перемножаемых пар

К-разрядных чисел, М=K+L+H — общее число входов устройства.

15

Ф о р м у л а и з о б р е т е н и я

Конвейерное вычислительное устройство, содержащее входные регистры, блоки преобразования кода числа в двоичный код количества единиц и тактируемые элементы задержки,* причем25 блоки преобразования кода числа в двоичный код количества единиц объединены в ярусы, выходы блоков преобразования кода числа в двоичный код количества единиц каждого яруса, кро- 30 ме верхнего, соединены через последовательно соединенные тактируемые элементы задержки с входами блоков преобразования кода числа в двоичный код количества единиц следующего яруса, причем количество тактируемых элементов задержки, соединенных последовательно, равно номеру разряда выхода блока преобразования кода числа в двоичный код количества единиц, выход40 старшего разряда блока преобразования кода числа в двоичный код количества единиц верхнего яруса соединен через два последовательно соединенных тактируемых элемента задержки с первым 45 входом того же блока преобразования кода числа в двоичный код количества единиц, тактовые входы всех тактируемых элементов задержки соединены с тактовой шиной устройства, о т л и— ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей эа счет реализации операции вычисления сумм вида

Н L

Р=с» А, А + В1, )= 1 где Н вЂ” количество пар перемножаемых

К-разрядных чисел А,, A>, L — количество одно!!ременно сумл)ируемых чисел в режиме умножения, первый ярус содержит Н секций, кажлая из которых содержит блок преобразования кода числа в двоич)п,!й! код количества единиц и группу из К элементов И-ИЛИ, входные регистры также разбиты на

Н секций, устройство дополнительно содержит выходной регистр сдвига и две группы элементов ЗАПРЕТ, причем тактовые входы первых входных регистров каждой секции соединены с выходами соответствующих элементов ЗАПРЕТ первой группы, прямые входы которых соединены с тактовой шиной устройства, а инверсные входы — с шиной управления устройства, тактовые входы остальных входных регистров всех секций вьгходного регистра сдвига соединены с тактовой шиной устройства, выход младшего разряда первого входного регистра каждой секции соединен с прямым входом соответствующего элемента ЗАПРЕТ второй группы, инверсный вход которого соединен с шиной управления устройства, а выход — с входом блока преобразования кода числа в двоичный код количества единиц соответствующей секции первого яруса, выходы разрядов первого регистра каждой секции соединены с первыми входами соответствующих элементов И-ИЛИ соответствующей секции, вторые входы которых подключены к выходам разрядов второго входного регистра той же секции, третий и четвертый инверсный вхоДы всех элементов И-ИЛИ всех секций соединены с шиной управления устройства, а пятые входы элементов

И вЂ И каждой секции соединены с выходами младших разрядов входных регистров с третьего по К-й соответствующей секции, выходы элементов И-ИЛИ каждой секции подключены к входам соответствующего блока преобразования кода числа в двоичный код количества единиц первого яруса, выходы младших разрядов остальных входных регистров каждой секции соединены с входами соответствующих блоков преобразования кода числа в двоичный код количества единиц первого яруса, выход младшего разряда блока преобразования кода числа в двоичный код количества единиц верхнего яруса подключен к входу младшего разряда выходногО регистра сдвига, входы блоков преобразования всех ярусов, кроме первого, подключены к выходам млапш!)х р;)зрядов входных

1322261 ки, число которых равно числу пропущенных ярусов, регистров через последовательно соединенные тактируемые элементы задерж/! г

Фиг 2

Составитель A. Степанов

Редактор П. Гереши Техред А.Кравчук Корректор Л. Пилипенко

Заказ 2864/44 Тираж 672 Подписное

ВНИИ11И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Проиэнодственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4