Устройство для сопряжения процессора с памятью

Иллюстрации

Показать всеРеферат

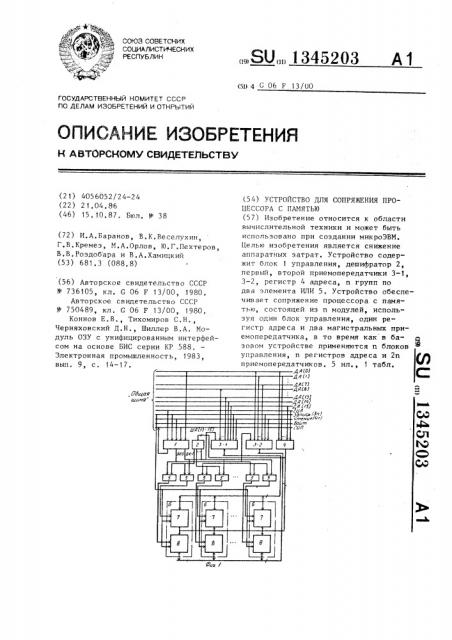

Изобретение относится к области вычислительной техники и может быть использовано при создании микроЭВМ. Целью изобретения является снижение аппаратных затрат. Устройство содержит блок 1 управления, дешифратор 2, первьй, второй приемопередатчики 3-1, 3-2, регистр 4 адреса, п групп по два элемента ИЛИ 5, Устройство обеспечивает сопряжение процессора с памятью , состоящей из п модулей, используя один блок управления, один регистр адреса и два магистральных приемопередатчика , в то время как в базовом устройстве применяются п блоков управления, п регистров адреса и 2п приемопередатчиков. 5 ил., 1 табл. с S (Л 00 4 СП ND О СО

СО!ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!) 4 G 06 F 13/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flG ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4056052/24-24 (22) 2 1,04. 86 (46) 15. 10.87. Бюл. Ие 38 (72) И.А. Баранов, В. К. Веселухин, Г. В, Кремез, М. A.Îðëîâ, Ю. Г. Пехте ров, В.В.Роздобара и В.А.Хамицкий (53) 681. 3 (088. 8) (56) Авторское свидетельство СССР

9 736105, кл. G 06 F 13/00, 1980.

Авторское свидетельство СССР !!е 750489, кл, С 06 F 13/00, 1980.

Коннов Е.В., Тихомиров С.Н., Черняховский Д.Н., Шиллер В.А. Модуль ОЗУ с унифицированным интерфейсом на основе БИС серии КР 588.

Электронная промышленность, 1983, вып. 9, с. 14-17.

„„SU„„1345203 А I (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С ПАМЯТЬЮ (57) Изобретение относится к области вычислительной техники и может быть использонано при создании микроЭВМ.

Целью изобретения является снижение аппаратных затрат. Устройство содержит блок 1 управления, дешифратор 2, первый, второй приемопередатчики 3-1, 3-2, регистр 4 адреса, и групп по два элемента ИЧИ 5, Устройство обеспечин ает сопряжение процессора с памятью, состояцей из п модулей, используя один блок упранления, один регистр адреса и два магистральных приемопередатчика, в то время как в ба- д зовом устройстве применяются п блоков управления, и регистров адреса и 2п приемопередатчикон. 5 ил,, 1 табл. дяди С: дяде дясл дясвг дя (x я(М

Маей я(%

gunuco < /

ыя

0Р

Qm eNui (u>) ь ип

1 134, Изобретение относит<.я к нычс«слительной технике и может быть исппль— зонано при создании микроЭВМ.

Цель изобретения — снижение а.-паратных затрат, На фиг. 1 приведена структурная схема устройства, подсоедине.. ного, 11 . I I например, к магистрали Общая шика микроЭВМ "Электроника-60", совместно с ll модулями операTHBHGI памяти; на фиг. 2 — структурная схема одного vç вариантов реализации блока управления (на основе ИМС К) 588ВГ2); на фиг ° 3 — структурная схема одного к.:I вариантов реализации магистральногс приемопередатчика (на основе ИМС

KP588BA1), на фиг. 4 — функциональная схема одного из вариантов модуля opеративной памяти емкостью 4Кх16 (на основе ИМС КР537РУ2А); ка фи« . 5 временная диаграмма работы устройства,.

Устройство для сопряжения процессора с памятью содержит (фиг„ 1) б.с<ок управления, дешифратор 2, первый«, второй приемопередатчики 3- „ 3 — 2, 1 регистр 4 адреса, 2п элементов ИЛИ 5, п модулей 6 оперативкой памяти, н состав каждого из которых входят блоки хранения старших 7 и млад1<сс«х Я зсмк байтов .

Блок 1 управления предна значе к дл>я управления работой voòðoéñòÿ:1 посрс:дтвом формирования сигналов выборки блока хранения младших или старших байтов н модуле памяти, соответственно ВКО и ВК1, а также сигнала синхронизации пассивного устройства (СИП,< на основе управляющей информации, поступающей o T проце с.с о ра, 40

Дешифратор 2 служит для определения модуля памяти, к которому произ— водится обращение, и управления передачей в него сигналов выборки HKO u 8KI от блока 1. Данный б1лок представ- 4.— .пяет собой дешифратор с инверсными выходами по количеству подключаемых модулей памяти.

Двунаправленные приемопередатчи:си

3-1, 3-2 предназначены для передач « информации посредством <нины данных (ШД), либо из магистрали в память, либо в обратном направлении, Регисгр

4 адреса предназначен для запоминания кода адреса, по которому произзо1 цится обращение к памяти, и устанозки его посредством шины адреса (ША) нз адресных входах модулей памяти. Эл — ченты ИЛИ 5 служат для перед чи уп—

О) 2 рлнляющн.- . с<сгн;< сс н )> ;T) с <>K I <<т Inлс<ка

1 Io:п>ко и тот «n! v!I II;Iмяти, к ".с rn— рому Ilpoll .водится обоаще<

6 памяти I:редназнл се «ы для хранения кодов. Блс.ки хране IHH старших 7 и

I".«.адших Я б ай то н e ly, «:IT Лля х ране «ия, соответс "> пенно, 8-15 H 0-7 разрядов. записанньсх в мо««ул, 6 памяти 16-разрядных слон.

/ ,лок управления А,«г. 2, реалн

",îHHHHûé на основе микросхемы

КР5ЯЯВГ?, содержит peгистр 9 адреса модуля памяти, элеме«т 10 сравнения ац)зеса, элемент 11 управления обменом, элемент 12 выборки, элемент 13 моделиронRHHR;ll«êëÿ обращения к загомикающему устройст:зу, а также дне

НС-цело II>I Е,, С, и К2, С, Информа—

I„.ионные нходы регистра 9 объединены с входами задания адреса модуля памяти элемента 10 сравнения. Параметры

RC-цепочек, определяющих задержку выдачи сигнала CHIL относительно сигналов ВКО и ВК1 при считызакии или записи соответственно, подбираются в зазисимости от быстродействия используемых н модуле ОЗУ <икросхем, 11риемопередатчики 3-1, 3-2 (фиг.3) выполненьI на основе «икросхем КР588ВА, с одержат олок 14 уси.«ителей канала

К2, блок 15 усилителей канала К1 и блок 16 управления, Информационные входы-вь<ходы приемопередатчиков сое— дикены соответственно с блоками 14 и 15, а I«x управляющими входами служат входы блока 16.

Устро«ство работает следующим образом.

Работ - устрсйства показана на примере сопряжения процессора с ОЗУ емкостью 7.K 16-разрядных слов, Г)ри сбоащеник к ОЗУ (фиг, 5) процессор уста «анлинaют ка шинах данных — адреса магистрали Общая шина

,ДА) <О-151 асрес. слова, в котором значенис !IA (Г)1 определяет к старшему или младшему байту адресуемого слона производится обращение,, ДА с"

; 1 — 12з спределяют адрес слова к моду.по ОЗУ к ДА Г13-15„ — номер модуля

ОЗУ, Зат =-.ì проке ссор выставляет сигнал СИЛ = О, пс; котсрому адресное слово залi«oI:лаете=I в регистр 4 адреса. Кроь е -.о<-с, д; —.нный сигнал постуI àåò н б .ок 1 и икиниирует запоминание н э.с ..еH Tå 11 уп ранле< ия обменом

Г блока 1 гигHRJIÎB с II HH ДЛ О, и Байт, .-.оследн«. из которых определяет раз! 341203 рядность адресуемых слов (если Байт = — 1, то устройство работает с 18 16разрядными словами, если Байт =- 0 то устройство работает с байтами) . По

6 сигналу СИЛ = 0 осуществляется срав— нение на элементе 10 сигналов на входах регистра 9 Д1, Д2 и ДЗ с сигналами на входах задания адреса модуля

ОЗУ Л1, Л2 и АЗ, Поскольку указан- 10 ные входы объединены, то на выходе элемента 10 сравнения формируется сигнал разрешения формирования управляющих сигналов ВКО, ВК1 и СИП, поступающий в элементы выборки 12 и мо- !ч делирования 13 цикла обращения. R результате на выходах элемента !3 "Задержка чтения (ЗД Чт) и Задержка записи" (ЗД Зп) устанавливается низкий уровень напряжения (разряжаются 20 емкости цепочек R C и Н С ) . Код

1 1 номера модуля ОЗУ поступает по ША (13-15! из регистра 4 адреса на входы дешифратора 2 и устанавливает ну2Г1 левой сигнал на соответствующем адре- 2- суемому модулю выходе дешифратора.

После этого процессор снимает адрес с магистрали "Общая шина".

При считывании данных из модуля

ОЗУ (цикл "Ввод" на фиг, 5) процессор 30 устанавливает нулевой сигнал на шине

"Запись" магистрали "Общая шина" (Зп = О), Данный сигнал, поступая в блок 1, вызывает формирование на его выходах сигналов ВКО и ВК1 в зависимости от сигналов Байт и ДЛ !.О! по следующей таблице.

Кроме того, по сигналу Зп = О напряжение на выходе ЗД Чт начинает рас- 40 ти с постоянной времени цепочки R Ñ,.

Сформированные на выходах блока 1 нулевые сигналы RKO и ВК1 посредством элементов ИПИ 5, управляемых дешифратором 2, передаются в адресуемый 45 модуль 6 оперативной памяти на входы разрешения обращения к микросхемам

ОЗУ (СЕ на фиг. 4) . При этом на вход режима работа микросхем (WR/RO) с шины Запись" магистрали "Общая шина" поступает нулевой сигнал, что соответствует режиму чтения, а на их адресные входы — код адреса по ША (1-123 с регистра 4 адреса, R результате производится считывание информации иэ 5

ОЗУ, которая устанавливается на ШД

ОЗУ Г8-15j и !О-7j в зависимости от разрядности считываемого слова, определяемого нулевыми сигналами RK.

Считанньlo данные поступают в KR нал KZ приемопередатчиков 3 — 1, 3-2.

Приемопередатчики, на управляющие входы которых поступают нулевые сиг— нальt ВК,,обеспечивают передачу данных из канала К2 посредством блока 15 усилителей канала, через канал К1 в магистраль Общая шина на шины ДЛ (0-151, поскольку сигнал ЗП-О, поступающий в блок 16 управления, настраивает приемопередатчик на передачу информации из К2 в К1, 1(осле того, как напряжение на выходе элемента 13 ЗД Чт достигает определенного уровня, формируется сигнал СИП = О, который поступает в магистраль Общая шина 1 и служит для процессора сигналом квитирования, сообщающим о передаче данных из ОЗУ в магистраль. По этому сигналу процессор считывает данные иэ магистрали и снимает сигнал "Запись" (Зп=1). В результате блок 1 перестает формировать нулевые сигналы ВК и СИП (ВКО = ВК1

СИП = 1), последний из которых инициирует установку процессором СИА=1, что, в свою очередь, приводит к установке блока 1 в исходное состояние.

На этом цикл обращения к ОЗУ завершен.

Запись данных в модуль ОЗУ (цикл

"Вывод" на фиг. 5) производится аналогично циклу считывания. Отличие заключается в том, что вместо сигнала Запись процессор формирует сигнал Чтение".,В результате микросхемы адресуемого модуля 6 ОЗУ работают в режиме записи (на вход WR/RO поступает единица). Магистральные приемопередатчики передают данные иэ магистрали

"Общая шина" в ОЗУ (сигналом Чт = О они настроены на передачу информации из канала К1 в канал К2).. Задержка формирования сигнала СИП = О определяется цепочкой R С ., подключенной к

L выходу ЗД Зп блока 1. Кроме того, данные на магистраль "Общая шина" в цикле Вывод выставляет процессор в течение времени после формирования сигнала Чт = О (7, определяется задержкой блока 1 на формирование сигналов ВК), Сигнал СИП .= О сообщает процессору о записи данных в ОЗУ ! и вызывает снятие последним данных с магистрали и установку сигналов ЧТ= — ВКО = RK1 = 1 и далее СИП = 1, СИА = 1.

При сопряжении с постоянной памятью предлагаемое устройство работает

1, 1" Гi 1

Барр)l(A0 j BEG (Рк! 1 приме р ар ие

О О

О 1

X Х лично тОлькО В режиме с Гиты и I е!ия 1(з ГГам51т ( реализуя цикл Ввод

Форм улаиэобpeтeнил (Устройство для сопряжения процес-сора с памятью, содерж;ш-,ее блок y!Iравления, регистр адреса, Ilpðÿûé, BT() рой приемопередатчики„причем первьк входы-выходь1 первого, второго прие!опередатчиков соединены с входами-вь(ходами устройства для подключения сэ— ответственно входов-выходов старшег о и младшего байтов данных — адреса процессора, первый, второй входы задания направления передачи ин(1?ормации первого, второго приемопередатчиков подключены к входам устройства для подключения выходов чтения и записи процессора, входь1 выборки первого, второго приемопередатчиков соединены соответственно с первым, вторым выходами блока управления, третий выход которого соединен с выходом устройства для подключения к входу синх— ронизации процессора, с первого по ,пятый входы блока управления соединены с входами устройства для подклю .ения выходов записи, чтения, з аданив режима работы с даннымир сичхронизац;.11 и ну: i (1(11 (l!;I 1пчда данных — адреса про((еcc(ра, вх(1 i еl 1(тр l Вдре(а (-оединен с Входом ус I р(йства для ГтодК.IЮР(РНИЯ В ГХОД(-: Дав .IЬ X — ПДРЕ((р(ПPO— це ссора, в торые Входы — вь(ходы первого, в то рого Г!р ие моп ер едатч иков сne диГ(е lib! с входами — Г» (ходами v c трой стг а для подключения соответственно входов — выходов дан(н Гх м.чадпих и старших paR ряДОГ(памят, Вь(ход ppгнс тра адреса соедине1(р Выходом y (:òðnéñòBà для по,(Гк.(ГГоче(ин к аДРесномУ вхоДУ памнтир о т л и, а ю ш е е с я темр что„ с целью "нижения аппаратных затрат, В него RRO;låIIbI де(11ИАратор на и выходов (и число модул(й памяти) и и групп по Г(ва элемента ИЛИ в каждой группе, .;;pи(1ем первь1е входы перво -o,. второго .:лементов ИЛИ i-i-póièòbi (i

1, и) (.оедннены с х -м выходом дешифРатоРа, ВтоРые вхоДЬ1 пеРвогор втоРого элементов ИЛИ всех групп соединены соответственно с первым, вторым выходами блока управления, вход дешифратора соединен с выходом регистра адреса, выходы первого, второго элементов

И(1И всех групп соединены с группой Bbl хо QB устройства для подключения входог. выборки модулей памяти.

3 апис;..— считывание 16-раз рядного слова ЛА 1.0 . — ЛА (151

Запись в младший байт ЛА Г О JЛА 171

Запись в страший байт ЛА 11 Р 1 —

ЛА (15) Нет выборки

Х вЂ” =",н аче ние сиг1: ала бе з раз1 >i ) 20 )

Зал

Чт бп ,Р

0- 73

153) Я4

Ф.л 1

СЦА

Запись Т

Чтение

äéÎ д/й — (1 аи - !

5А V;545nP! с аю „РОС"

q."i (g.

Составите.,:;.:,, П;pухин

Техред .П,Сердюкова

Редактор И.1(асарда

Корректор И. 1 !арощи

Заказ 4922/48 1 ира,ф Q7, С

ВНИИПИ Ро суда рстве нного кс мите та СССР по девам изобретений и откр:тпй

11 3035 Москва, Ж-35, Р;;.уп с кая I . а6 „„, „4! 5

Ио, |иг;! иПроизводственно-по".играАическое прсдприят -., г, У ;: лроп, у:1, П н ктная, 4