Усилитель считывания на кмдп - транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах , выполненных из КМД11-транзисторов, для усиления сигналов считываемой информации. Целью изобретения является повьшение надежности усилителя за счет повы циента усиления. ния содержит два тора 1, 2, четыре зистора 3-6 п-ти ных транзистора 7 ляющий транзистор транзисторы 19-22 инвертирующие тра типа. Затворы тра и транзисторов 7, ляются входом 15 работы усилителя, и третьего 5, вто 6 переключающих т ветственно объеди формационными рхо теля, выходами 13 ляются сток и ист Коэффициент усиле за счет введения ратной связи, обе зисторами 17 и 18 10 .k. теля за счет повышения его коэффициента усиления. Усилитель считывания содержит два управляющих транзистора 1, 2, четыре перек.гаочающих транзистора 3-6 п-типа, два установочных транзистора 7, 8, третий управляющий транзистор 16, нагрузочные транзисторы 19-22 и вновь введенные инвертирующие транзисторы 17, 18 ртипа. Затворы транзисторов 1, 2, 16 и транзисторов 7, 8 объединены и яв-. ляются входом 15 управления режимом работы усилителя, затворы первого 3 и третьего 5, второго 4 и четвертого 6 переключающих транзисторов соответственно объединена п явJтяmтcя информационными рходами 11, 12 усилителя , выходами 13 и 1А которого являются сток и исток трпнзистора 16. Коэффициент усиления увепт1чивается за счет введения полокит( льной об-« ратной связи, обеспечиваемой транзисторами 17 и 18. I ил. 10 . (Л со 00 со о м

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1348904 А 1 (51)4 С 11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

СО

4ъ

0. )

<„.»

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4075002/24-24 (22) 09 .06.86 (46) 30,10.87. Бюл, У 40 (71) Московский инженерно-физический институт (72) В.И.Белоусов, 1О.M.Ãåðàcëìoâ, Н,Г,Григорьев, А.Н.Кармаэинский и П.Б.Поплевин (53) 681,327(088,8) (56) IFEE Tournal of Solid-State

Circuits, 1985, чо1. 20, Ф 5, р. 944, fig. 8, Там же, р. 938, fig. 11. (54) УСИЛИТЕЛЬ СЧИТЬБАНИЯ НА КМДПТРАНЗИСТОРАХ (57) Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах, выполненных иэ КМДП-транзисторов, для усиления сигналов считываемой информации. Целью изобретения является повьппение надежности усилителя за счет повьппения его коэффициента усиления. Усилитель считывания содержит два управляющих транзистора 1, ?, четыре переключающих транзистора 3-6 п-типа, два установочных транзистора 7, 8, третий управляющий транзистор 16, нагрузочные транзисторы 19-22 и вновь введенные инвертирующие транзисторы 17, 18 ртипа. Затворы транзисторов 1, 2, 16 и транзисторов 7, 8 объединены и яв-, ляются входом 15 управления режимом работы усилителя, затворы первого 3 и третьего 5, второго 4 и четвертого

6 переключающих транзисторов соответственно объединен» яв.тяются информационными гходамн ll, 12 усилителя, выходами 13 и 14 которого являются сток и исток транзистора 16.

Коэффициент усиления увепичивается эа счет введения положительной обратной связи, обеспечиваем и транзисторами 17 и 18, l ил.

)348904

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах, выполненных иэ КМДП-транзисторов, 5 для усиления сигналов считываемой информации.

Цель изобретения — повышение надежности усилителя за счет унеличения его коэффициента усиления, 10

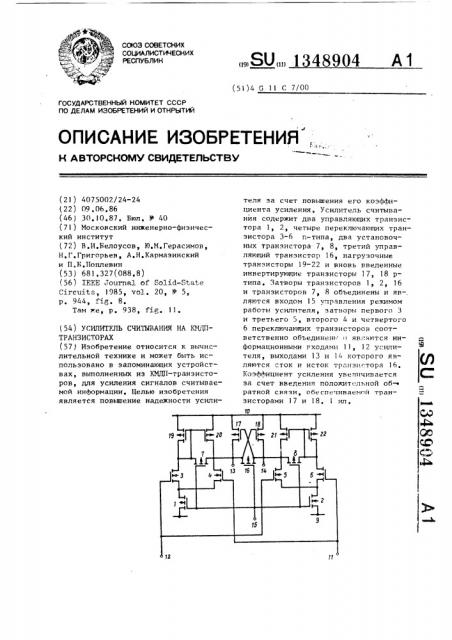

На чертеже приведена принципиальная схема усилителя считывания.

Усилитель считывания содержит первый 1 и второй ? управляющие транзисторы, переключающие транзисторы 3 — 6 с первого по четвертый п-типа, первый 7 и второй Я установочные транзисторы р-типа, шину 9 нулевого потенциала, шину 10 питания. На чертеже обозначены информационные входы 1) 20

12, выходы 13, 14 и вход 15 управления режимом работы усилителя.

Усилитель содержит также третий управляющий транзистор 16, первый 17 и второй 18 инвертирующие транзисторы и нагруэочные транзисторы 19-22 с первого по четвертый р-типа, Усилитель считывания работает следующим образом, В статическом режиме на управляю- 30 щем входе 15 поддерживается напряжение "0", а на входах 11 и 12 — произвольное напряжение от "0" до ")", При этом транзисторы 1 и 2 закрыты, а транзисторы 7 и 8 и транзистор )6 открыты, в результате чего напряжения на выходах 13 и 14 поддерживаются н пределах от 11„„-))„,р, до U„,„, где

Б„„ †. напряжение питания и пороговое напряжение транзистора р-типа.40

В режиме считывания на вход 15 подается напряжение "1", а на входы

11 и 12 — напряжение, соответстнующее считываемой информации. При этом открываются транзисторы 1 и 2 и за- 45 пирается транзистор 16 вследствие чего усилитель оказывается в активном состоянии и начинает переключаться н соответствии с сигналом, поступающим на входы 11 и 12. Например, если напряжение на входе 11 больше, чем на входе 12, то на выходе 13 устанавливается напряжение "0", а на выходе

14 — напряжение "1", Введение положительной обратнои связи с помощью транзисторов 17 и 18 позволяет повысить коэффициент уси— ления усилителя считывания в несколько раэ.

Формула и з о б р е т е н и я

Усилитель считывания на КМДП-транзисторах, содержащий первый и второй управляющие транзисторы и с первого по четвертый переключающий транзисторы п-типа, первый и второй установочные транзисторы, с первого по четвертый нагрузочные транзисторы и третий управляющий транзистор р-типа, причем затноры управляющих и установочных транзисторов объединены и являются входом управления режимом работы усилителя, истоки первого и второго управляющих транзисторов соединены с шиной нулевого потенциала усилителя, сток первого упранляющего транзистора подключен к истокам первого и второго переключающих транзисторов, сток второго управляющего транзистора соединен с истоками третьего и четвертого переключающих транзисторон, сток первого переключающего транзистора подключен к стоку первого нагру.— эочного, затворам первого и второго нагрузочных транзисторон и истоку первого установочного транзистора, сток которого соединен со стоками второго переключающего, второго нагрузочного транзисторов и стоком третьего управляющего транзистора, исток которого подключен к стокам второго установочного, третьего нагрузочного и третьего переключающего транзисторов, затворы третьего и четвертого нагрузочных транзисторов, стоки четвертого нагруэочного и четвертого переключающего транзисторов соединены с истоком второго установочного транзистора, источники нагрузочных транэисторон подключены к шине питания усилителя, затворы первого и третьего переключающих транзисторон объединены и являются первым информационным входом усилителя, затвори второго и четвертого переключающих транзисторон объединены и являются вторым информационным входом усилителя, выходами которого являются сток и исток третьего управляющего транзистора, о т л и ч а ю щ и йс я тем, что, с целью повышения надежности за счет увеличения коэффициента усиления усилителя„ н него введены первый и второй инвертирующие транзисторы, истоки которых соединены с шиной питания усилителя, причем сток первого и затвор второго иннер—

1348904

Составитель Т,Зайцева

Техред М.Ходанич Корректор М.Демчик

Редактор Т.Лазоренко

Заказ 5196/52 Тираж 587 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 тирующих транзисторов подключены к стоку третьего управляющего транзистора, исток которого соединен с затвором первого и стоком второго инвертирующих транзисторов .