Многоканальный программируемый генератор импульсов

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в контрольно-измерительной аппаратуре и. цифровых вычислительных машинах, в частности в устройствах функционального контроля интегральных схем с повышенным уровнем интеграции, в качестве формирователя синхронизирующих импульсов, стробирующих и управляющих сигналов для объектов контроля и амплитудно-временных дискриминаторов. Целью изобретения является расширение функциональных возможностей. Для достижения этой цели в устройство дополнительно введены линия 3 задержки, счетчики 4 и 5, схема сброса 6,блок 7 управления. Устройство также содержит генератор 1 опорной частоты,формирователь 2 периода, каналы 8.1-8.N формирования импульса, каждый из которых состоит из блоков 9 и 10 памяти , коммутаторов 11 и 12, выходного триггера 13. 1 з.п. ф-лы, 5 ил. (Л 00 4 00 со 00 ел Фиъ. 1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (д 4 " 03 K 3/64

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ ф

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3881326/24-21 (22) 08.04.85 (46) 30.10.87. Бюл. М 40 (72) В.В,Козлов, А.И.Панов, Г.В.Клышников и Б.П.Лучин (53) 621.373(088.8) (56) Авторское свидетельство СССР

1029403, кл. Н 03 К 3/64, 1983.

Авторское свидетельство СССР .|| 860295, кл, Н 03 К 3/64, 198 1. (54) ИНОГОКАНАЛЬКЪ|Й ПР ОГРАД||И РУЕМЪ|И

ГЕНЕРАТОР ИМПУЛЬСОВ (57) Изобретение может быть использовано в контрольно-измерительной аппаратуре и цифровых вычислительных машинах, в частности в устройствах функционального контроля ин„„SU„„1348985 A1 тегральных схем с повышенным уровнем интеграции, в качестве формирователя синхронизирующих импульсов, стробирующих и управляющих сигналов для объектов контроля и амплитудно-временных дискриминаторов ° Целью изобретения является расширение функциональных возможностей. Для достижения этой цели в устройство дополнительно введены линия 3 задержки, счетчики 4 и 5, схема сброса 6,блок

7 управления. Устройство также содержит генератор 1 опорной частоты,формирователь 2 периода, каналы 8. 1-8.N формирования импульса, каждый иэ которых состоит иэ блоков 9 и 10 памяти, коммутаторов 11 и 12, выходного триггера 13. 1 з.п. ф-лы, 5 ил.

1348985

Изобретение относится к импульсной технике и может быть использовано в контрольно-измерительной аппар.гтуре и цифровых вычислительных машинах, в частности в устройствах функционального контроля интегральных схем с повышенным уровнем интеграции, в качестве формирователя синхронизирующих, стробирующих и управляющих сигналов для объектов контроля и амплитудно-временных дискриминаторов, Цель изобретения — повышение надежности работы и расширение функциональных возможностей устройства.

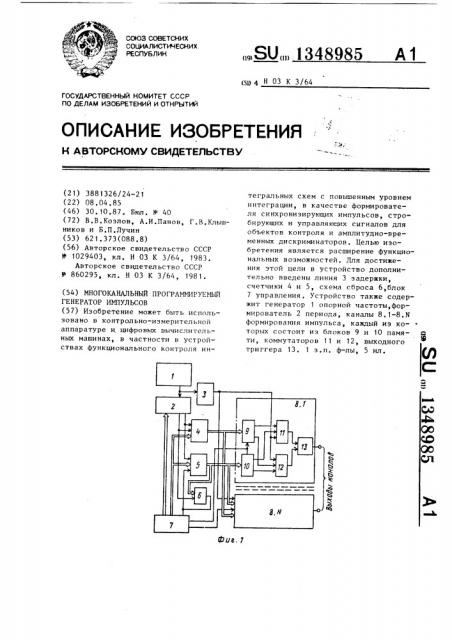

На фиг.1 представлена блок-схема н1ггогокаггальггого программируемого генератор а импульсов; на фиг.2-4 — схемы формирователя периода, устройства сброса и блока управления; на фиг.5 — временные диаграммы работы устройства.

Устройство содержит генератор 1 опорной частоты, формирователь 2 периода, линию 3 задержки, счетчики 4 и 5,схему 6 сброса, блок 7 управления и каналы 8.1-8.N формирования импульса, каждый из которых состоит из блоков 9 и 10 памяти, коммутаторов

11 и 12 и выходного триггера 13.

Выход генератора 1 опорной частоты соединен с тактовым входом формир<>вателя 2 периода и через линию 3 задержки с первыми входами коммутаторов 11 и 12 каналов 8.1-8.V«!>opмирова>гггя импульса. Первый выход формирователя 2 периода соединен со счетными входами счетчиков 4 и 5, второ>! выход — с уста)гоночными входами c ÷I. T шка 4 и схемы 6 сброса, выход котг>рг>й соедггнен с установочггым г>хос ч т >пка 5. 1!нформационные входы формирователя 2 периода подклн>чены к ггерг> г>й группе ггыходс>гз блока 7 управнения, вторая груггпа выходов которого соединена с информационш. ми входами счетчиков 4 и 5. Выходы разрядов счетчика 4 подключены к адресным входам блока 9 памяти каждого из каналов 8.1-8.N формирования импульса,, выходы разрядов счетчика

5 — к разрядггым входам схемы б сброи а Ipl. ñø4ì входам блока 10 памяти каждого канала 8. 1-8. N. Третья групвых II> в бл ока 7 уll 1>пиления по к анально соединена с объединенными в каждом ка нал ь у про вля юшими входами блоков 9 и 10 памяти. Первые выходы

55 блоков 9 и IU памяти соединены соответственно с вторыми и третьими входами коммутатора 11, вторые выходы блоков 9 и 10 памяти — с вторым и третьим входами коммутатора 12, выходы коммутатора 11 и 12 раздельно подключены к входам выходного триггера 13.

Формирователь 2 периода (фиг.2) включает в себя регистр 14, выходы которого поразрядно соединены с входами счетчика 15, выход которого соединен с установочным входом самого счетчика и через инвертор 16 подключен к первому входу элемента И 17, второй вход которого соединен со счетным вход<>м счетчика 15, причем входы регистра 14 являются информационными входами, счетный вход счетчика 15 — тактовым входом, выход элемента И 17 — первым выходом, а выход счетчика 15 — вторым выходом формирователя 2 периода.

Схема 6 сброса (фиг.3) состоит из m-входоггого элемента И 18, первый вход которого подключен к выходу инвертора 19, а выход соединен с первым входом элемента ИЛИ 20, причем (ш — 1) входов элемента И 18 и нход инвертора 19 являются разрядиыми входами, второй вход элемента

И П! 20 установочным входом, а выход элемента Ш11! 20 — выходом схемы 6 сброса.

Блок 7 управления (фиг.4) содержит запоминггншее устройсTво 21, выходы которого соединены с входами буферного регистра 22, дешифратора

23 и входами арифметико-логического устройства (Л 1У) 24, выходы которого подключены к вхходам буферного регистра 25, причем выходы б,ферных регистров 22, 25 и дешифратора 23 являются соответственно первой, второй и третьей груTIIIoII вьгходов блока

7 упра вле ни я .

И>гого канал ьнь>йг программируемый генератор импульсон работает следующим образом.

В исходном состоянии во всех ячейках блоков 9 и 10 памяти каналов

8.1-8.N установлен "0", триггеры 13 сброшены. В соответствии с заданными значениями задержки и длительности выходных импульсов, информация о которых хранится в запоминающем устройстве 21 блока 7 управления, АЛУ осуществляет расчет адресов ячеек з 13489 блоков 9 и 10 памяти каналов 8.1-8.N, в которые должны быть записаны "1".

Расчет осуществляется по следующим формулам:

5 (л

Гт\

А = --- — 2 К

Т

L

° тэ

А = -- - — (2 — 1) К.

Т

Э о л

+ дл Т

А =----- — — 2 ° К;

Т4 л

> à. (2 — 1) К, Т

15 где А, А — адреса первых разрядов в блоках 9 и 10 памяти;

А,, А — адреса вторых разрядов в блоках 9 и 10 памяти; задержка формируемого импульса;

7 „— длительность формируемого импульса;

Т, — период генератора 1 опорной частоты;

m — разрядность счетчиков

4 и 5;

К = О, 1, 2,...

30

Затем из запоминающего устройства 2 1 блока 7 управления через буферный регистр 22 в регистр 14 формиро35 вателя 2 периода переписывается информация о величине периода Т„. Рассчитанные посредством АЛУ 24 адреса !

А,, А., А,, А через буферный регистр

25 блока 7 управления заносится в счетчики 4 и 5. Дешифратор 23 осуществляет выбор каналов 8.1-8.N °

В выбранных каналах в блоки 9 и 10 памяти производится запись "1" в соответствии с адресами, установленными 45 на выходах счетчиков 4 и 5.

По окончании процесса записи информации в блоки 2, 9 и 10 счетчики

4 и 5 устанавливаются в исходное (нулевое) состояние и производится запуск генератора 1 опорной частоты (кнопка Пуск не показана) .

На выходе генератора 1 опорной частоты формируются тактовые импульсы с периодом следования Т. (фиг. 5a) которые поступают на счетчик 15 формирователя 2 периода и линию 3 задержки. На выходе счетчика 15 формирователя 2 периода вырабатываются импульсы с периодом Т„(фиг.56), которые поступают на установочные входы счетчиков 4 и 5 (на счетчик 4 непосредственно, а на счетчик 5 через схему 6 сброса).

Тактовые импульсы с генератора 1 опорной частоты проходят через логический элемент И 17 формирователя 2 периода на счетные входы счетчиков

4 и 5 (фиг.5в). Задержанные посредством линии 3 тактовые импульсы поступают на первые входы коммутаторов

11 и 12 каналов 8.1-8.N, осуществляя стробирование информации, поступающей с выходов блоков 9 и 10 памяти (фиг.5г) . В момент времени t, производится стробирование информации, записанной в ячейках памяти с нулевым адресом.

По приходу тактовых импульсов на счетные входы счетчиков 4 и 5 в момент времени С происходит изменение их состояния,. следовательно, меняются адреса ячеек памяти блоков 9 и 10 соответственно на А и А . Информа1 ция первых разрядов блоков 9 и 10 памяти показана на фиг.5д,е соответственно. В момент времени t осуществляется стробирование совпадающих во времени сигналов "1" с выходов первых каналов блоков 9 и 10 памяти.

При этом на выходе коммутатора 11 формируется импульс (фиг. 5и, момент времени t ), который устанавливает выходной триггер 13 в состояние "1".

На выходе триггера 13 формируется передний фронт импульса с заданной задержкой i (фиг.5л, момент времени

) . Таким образом, формируется задержка импульса.

По прошествии программно заданного количества импульсов счетчики 4

5 и 5 формируют очередные адреса А и

А, поступающие на адресные входы блоков 9 и 10 памяти, и с момента времени t на выходах вторых каналов блоков 9 и 10 памяти устанавливается "1" (фиг.5ж, з).В момент времени t осуществляется стробирование этой информации импульсом, поступающим с выхода линии 3 задержки на коммутатор 12 (фиг.5r), на выходе которого формируется импульс (фиг,5к), поступающий на второй вход триггера

13, Последний сбрасывается, формируя на выходе задний фронт импульса длительностью . (фиг.5л, момент времени t„).

1 348985

Таким образом осуществляется формирование импульсов с заданной задержкой и длительностью в одном из ш каналов, В момент времени t на установоч9 ные входы счетчиков 4 и 5 с выхода счетчика 15 формирователя 2 периода поступает импульс, сбрасываюший счетчики в исходное состояние ° Затем происходит выбор очередного канала, в котором импульс формируется аналогичным образом.

Формула и з обре т е н и я

1. Многоканальный программируемый генератор импульсов, содержащий генератор опорной частоты, выход которого соединен с тактовым входом формирова- 2п теля периода, каналы формирования импульса, отличающийся тем, что, с целью повьш)ения надежности и расширения фнукциональных возможностей, в не с дополнительно вве- 25 цены блок управления, первый и второй

I T èêè, схем» сброса, линия задержки, причем первая группа выходов блока управления соединена с информаци. нными вх дами формирователя периода, первый выход которого подключен к счетным входам первого и второго счетчиков, информационные входы кот. рых поразрядно объединены и подключены к второй группе выходoB блока управления, трет я группа выходов ьLIIороi о цодключ.н» соотвеTcòíåíín к управляющим входам каналов формир вания импульса, первые адресные m)f— ны которых поразрядно объединены и соединены с выходами первого счетчика, установочный вход которого подключен к второму выходу формирователя периода и через схему сброса — к установочному входу второго счетчика, выходы которого соединены с разрядными входами схемы сброса и с вторыми поразрядно объединенными адресными шинами каналов формирования импульса, стробирующие входы которых объединены и соединены с выходом линии задержки, вход которой подключен к выходу генератора опорной частоты, 2. Генератор по п. 1, о т л и ч а ю ш и и с я тем, что каждый иэ каналов формирования импульса содержит первый и второй блоки памяти, первые выходы которых подключены соответственно к первому и второму входам первого коммутатора, выход которого соединен с первым входом триггера, второй вход которого подключен к выходу второго коммутатора, первый и второй входы которого соединены с вторыми выходами соответственно первого и второго блоков памяти, причем объединенные входы управления первого и второго блоков памяти являются управляющим входом канала формирования импульса, адресные входы первого .и второго блоков памяти являются соответственно первыми и вторыми адресными шинами канала формирования импульса, объединенные третьи входы первого и вторпго коммутаторов являются стробируюшим входом, а выход триггера — выходом канала формирования импульса.

1348985 (Юане. г

ФО2, J

0m n íep

/7700а /

Опорной

ЮС/77ОЛЬ

0m cue/77ЧТО 5

0m qmpnuРоА7/77елЯГ

nep//os

0/77 &та 7

ynpudnewua

Е/77(/Ы% ) сАеее сРиса

КС//Е/77 U=

w4,5 е77жюУХ

tf дорпорИааел/о певала

ЖР)77 CNAY /,s5

Ко/7ои.ап У, Ф

/7а/ЧЯ/77О

1348985

Соствитель Б. Кириллов

Техред Л. Олийнык

Корректор Г.Решетник

Редактор Л.Пчолинская

Заказ 5199/56 Тираж 899

В11ИШ1И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул,Проектная,4