Матричный накопитель для запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для использования в цифровых устройствах. Целью изобретения является повьшение степени интеграции матричного накопителя . Для этого в матричный накопитель введены вторая полупроводниковая область р-типа проводимости и вторая полупроводниковая шина p -типа проводимости , расположенная на второй полупроводниковой области и участке первого слоя дизлектрика, примыкающего к краю канавки. Участки второй полупроводниковой шицы, расположенные на второй полупроводниковой области5,. диффузионная область, каждая металггшческая шина и полупроводниковая подложка образуют соответственно исток, первый и второй затворы и сток второго ключевого МДП-транзистора ячейки памяти матричного накопителя, а втр рая диффузионная шина образует шину считывания матричного накопителя. : 4 ил. ,- 1

СО(ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (5D 4 G 11 С 11/40

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4072847/24-24 (22) 02.06.86 (46) 23.12.87, Бюл. Р 47 (71) Московский авиационный институт им. Серго Орджоникидзе (72) Н.А. Аваев (53) 681.327.66(088.8) (56) Чен.Д. Динамическое ЗУПВ емкостью 64 К с большими запасами работоспособности. — Электроника, 1981, Ф 8, с. 62-69.

IEEE Trans., 1979, v. ED-269 р. 839-852. (54) МАТРИЧНЬИ НАКОПИТЕЛЬ ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА (57) Изобретение относится к вычислительной технике и предназначено для использования в цифровых устройствах.

Целью изобретения является повышение степени интеграции матричного накопителя. Для этого в матричный накопитель введены вторая полупроводниковая область р-типа проводимости и вторая полупроводниковая шина р - типа проводимости, расположенная на второй полупроводниковой области и участке первого слоя диэлектрика, примыкающего к краю канавки. Участки второй полупроводниковой шины, расположенные на второй полупроводниковой области, диффузионная область, каждая металлическая шина и полупроводниковая подложка образуют соответственно исток, первый и второй затворы и сток второго ключевого МДП-транзистора ячейки памяти матричного накопителя, а вто- ® рая диффузионная шина образует шину считывания матричного накопителя, 4 ил. (::

136162

Изобретение относится к вычислительной технике и может быть использовано, в частности, при построении оперативных запоминающих устройств.

Цель изобретения — повышение степени интеграции.

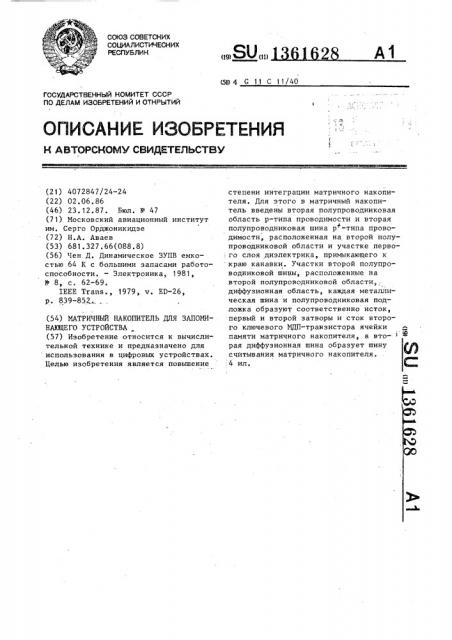

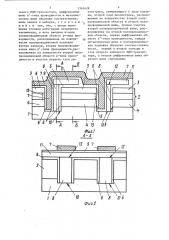

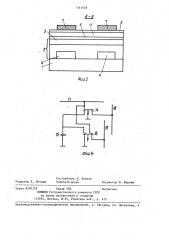

На фиг. 1 показана структура матричного накопителя в направлении строки, поперечный разрез; на фиг.2 — 10 разрез Л-А на фиг. 1; на фиг. 3— разрез Б-Б на фиг.1; на фиг.4 — эквивалентная схема запоминающего элемента матричного накопителя.

Матричный накопитель содержит полупроводниковую подложку 1 р -типа эпитаксиальный слой 2 р-типа проводимости, первые диффузионные шины 3 и --типа, первые диффузионные области

4 п -типа, канавки с боковыми поверх- 20 ностями 5, первый слой 6 диэлектрика, металлические шины 7, вторую полупроводниковую область 8 р-тиЛа, второй слой 9 диэлектрика, контакт 10 второй полупроводниковой области 8 с полу- 25 проводниковой подложкой 1, вторые полупроводниковые шины .11 р -типа,контакт 12 второй полупроводниковой области 8 с второй полупроводниковой шиной 11, канал 13 первого ключевого др

МДП-транзистора 14, запоминающий конденсатор 15, второй ключевой МДПтранзистор 16, шину 17 выборки, шину

18 записи и шину 19 считывания.

Накопитель работает следующим образом.

Подложка 1 соединяется с нулевой шиной, Информация в запоминающем элементе хранится в виде напряжения на запоминающем конденсаторе, образован- 40 ном емкостью р -и -nepexcpa между подложкой 1 и областью 4 n+ — типа. В режиме хранения напряжения на шинах

17-19 равны нулю и оба транзистора 14 и 16 закрыты. Конденсатор 15 отключен 45 от шин и хранит информацию: низкий (нулевой) уровень напряжения U соответствует логическому нулю, а высокий ,11

U — логической единице. Двухзатворный транзистор 16 закрыт при сквозном 50

° обеднении носителями слоя.

При считывании на шины 18 записи подают нулевое напряжение, на шинах

19 считывания предварительно устанавливают напряжение U, которое по . окончании импульса установки поддер,живается емкостью шины. После этого подают отрицательный импульс амплитудой Uq „на шину 17 выборки, .Тран8 2 зистор. 16 отпирается в случае храйения логического нуля, и напряжение на шине 19 понижается. В случае хранения логической единицы транзистор

16 остается закрытым, а напряжение на шине 19 не изменяется.

В накопителе считывание является неразрушающим, так как при считывании запоминающий конденсатор не связан с шиной столбца и напряжение на нем сохраняется.

Предлагаемый накопитель позволяет достигнуть большой степени интеграции, так как площадь, приходящаяся на один. запоминающий элемент, ограничивается разрешающей способностью фотолитографии, а сигнал считывания не зависит от емкости запоминающего конденсатора.

Формула и з обретения

Матричный накопитель для запоминающего устройства, содержащий полупроводниковую подложку р -типа проводимости, диффузионные области и -типа

1 проводимости, расположенные в приповерхностной области полупроводниковой подложки, эпитаксиальный слой р-типа проводимости, расположенный на поверхности полупроводниковой подложки, диффузионные шины п -типа проводимости, расположенные в приповерхностной области эпитаксиального слоя над диффузионными областями п — типа проводимости, канавки, выполненные в эпитаксиальном слое и приповерхностной области полупроводниковой подложки, боковые стенки канавки,соприкасающиеся с диффузионными шинами и областями n+ -типа проводимости, первый слой диэлектрика, расположенный на поверхностях эпитаксиального слоя и канавки, металлические шины, расположенные на поверхности первого слоя диэлектрика, причем полупроводниковая подложка и диффузион-. ные области n+-типа проводимости образуют соответственно первый и второй электроды запоминающих конденсаторов, диффузионные области и -типа ф проводимости, участок диффузионной шины, расположенный над диффузионной областью и -типа проводимости, и

4 участок металлической шины, расположенный внутри канавки, образуют соответственно сток, исток и затвор клюз 1361628

4 чевого МДП-транзистора, диффузионные электрика, примыкающего к краю канавшины и -типа проводимости и металли- ки, второй Слой диэлектрика, располоческие шины образуют соответственно женный на поверхностях второй полушины записи и выборки, о т л и ч а ю — проводниковой области и второй полу5 шийся тем, что, с целью повы- проводниковой шины, причем участки шения степени интеграции матричного второй полупроводниковой шины, раснакопителя, в него введены вторая положенные на второй полупроводникополупроводниковая область р-типа про- вой области, первая диффузионная обводимости, расположенная на поверх- 1О ласть и"-типа проводимости, каждая ности полупроводниковой подложки металлическая шина и полупроводниковнутри канавки, вторая полупроводни- вая подложка образуют соответственно ковая шина р -типа проводимости,рас- исток, первый и второй затворы и положенная на поверхности второй полу- сток второго ключевого МДП-транзиспроводниковой области р-типа прово- 15 тора, а вторая диффузионная шина обдимости и участке первого слоя ди- разует шину считывания.

1 8

Фиг.2

1361628

Составитель В. Венков

Техред M.ÄHäûê

Редактор В. Петраш

Корректор М. Шароши

Заказ 6297/52 Тираж 588

ВНИИПИ Государственного комитета СССР

-по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4