Одноразрядный сумматор-вычитатель

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств ЭВМ и спецпроцессоров. Цель изобретения - расширение функциональных возможностей за счет реализации дополнительных операций сложения и вычитания обратных кодон двоичных чисел . Одноразрядный сумматор-вычитатель содерзкит семь элементов РАВНОЗНАЧНОСТЬ 1-7, входы 8 и 9 первого и второго операндов соответствующих разрядов,вход 10 переноса-заема, входы 11-13 настройки,выход 14 суммы, выход 15 переноса-заема. 1 ил., 1 табл. сл

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (51) 4 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ (21) 4077500/24-24 (22) 08.05.86 (46) 23.01.88. Бюл. У 3 (72) Л.Б.Авгуль, В.А.Мищенко, С.М.Терешко, С.:I.ôåä÷åíêî и М.M.Татур (53) 681.385.5(088.8) (56) Лысинков Б.Г.Арифметические и логические основы цифровых автоматов ° — Минск: Высшая школа, 1980, с. 279, р. 74.

Авторское свидетельство СССР

)(- 1251070, кл. G 06 F 7/50, 1985. (54) ОДНОРАЗРЯДНЫЙ СУММАТОР-ВЬИИТАТЕЛЬ (57) Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств

ЭВМ и спецпроцессоров. Цель изобретения — расширение функциональных возможностей за счет реализации дополнительных операций сложения и вычитания обратных кодов двоичных чисел. Одноразрядный сумматор-вычитатель содержит семь элементов РАВНОЗНАЧНОСТЬ 1-7, входы 8 и 9 первого и второго операндов соответствующих разрядов, вход 10 переноса-заема, входы 11 — !3 настройки, выход 14 суммы, выход 15 переноса-заема.

1 ил., 1 табл.

8875

10

20

1 136

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения арифметико-логических устройств ЭВИ и спецпроцессоров.

Цель изобретения †расширение функциональных возможностей за счет реализации операцийсложения и вычитания над о ратнымикодами двоичныхчисел.

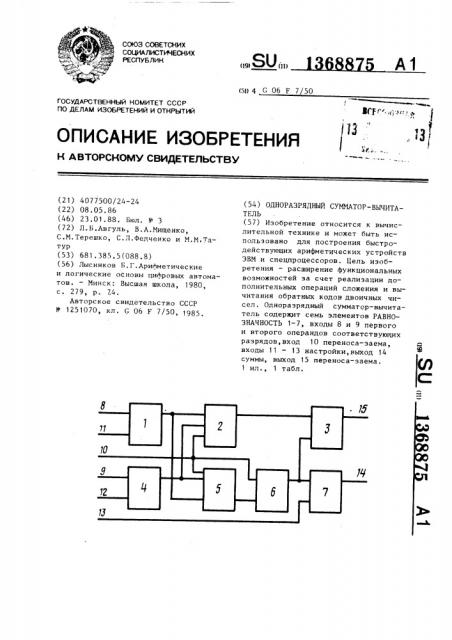

На чертеже представлена схема предлагаемого одноразрядного сумматора-вычитателя.

Одноразрядный сумматор-вычитатель содержит элементы РАВНОЗНАЧНОСТЬ 1 в 7, вход 8 i-ro разряда первого операнда, вход 9 i-го разряда второго операнда, вход 10 переносазаема из (i — 1)-го разряда, входы

11 — 13 настройки, выход 14 суммыразности i-го двоичного разряда, выход 15 переноса-заема в (i+1)-й разряд.

Устройство работает следующим образом.

На вход 8 подается прямой код i-ro разряда первого операнда х,, на на вход 9 — прямой код i ro разряда второго операнда у;, на вход 10 сигнал переноса-заема из (i-1)-го разряда р,.,, на входы 11...13 сигналы настройки U,... U соответственно. На выходе 14 реализуется логическая функция, соответствующая значению суммы-разрядности в

i-м двоичном разряде, на выходе 15 логическая функция, соответствующая сигналу переноса-заема в (i+1)-й разряд.

Коды настроек на выполнение восьми арифметических операций приведены в таблице..

Достоинством предлагаемого устройства являются широкие функциональные возможности, простая конструкция, однородная структура и высокое быстродействие.

2 ор мула из обре тения

Одноразрядный сумматор-вычитатель, содержащий элементы РАВНОЗНАЧНОСТЬ, причем вход i-ro разряда первого операнда сумматора-вычитателя, i=

1, и, п-разрядность операндов соединен с первым входом первого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с первым настроечным входом сумматора-вычитателя, а выход соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ и первым входом третьего элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом четвертого элемента РАВНОЗНАЧНОСТЬ,а второй вход соединен с входом переноса-заема из (i-1)-го разряда сумматора-вычитателя и вторым входом второго элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом пятого элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с выходом переноса-заема в (i+1) и разряд сумматора-вычитателя, о т л и ч а ю щ и йс я тем,что,с целью расширения функциональных возможностей за счет реализации операций сложения и вычитания над обратными кодами двоичных чисел, вход i.-ro разряда второго операнда соединен с певрым вхбдом шестого элемента РАВНОЗНАЧНОСТЬ, второи вход которого соединен с вторым настроечным входом сумматора-вычитателя, а выход соединен с третьим входом второго элемента РАВНОЗНАЧНОСТЬ и вторым входом четвертого элемента

РАВНОЗНАЧНОСТЬ, выход которого соединен с вторым входом пятого элемента РАВНОЗНАЧНОСТЬ и первым входом седьмого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с третьим настроечным входом сумматора-вычитателя, а выход соединен с выходом суммы-разности i-го разряда сумматора-вычитателя.

1368875

Операция

11 11, 12/U 13/0з

15

X+Y р;, ) 150 (х 1 э 7(е Ус р;, ) 0

X+Y р;, ) р, ) 0

f (х;, У, з

X+Y

f (х,, v р,, ) 0

0 щ (x, У; Р;, р, ) Г<, (х;, v

Х-Y

Х-Y р;, ) (х,, у;, P„ =, ) 0

Х-Y

Х-7

Составитель М.Есенина

Техред М.Ходанич

Корректор В.Гирняк

Редактор Е.Папп

Подписное

Заказ д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород,, ул. Проектная, 4

Сигналы настройки

297/51 Тираж 704

В11ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, f >(x;, v;, р, )

f7(х,, ч;, р )