Полупроводниковый стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике , в частности к устройствам питания электронных приборов. Пель изобретения - повышение надежности и расширение функциональных возможностей . Устройство содержит первый транзистор (т) 3, второй (Т) 4, первый резистор (Р) 5, блок управления г (БУ) 6, второй (Р) 7, третий (Р) 8, стабилитрон (С) 9, конденсатор (К) 10 и третий (Т) 11. В момент подключения источника питания к схеме устройства происходит заряд К 10 и на (Р) 7 появляется потенциал, достаточный для отпирания Т 11. По цепи Р 5-Т 11 напряжение с входа поступает на выход. При этом ВУ 6 формирует выходные сигналы, по которым открываются Т 4 и Т 3. После заряда К 10 и Т 11 закрывается и питание нагрузки и БУ 6 осуществляется через открытый Т 3. В случае к.з. или перегрузки напряжение на БУ 6 уменьшается и с его выходов поступают сигналы, запирающие Т 4 и Т 3. Для исключения случаев деблокировки схемы при кратковременных повьш1ениях напряжения на выходе источника питания в схему введены С 9 и третий Р 8. При повышениях напряжения С 9 открывается и через Р 7 и К 10 ток практически не протекает. 1 ил. с в (/)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

„Л0„„1 72 06 (511 4 G 05 F 1/569

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АSTOPCHOMV СВИДЕТЕЛЬСТВУ й; "Ф1> . л 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4061921/24-07 (22) 30.04.86 (46) 07,02.88, Бюл. У 5 (71) Научно-исследовательский и проектный институт городского пассажирского транспорта г. Москвы (72) Н,В. Кобозев и Г.А. Плуцис (53) 621.316.722.1(088.8) (56) Авторское свидетельство СССР

N 702367, кл. С 05 F 1/569, 1977.

Авторское свидетельство СССР

У 490788, кл, G 05 F 1/569, 1974. (54) IIOJIYIIPOBOQHHKOBbN СТАБИЛИЗАТОР

ПОСТОЯННОГО НАПРЯЖЕНИЯ (57) Изобретение относится к электротехнике, в частности к устройствам питания электронных приборов. Цель изобретения — повышение надежности и расширение функциональных возможностей. Устройство содержит первый транзистор (T) 3, второй (Т) 4, первый резистор (Р) 5, блок управления

S (БУ) 6, второй (P) 7, третий (p) 8, стабилитрон (С) 9, конденсатор (К) 10 и третий (Т) 11 ° В момент подключения источника питания к схеме устройства происходит заряд К 10 и на (Р) 7 появляется потенциал, достаточный для отпирания Т 11 ° По цепи P 5-Т 11 напряжение с входа поступает на выход, При этом БУ 6 формирует выходные сигналы, по которым открываются Т 4 и Т 3. После заряда К 10 и Т 11 закрывается и питание нагрузки и bY 6 осуществляется через открытый Т 3. В случае к.s. или перегрузки напряжение на БУ 6 уменьшается и с его выходов поступают сигналы, запирающие Т 4 и Т 3.

Для исключения случаев деблокировки схемы при кратковременных повьппениях напряжения на выходе источника питания в схему введены С 9 и третий Р 8. При повышениях напряжения

С 9 открывается и через P 7 и К 10 ток практически не протекает. 1 ил.

13 72:306

Изобрете»»ие относит< я к 1лектротехнике, в частности к устройствам питания электронных приборов.

Цель изобретения — повышение на5 деж>»о. Г»» и расширение функциональных возможностей стабилизатора °

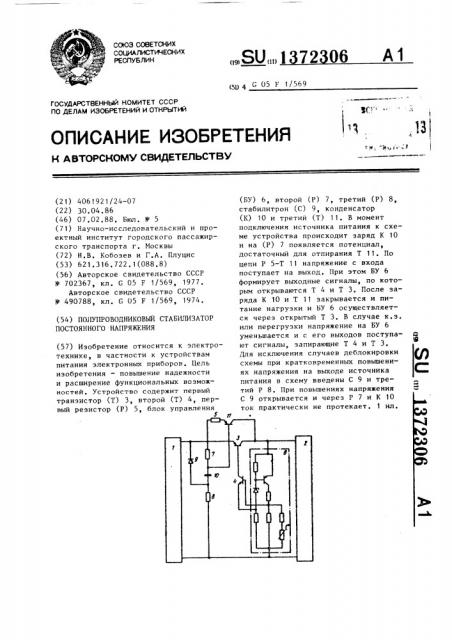

На чертеже представлена принципиальная схема предлагаемого стабилизатора. 10

На чертеже представлена принципиальная схема предлагаемого стабили45 ее «ихо;»оп поступают «игналы, запирающие .гранзистори 4 и 3, После этого схема блокируется и ее запуск

BoBbIÎ>»» по<) Iе по»»тор но1 О подключе

Н11Н H<" TO I III»F< B 1 1»итания, 55

Длн тогo, «тоби 11«кл»очить случай пеб>покиронки < ?; ми при кратконременних повьппениях напг>нж<. »и, на Bb»xo затора.

Стабилизатор содержит источник 1 питания и нагрузку 2, первый тран- 15 зистор 3, включенный последовательно в силовую »пину, второй транзистор 4, коллектор которого подключен к базе транзистора 3, первый резистор 5, один вывод которого подключен к эмит- 2р теру транзистора 3, блок 6 управления, второй 7 и третий 8 резисторы, стабичитрон 9, включенный между

s HTTepos транзистора 3 и резистора

8. к которому подключена одна обклад- 25 ка,, >нденсатора 10, другая с бкладка которого подключена к резистору 7, тре гий транзистор 11, включенный между резистором 5 и коллектором транзистора 3.

П<)<»упроводниковьп» стабилизатор пост<я»11»ого 1»апряжения работает следующим образом, 8 .омент подключения источника 1 питания к схеме стабилизатора проис35 ходит арнд конденсатора 10 и на резист< ре 7 появляется потенциал, до«тат; »ный для отпирания транзистора I1. tIO цепи резистор 5 — транзистор 11 < - вх<)да стабилизатора постУ 40 пает нг» его 1»иход. Нри этом схема 6 управления формир,ет выходные сигналы, птся транзистор11 4 11 3. 11<><:IF заряда конденсатора 10 гра.»-,и«т<>р 11 закрывается и пи г:<нис нагруз»<и 2 и exp)1<1 6 управJ1c .с»1»н < )сущ<зс Гнлнетc»» через QTKpblTb»H транзистор 3.

Е«ли 1»рои«х<)дит короткое замыка11Не 11>11» и<. регру»ка, напряжение на схе »е 6 управления уменьшается и с де источника 1 питания в схему стабилизатора введены стабилитрон 9 и третий резистор 8. При повышениях напряжения стабилитрон 9 открывается и через резистор 7 и конденсатор 10 ток практически не протекает, Таким образом, на базе транзистора

11 при повышенных напряжениях не возникает отпирающего потенциала.

Использование новых элементов третьего транзистора, стабилитрона, второго и третьего резисторов, конденсатора отличает предлагаемый стабилизатор постоянного напряжения от известного так как при коротком замыкании на выходах стабилизатора схема блокируется, на выходе стабилизатора полностью исчезает напряжение, что устраняет возможность развития неисправностей в питающейся от стабилизатора аппаратуре, Формула изобретения

Полупроводниковый стабилизатор постоянного напряжения, содержащий первый транзистор, включенный последовательно в силовую шину, эмиттер которого подключен к входному выводу, а коллектор — к вьгходному выводу, второй транзистор, коллектор которого подключен к базе первого транзистора, первый резистор, один вывод которого соединен с эмиттером первого транзистора, блок управления вторым транзистором, входы которого соединены с коллектором первого транзистора и общей шиной, а выходы соединены с базой и эмиттером второго транзистора, о т л и ч а ю щ и и с я тем, что, с целью повышения надежности и расширения функциональных возможностей, в него введены третий транзистор, второй и третий резисторы, стабилитрон и конденсатор, причем эмиттер третьего транзистора соединен с другим выходом первого резистора, а его коллектор соединен с коллектором первого транзистора, к эмиттеру которого подключен катод стабилитрона и первый вывод второго резистора, второй вы- вод второго резистора и одна из обкладок конденсатора с базой третьего транзистора, а анод и другая обкладка конденсатора соединены с одним из выводов третьего резистора, другой вывод которого соединен с обшеи шинои.