Четырехвходовый одноразрядный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и предназначено для построения многооперандных быстродействующих арифметических устройств . Цель изобретения - упрощение сумматора. В состав устройства входят три элемента сложения по модулю два 1,2,3, два элемента И 4,5, один элемент РАВНОЗНАЧНОСТЬ 7, один элемент НЕ 6, четьфе входа 8-11, выход 12 суммы и два выхода 13, 14 переноса. При подаче на информационные входы двоичных сигналов на выходе устройства реализуются логические функции, соответствующие сигналам суммы и переноса в старшие разряды. 1 ил., 1 табл.

4216 А1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (51)4 G 06 F 7 50

I 4.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4098636/24-24 (22) 30.07.86 (46) 15.02.88. Бюл. У 6 (72) Л.Б.Авгуль, Ю.И.Дубовик, В.П.Супрун и В.П.Якуш (53) 681.325.5(088.8) (56) Авторское свидетельство СССР

У 450160, кл. G 06 F 7/50, 1972.

Логическое проектирование.БИС/

/Под ред. В.А.Мищенко. М.: Радио и связь, 1984, с.55-56, рис.4.3. (54) ЧЕТЫРЕХВХОДОВЫЙ ОДНОРАЗРЯДНЫЙ

СУММАТОР (57) Изобретение относится к области вычислительной техники и предназначено для построения многооперандных быстродействующих арифметических устройств. Цель изобретения — упрощение сумматора. В состав устройства входят три элемента сложения по модулю два

1,2 3 два элемента И 4,5, один элемент РАВНОЗНАЧНОСТЬ 7, один элемент

НЕ 6, четыре входа 8-11, выход 12 суммы и два выхода 13, 14 переноса.

При подаче на информационные входы двоичных сигналов на выходе устройства реализуются логические функции, соответствующие сигналам суммы и переноса в старшие разряды. 1 ил., 1 табл. г

Пр одолже ние та бли цы

1 13742

Изобретение относится к вычислительной технике.и предназначено для построения многооперандных быстродействующих арифметических устройств.

Цель .изобретения — упрощение четырехвходового одноразрядного сумматора.

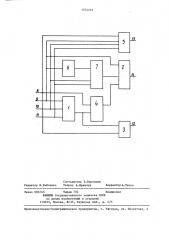

На чертеже представлена функциональная схема четырехвходового одноразрядного сумматора.

Сумматор содержит элементы 1-3 сложения по модулю два, элементы И 4, 5, элемент НЕ 6, элемент РАВНОЗНАЧНОСТЬ 7, входы 8 — 11, выход 12 сум- 15 мы, выходы 13 и 14 старшего и младшего переносов.

Сумматор работает следующим образом.

На входы 8 — 11 подаются двоичные 20 переменные х...,.,х . На выходе 12 реализуется логическая функция

S — х + х + х + х соответствующая сигналу суммы, на выходе 13 — логическая функция 25

Р„=х,ххх соответствующая сигналу старшего переноса; на выходе 14 - логическая функция

P,=õ, (+) R(x„x „x„X+3(x, (х,®х ® 30

Q х,)), соответствующая сигналу младшего переноса.

Здесь R(x х,х, )=х,х х и х х,х функция Равнозначности. 35

Значения указанных логических функций представлены в таблице.

1 0 1 1 1

1 1 0 0 0

1 1 0, 1 1

1 1 1 О 1

1. 1 1 1 0

О 1

О 1

О 1

О 1

1 0

Четырехвходовый одноразрядный сумматор, содержащий первый и второй элементы И, элемент НЕ, первый элемент сложения по модулю два, первый, второй, третий и четвертый входы первого элемента И соединены соответственно с первым, вторым, третьим и четвертым входами сумматора, а выход соединен с выходом старшего переноса сумматора, первый вход сумматора соединен с первым входом второго элемента И, а второй, третий и четвертый входы сумматора соединены соответственно с первым, вторым и третьим входами первого элемента сложения по модулю два, второй вход сумматора подключен к входу элемента НЕ, о т— . л и ч а ю шийся . тем, что, с целью упрощения, сумматор содержит второй и третий элементы сложения по модулю два и элемент РАВНОЗНАЧНОСТЬ, входы которого подключены к выходу элемента НЕ и третьему и четвертому входам сумматора, цходы второго элемента сложения по модулю два соединены с выходами элемента РАВНОЗНАЧНОСТЬ второго элемента И и вторым входом сумматора, а выход соединен с выходом младшего переноса сумматора, первый вход которого подключен к первому входу третьего элемента сложения по модулю два, второй вход которого соединен с выходом первого элемента сложения по модулю два и вторым входом второго элемента И, а выход — с выходом суммы сумматора.

0 0

О О 45

0 0

0 1

0 О

О 1

О 0 О 0 0

О О 0 1 1

0 О 1 О 1

0 0 1 1 0

О 0 1

0 1

0 1 О 1 0

0 -1

0 1

0 1 1 1 1

1 О 0 0 1

1 0 О 0 1 0 0

1 4 5 б 7

1 О 0 1 О 0 1

1 О 1 0 0 0 1

Формула изобретения

1374216

Составитель В.Березкин

Техред А.Кравчук Корректор А.Тяско

Редактор И.Рыбченко

Заказ 603/45 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4