Усилитель считывания на кмдп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на КМДП-транзисторах. Цель изобретения - повышение надежности усилителя считывания. Поставленная цель осуществляется за счет введения инверти944 , - слильтееля щеирующих транзисторов, образующих положительную обратную связь, увеличивающую коэффициент усиления, а также приводящую к запиранию одного из инвертирующих транзисторов, за счет чего исключается протекание тока через соответствующий дифференциальный каскад усилителя, следовательно, уменьшаются потребляемая мощность и уровень логического нуля усилителя. Устройство содержит дифференциальные каскады 1, 2, каждый из которых состоит из транзисторов 3, 4, 5 первого типа проводимости - управляющего, первого и второгЬ переключающих элементов , транзисторов 6,7,8 второго типа проводимостей - установочного, первого и второго нагрузочных элементов , ключевые элементы 14, 20 на транзисторах второго типа проводимости , четыре инвертирующих элемента 16 - 19 на транзисторах второго типа проводимости, 1 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (59 4 С 11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н Д BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТЬЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4122171/24-24 (22) 17.09.86 (46) 29.02.88, Бюл. Ф 8 (72) В.В.Баранов, В.И.Белоусов, Ю.M.Ãåðacèìoâ, Н.Г.Григорьев, А.Н.Кармазинский, П.Б.Поплевин и С.A.Òðoøèí (53) 681.327.66(088,8) (56) Патент Англии Р 2100542, кл. Н 03 К 5/02, 1982.

IEEE Journal of Solid-State

Circuits, 1985, vol. 20, Р 5, р. 944, fig, 8. (54) УСИ31ИТЕЛЬ СЧИТЫВАНИЯ НА КМДПТРАНЗИСТОРАХ (57) Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на КМДП-транзисторах. Цель изобретения — повышение надежности усилителя считывания. Поставленная цель осуществляется за счет введения инверти„.SU»1377 А1 рующих транзисторов, образующих положительную обратную связь, увеличивающую коэффициент усиления, а также приводящую к запиранию одного из инвертирующих транзисторов, за счет чего исключается протекание тока через соответствующий дифференциальный каскад усилителя, следовательно, уменьшаются потребляемая мощность и уровень логического нуля усилителя.

Устройство содержит дифференциальные каскады 1, 2, каждый из которых сос-. тоит из транзисторов 3, 4, 5 первого типа проводимости — управляющего, первого и второго переключающих элементов, транзисторов 6,7,8 второго типа проводимостей — установочного, В первого и второго нагрузочных элементов, ключевые элементы 14, 20 на транзисторах второго типа проводимости, четыре инвертирующих элемента

16 — 19 на транзисторах второго типа проводимости. 1 ил.

1377910

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на

КМПП-транзисторах для усиления сигна5 лов считываемой информации.

Целью изобретения является повышение надежности усилителя считывания.

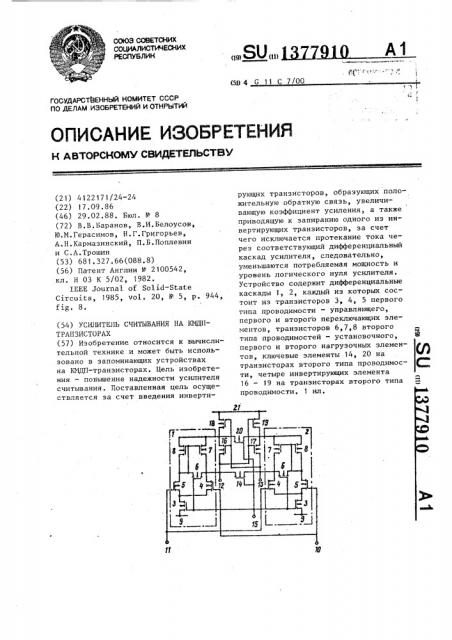

На чертеже представлена схема усилителя считывания, 10

Устройство содержит первый 1 и второй 2 дифференциальные каскады, каждый из которых состоит из транзисторов 3 — 5 первого типа проводимости — управляющего, первого и второго переключающих элементов, транзисторов 6 — 8 второго типа проводимости — установочного, первого и второго нагрузочных элементов, шину 9 нулевого потенциала, первый 10 и вто- 20 рой 11 информационные входы, первый

12 и второй 13 информационные выходы, первый ключевой элемент 14 на транзисторе второго типа проводимости, управляющий вход 15, первый — четвер- 25 тый инвертирующие и второй ключевой элементы на транзисторах 16 — 20 второго типа проводимости, шину 21 питания.

Принцип действия усилителя считывания заключается в следующем.

В статическом режиме на входе 15 поддерживается напряжение "0", а на входах 10 и 11 — напряжения, соответствующие произвольной информации. При этом транзисторы 3 закрыты, а транзисторы 6, 14, 20 открыты, в результате чего на выходах 12 и 13 и истоках транзисторов 7 и 8 каскадов 1, 2 установлены одинаковые напряжения, лежащие в диапазоне От Н -Un„ðð до ип питания и пороговое напряжение транзисторов второго типа проводимости..

В активном режиме, т.е. в режиме

45 считывания информации, на вход 15 подается напряжение "1", а на входы 10 и ii — напряжения, соответствующие считываемой информации. Пусть для определенности U „ — напряжение на входе l0, à U „— напряжение на

50 входе 11 и U „> U . Тогда после пе " т ВХ2 реключения усилителя на выходе усилителя l2 устанавливается низкий уровень напряжения U,,а на. выходе 13 высокий уровень напряжения U . При55 чем размеры транзисторов в схеме выбираются такими, что обеспечивается условие U )U» П„рр . В результате

К-Д 1 ййл Кх -)t) 1и k 1+ 1

11, (2 + .МШ 2 ) (1.1. ) НЕГР

P и И вЂ” ширина каналов иив2 транзисторов

16 — 19 соответгде W иив1 ственно;

M — ширина канала иагр транзисторов 7 и 8; и — коэффициенты

Р

ВЛИЯНИЯ ПОДЛОЖКИ транзисторов первого и второго типа проводимости;

K — коэффициент усив ления прототипа; и k — удельные крутизtl р ны транзисторов

3 4 и 7е8ю что при К =15; Ии„ i/W „,ð =0 05;

0,5 — 1,0 составляет К=5,0-5,5.

1Io сравнению с прототипом предлагаемый усилитель обладает в 5,05,5 раза более высоким коэффициентом транзисторы 16, 18 после переключения усилителя оказываются закрытыми, т.е. исключается протекание тока через каскад 1. Поскольку транзисторы 3 — 5 каскада 1 открыты по затвору, то напряжение на выходе l2 оказывается равным напряжению шины 9, т,е °

U =О. В прототипе ток после перекпючения усилителя протекает через оба каскада, т.е. через усилитель протекает вдвое больший ток, а уровень "0" при малом входном. сигнале (U ах 1

« U ) определяется формулой

Вх2 ип

"О вх Ппav п

U = — — — -" ——

1+1„ где U — пороговое напряжение вОРп транзисторов первого типа проводимости; — коэффициент влияния подложки этих транзисторов, что при U =4-5 В и U =1 В и 1

Вх1 flop u и

=l 0 составляет значительную величи1 о ну, равную U =1,5-2,0 В.

Транзисторы 16 — 19 включены по схеме с положительной обратной связью, что приводит к увеличению коэффициента усиления по сравнению с прототипом в К раз, где U -U c< U

ef 1 Вк2

1377910

Составитель А.Ершова

Редактор Н.Слободяник Техред М.Ходанич КорректорМ.Шароши

Заказ 879/48 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, r.Óæãoðîä, ул.Проектная, 4 усиления, вдвое меньшей потребляемой мощностью и минимально возможным (нулевым) уровнем "0". формула изобретения

Усилитель считывания на КМДП-транзисторах, содержащий ключевой элемент на транзисторе, первый и второй дифференциальные каскады усиления, каждый из которых состоит из первого и второго переключающих и управляющего элементов на транзисторах первого типа проводимости, первого и второго нагрузочных и установочного элементов на транзисторах второго типа проводимости, истоки транзисторов нагрузочных элементов каждого дифференциального каскада объединены, стоки первых нагрузочных элементов на тран- 2 зисторах первого и второго дифференциальных каскадов подключены соответственно к истоку и стоку транзистора ключевого элемента и являются соответственно первым и вторым информационными выходами усилителя считывания, затворы транзисторов нагрузочных элементов каждого дифференциального каскада объединены со стоками транзисторов вторых нагрузочного и

1 переключающего элементов каждого дифференциального каскада и подключены к стоку транзистора установочного элемента каждого дифференциального каскада, исток которого подключен к стоку транзистора первого нагрузочного и истоку транзистора первого переключающего элементов каждого дифференциального каскада, сток первого и исток второго транзисторов переключающих элементов каждого дифференциального каскада подключены к стоку транзистора управляющего элемента каждого дифференциального каскада, исток которого подключен к шине н,левого потенциала усилителя считывания, затворы транзисторов установочных и управляющих элементов обоих дифференциальных каскадов объединены с затвором транзистора ключевого элемента и являются управляющим входом усилителя считывания, затвор транзистора второго переключающего элемента второго дифференциального каскада соединен с затвором транзистора первого переключающего элемента первого дифференциального каскада и является первым информационным входом усилителя считывания, затвор транзистора второго переключающего элемента первого дифференциального каскада соединен с затвором транзистора первого

I переключающего элемента второго дифференциального каскада и является вторым информационным входом усилителя считывания, о т л и ч а ю щ и и с я тем, что, с целью повышения надежности усилителя считывания, в него введены первый, второй, третий, четвертый инвертирующие и второй ключевой элементы на транзисторах второго типа проводимости, истоки третьего и четвертого транзисторов инвертирующих элементов объединены и под-, ключены к шине. питания усилителя считывания, затвора первого и третьего и сток второго транзисторов инвертирующих элементов подключены к второму информационному выходу усилителя считывания, затворы второго, четвертого и сток первого транзисторов инвертирующих элементов подключены к первому информационному выходу усилителя считывания, исток первого и сток третьего транзисторов инвертирующих элементов подключены к истоку первого транзистора нагрузочного элемента первого дифференциального каскада и истоку второго транзистора ключевого элемента, сток которого подключен к истоку второго и стоку четвертого транзисторов инвертирующих элементов и истоку транзистора первого нагрузочного элемента второго дифференциального каскада, затворы первого и второго транзисторов ключевых элементов объединены.