Мажоритарный элемент

Иллюстрации

Показать всеРеферат

Изобретение относится к комбинационным логическим схемам на биполярных транзисторах. Цель изобретения - повьппение быстродействия и снижение потребляемой мощности. Электрическая схема мажоритарного элемента построена на биполярных транзисторах. Переключатель тока второго информационного входа используется для инвертирования входного сигнала, благодаря , чему на базы транзисторов выходного переключателя тока один из сигналов поступает в инверсной форме. Использование мажоритарного элемента, построенного на переключателях тока и работающего с однофазными входными сигналами, отсутствие переключателя тока для одного из информационных входов позволяет достичь указанной выше цели. 1 йл. i (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (1! 4 Н 03 К 19/086, 19/?3

111

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4134571/24-21 (22). 15,!0.86 (46) 29.02.88. Бюл. У 8 (72) А.С.Березин, В.И.Кимарский, 1О.И.Кузовлев, Е.М.Онищенко, С.В.Сушко и И.В.Черняк (53) 62!.374(088.8) (56) Мкртчян С.О. Проектирование логических устройств ЭВМ на нейтронньм элементах. М.: Энергия, 1977, с.132, рис.5-1.

Будинский Я. Логические цепи в цифровой технике. М.: Связь, !977, с. 49, рис.1.36. (54) МАЖОРИТАРНЫИ ЭЛЕМЕНТ (57) Изобретение относится к комбинационным логическим схемам на биполяр„„SU„„1378049 А 1 ных транзисторах. Цель изобретения— повышение быстродействия и снижение потребляемой мощности, Электрическая схема мажоритарного элемента построена на биполярных транзисторах. Переключатель тока второго информационного входа используется для инвертирования входного сигнала, благодаря чему на базы транзисторов выходного переключателя тока один из сигналов поступает в инверсной форме. Использование мажоритарного элемента, построенного на переключателях тока и работающего с однофаэными входными сигналами, отсутствие переключателя тока для одного иэ информационньм входов позволяет достичь указанной вьппе цели. 1 йл.

1378049

Изобретение относится к импульсной технике, а точнее к комбинационным логическим схемам на биполярных транзисторах, 5

Целью изобретения является повышение быстродействия и снижение потребляемой мощности.

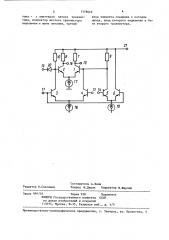

На чертеже представлена принципиальная схема мажоритарного элемента.

Мажоритарный элемент содержит первый 1, второй 2, третий 3, четвертый

4, пятый 5 и шестой 6 транзисторы, первый 7, второй 8, третий 9, четвер- 15 тый 10 резисторы, шины опорного напряжения 11 первый 12, второй )3, третий 14 входы, прямой 15 и инверс- . ный 16 выходы, первый )7, второй 18, третий 19 источники тока, диод 20 и 20 шину питания 21.

Коллекторы первого ) и второго 2 транзисторов соединены соответственно с прямым 15 и инверсным 16 выходами устройства и подключены через пер- 25 вый 7 и второй 8 резисторы к шине питания 21. Первый 17, второй 18 и третий 19 источники тока подключены к эмиттерам соответственно транзисторов 1 и 2, 4 и 3, 5 и 6, база перво-, го транзистора 1 подключена через третий резистор 9 к шине питания 21 и соединена с коллекторами четвертого 4 и пятого 5 транзисторов, база второго транзистора 2 подключена к 35 шине питания 2) через четвертый резистор 10 и соединена с коллектором . третьего транзистора 3 и с анодом диода 20, катод которого подключен к первому входу 12, второй 13 и тре- 40 тий 14 входы соединены соответственно с базами четвертого 4 и пятого 5 транзисторов, шина опорного напряжения 11 подключена к базам третьего

3 и шестого 6 транзисторов, а кол- 45 лектор шестого транзистора б соединен с шиной питания 21.

Устройство работает следующим образом.

Мажоритарный элемент построен на переключателях тока и предполагается, что он будет использоваться совместно с элементами 3GJI типа. Поэтому величина перепада уровней его входных сигналов равна U, ;

" 1 «о» конкретно Н = Е „ - U, U

= F,„ — 2Uo Номиналы резисторов 7 и 8 выбраны таким образом, что падение напряжения, создаваемое на каждом из них током источника тока 17, равно 0,5 U ° Ток источника 19 вдвое превосходит ток источника 18, который создает на резисторах 9 и 10 падение напряжения в 0,5 U

Когда уровни сигналов на входах

12 и 14 различны, логический уровень сигнала на выходе 15 повторяет уровень сигнала на входе 13 ° Если же уровни сигналов на входах )2 и 14 равны, уровень сигнала на выходе )5 не зависит от, состояния сигнала на входе 13, и повторяет логический уровень сигналов на входах 12 и 14.

Таким образом, устройство соответствует по функциональному назначению мажоритарному элементу.

Мажоритарный элемент имеет повышенное быстродействие ввиду уменьшения узловых паразитных емкостей баз транзисторов выходного переключателя тока и уменьшенную потребляемую мощность за счет сокращения числа источников тока.

Формула изобретения

Мажоритарный элемент, содержащий три входа, первый и второй транзисторы, эмиттеры которых соединены, коллекторы подключены соответственно к прямому и инверсному выходам элемента и соединены соответственно через первый и второй резисторы с шиной питания, эмиттеры третьего и четвертого транзисторов соединены, ба. за первого транзистора соединена с коллекторами четвертого и пятого транзисторов и через третий резистор подключена к шине питания, база второго транзистора соединена с коллектором третьего транзистора и подключена через четвертый резистор к шине питания, шина опорного напряжения соединена с базами третьего и шестого транзисторов, первый вход элемента соединен с базой четвертого транзистора, второй вход элемента соединен с базой пятого транзистора, о т— л и ч а ю шийся тем, что, с целью повышения быстродействия и снижения потребляемой мощности, в него введены три источника тока и диод, причем первый источник тока соединен с эмиттером первого транзистора, второй источник тока — с эмнттером третьего транзистора, третий источник

1378049

Составитель А.Янов

Техред M.Äèäûê Корректор М.Шароши

Редактор О.Спесивых

Заказ 890/55 Тираж 928

ВНИКАЛИ Государственного комитета по делам изобретений и открытий

113035, Мрсква, Ж-35, Раушская наб., д. 4/5

Подписное

СССР

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 тока — с эмиттером пятого транзистора, коллектор шестого транзистора подключен к шине питания, третий вход элемента соединен с катодом диода, анод которого подключен к базе второго транзистора.