Блок задержки цифровой информации с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и .может быть использовано в л иниях задержки цифровой информации. Цель изобретения - повышение надежности блока. Блок цифровой задержки информации содержит входной регистр 1, блоки 2, 4 кодирования, накопитель 3, выходной регистр 5, блоки 6, 9 сравнения, первый 7 и второй 8 счетчики адреса, элемент НЕ 10, элемент И 11, элементы 12, 14 задержки, одновибраторы 13, 15. Устройство позволяет осуществлять чтение по правильному (следующему ) адресу при сбое в счете первого счетчика 7 адреса. 1 ил.

COIO3 СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН g 4 б 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4082652/24-24 (22) 16.05.86 (46) 15.04.88. Бюл. № 14 (72) В. Н. Лацин, Е. Л. Полин, А. В. Дрозд, В. Л. Панченко и А. Е. Малярчук (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 1193653, кл. G 06 F 1/04, 1984.

Авторское свидетельство СССР № 1287137, кл. G 06 F 1/04, 1985.

„„Я0„„1388956 А 1 (54) БЛОК ЗАДЕР)ККИ ЦИФРОВОД

И НФОРМАЦИ И С САМОКОНТРОЛ ЕМ (57) Изобретение относится к вычислительной технике и может быть использовано в линиях задержки цифровой информации.

Цель изобретения — повышение надежности блока. Блок цифровой задержки информации содержит входной регистр 1, блоки 2, 4 кодирования, накопитель 3, выходной регистр 5, блоки 6, 9 сравнения, первый 7 и второй 8 счетчики адреса, элемент HE 10, элемент И !1, элементы 12, 14 задержки, одновибраторы 13, 15. Устройство позволяет осуществлять чтение по правильному (следующему) адресу при сбое в счете первого счетчика 7 адреса. 1 ил.

1388956

Формула изобретения 9

Изобретение относится к вычислительной технике и может быть использовано в линиях задержки цифровой информации.

Цель изобретения — повышение надежности блока.

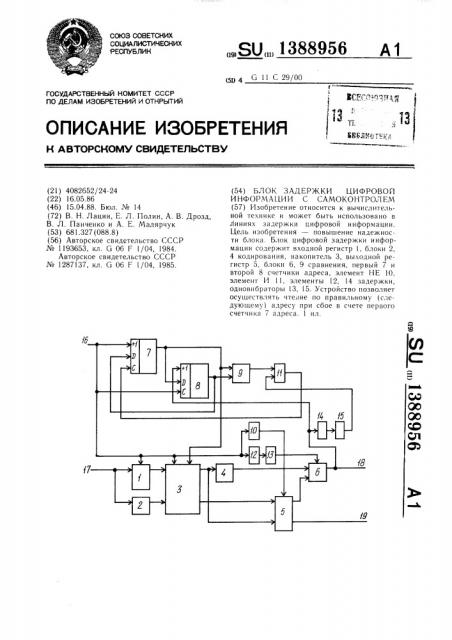

На чертеже изображена структурная схема блока цифровой задержки информации.

Устройство содержит входной регистр 1, первый блок 2 кодирования, накопитель 3, второй блок 4 кодирования, выходной регистр

5, первый блок 6 сравнения, первый 7 и второй 8 счетчики адреса, второй блок 9 сравнения, элемент HE 10, элемент И 11, первый элемент 2 задержки, первый одновибратор

13, второй элемент 14 задержки, второй одновибратор 15, вход 16 синхронизации, информационный вход 17, контрольный выход

18, информационный выход 19.

Устройство работает следующим образом.

В начальный момент происходит обнуление всех регистров устройства, счетчиков 7 и 8 и блока (цепи обнуления на чертеже не показаны).

На информационный вход 17 устройства начинают поступать данные, сопровождаемые синхроимпульсами типа «меандр» на входе синхронизации 16 устройства. Г1о каждому переднему фронту синхронизации происходит прием информации во входной регистр l. Одновременно происходит увеличение на единицу адреса в счетчике 7, причем во время первой половины периода действия синхроимпульса происходит чтение информации из ячейки с текущим адресом информации, записанной к тактов назад, а во время второй половины периода — запись информации в эту же ячейку, которая в свою очередь происходит через к тактов (гд» к— величина задержки, определяемая коэффициентом пересчета счетчика 7) . Таким образом, осуществляется задержка входных данных на к тактов. Информационные разряды -го слова записываются в накопитель вместе с контрольными разрядами следующего (i+1) -го информационного слова (из-за задержки на входном регистре 1).

Контрольные разряды формируются блоком

2. Через к тактов начинают считываться i-e информационное слово и контрольные разряды (i+1) -го слова. Выходной регистр 5 содержит информационные разряды (i— — 1)-ro слова и контрольные разряды i-го слова. Первый блок 6 сравнения в этот момент вырабатывает сигнал о совпадении контрольных разрядов.. вычисленных блоком

4, для считываемых информационных разрядов i-го слова с контрольными разрядами, вычисленными для этого же слова до записи в накопитель, 3. Стробирование блока 6 сравнения осуществляется с помощью элемента 12 задержки и одновибратора 13. При этом задержка элемента 12 должна быть достаточной для того, чтобы считанная в данном такте информация распространилась до выхода блока 6 сравнения.

1О

2С

4О

Одновибратор 13 формирует короткий импульс, во время действия которого на выходе блока 6 сравнения появляется «0», если контрольные разряды совпали, и «1», если контрольные разряды считываемого слова, вычисленные до записи и после считывания, не совпали. Длительность задержки и длительность импульса одновибратора 13 в сумме не должны превышать длительность цикла «Чтение».

Информация о сбое в считываемом в данный момент слове поступает на выход 18 устройства. Одновременно происходит проверка и, если нужно, исправление адреса в счетчике 7. Исправление осуществляется следующим образом: по переднему фронту синхроимпульсов на входе 16 устройства счетчик 7 увеличивает свой адрес на единицу, по этому же фронту предыдущий адрес переписывается в счетчик 8. Таким образом, счетчик постоянно хранит адрес предыдущего цикла чтение-запись. Гlри появлении сигнала о сбое («1» на выходе блока 6 сравнения) счетчик увеличивает свое состояние на единицу, Если при этом адреса, выдаваемые счетчиками 7 и 8, совпадают, то на выходе блока 9 сравнения возникает сигнал «0».

Если же совпадение не произошло (т. е. счетчик 7 увеличил свое состояние больше чем на единицу), то сигнал о несовпадении («1» на выходе блока сравнения) через элемент И !! принимает в счетчик 7 содержимое счетчика 8 (предыдущий адрес, увеличенный HB единицу). Тем самым восстанавливается состояние счетчика 7 и в течение оставшегося времени цикла осуществляется чтение по правильному адресу. По окончании цикла чтение — отрицательный перепад синхроимпульса на входе 16 устройства в выходной регистр 5 записывается информация, считанная по правильному адресу. Стробирование выходного сигнала блока 9 сравнения осуществляется с помо «ью элемента

14 задержки и одновибратора !5 таким образом, что выход блока 9 сравнения управляет входом приема в счетчик 7 только после того, как счетчик 8 увеличит свое состояние на единицу и результат сравнения поступит на вход элемента И 11.

Блок задержки цифровой информации с самоконтролем, содержащий входной регистр, первый и второй блоки кодирования, накопитель, первый блок сравнения, выходной регистр и первый счетчик адреса, причем информационный вход входного регистра является информационным входом блока, выход входного регистра подключен к информационному входу накопителя, адресные входы которого соединены с выходами разрядов первого счетчика адреса, выходы контрольных разрядов накопителя подключены к входам контрольных разрядов выходного!

388956

Составитель В. Рудаков

P едактор Н. Швыдкая Техред И. Верес Корректор А. Зимокосов

Заказ 1525/54 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1! 3035, Москва, УК вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 регистра, выходы контрольных разрядов которого соединены с информационными входами первой группы первого блока сравнения, выходы информационных разрядов выходного регистра являются информационными выходами блока, отличающийся тем, что, с целью повышения надежности блока, в него введены второй счетчик адреса, второй блок сравнения, элемент НЕ, элемент И, первый и второй элементы задержки, первый и второй одновибраторы, причем вход первого блока кодирования подключен к информационному входу блока, выходы первого блока кодирования соединены с входами контрольных разрядов накопителя, выходы информационных разрядов которого подключены к входам второго блока кодирования и входам информационных разрядов выходного регистра, выходы второго блока кодирования соединены с входами второй группы первого блока сравнения, выход которого является контрольным выходом блока и соединен непосредственно со счетным входом второго счетчика адреса и через второй элемент задержки — с входом второго одновибратора, сче-ный вход первого счетчика адреса, вход синхронизации второго счетчика адреса, управляющие входы входного регистра и накопителя, вход элемента НЕ и вход первого элемента задержки объединены и являются входом синхронизации блока, выход элемента НЕ подключен к управляющему входу выходного регистра, выходы разрядов первого счетчика адреса соединены с входами разрядов второго счетчика адреса и одними из входов второго блока сравнения, другие входы которого подключены к выходам разрядов второго счетчика адреса и входам разрядов первого счетчика адреса, выход второго блока сравнения подключен к первому входу элемента И, второй вход которого соединен с выходом второго одновибратора, выход элемента И подключен к входу синхронизации первого счетчика адреса, выход первого элемента задержки соединен с вхо20 дом первого одновибратора, выход которого подключен к управляющему входу первого блока сравнения.