Генератор тестов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре контроля и диагностирования-цифровых узлов. Цель изобретения - расширение .области применения за счет реализации возможности .генерации тестов для тестирования блоков, имеющих двунаправленные входы/выходы. Генер-атор содержит блок 2 памяти тестов для хранения теста, блок 10 памяти реакций для регистрации реакций контролируемого блока, регистр 4 для хранения тестовых ,слов, считанных из блока 2 памяти тестов, регистр 6 реакций для приема реакций, записываемых в блок 10 памяти реакций, коммутатор 7 для определения направления включения выводов контролируемого узла, счетчик 3 адреса для адресации блока 2 памяти тестов и блока 10 памяти реакций , элемент 1 задержки для форм ирования сигнала выборки, счетчик 5 для отсчета тестовьпс слов между сменами направления включения выводов контролируемого блока, элемент НЕ 9, элементы И 8, 12, 13, триггер 14, элемент ИЛИ 15 для распределения считываемых из блока 2 памяти тестов слов между регистром 4, коммутатором 7 и счетчиком 5. В- процессе тесо 9 (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5g 4 G 06 F 11/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М Д ВТОРСКОМ У СВИДЕТЕЛЬСТВУ . г (54) ГЕНЕРАТОР ТЕСТОВ (57) Изобретение относится к вычислительной технике и может быть ис(21) 4150883/24-24 (22) 11.11.86 (46) 23.06.88. Broa. "- 23 (72) А.Г.Шипита, В.П.Карпенко, Ю.P.Æåðäåâ, В.В.Лебедь и В.С.Волощук (53) 681.3 (088.8) (56) Авторское свидетельство СССР

У 642711, кл. G 06 F 11/22, 1978.

Авторское свидетельство СССР

Ф 836635, кл. G 06 F 11/22, 1978. пользовано в аппаратуре контроля и диагностирования -цифровых узлов. Цель изобретения — расширение области применения sa счет реализации возможности:.генерации тестов для тестирова" ния блоков, имеющих двунаправленные входы/выходы. Генератор содержит

„„SU„„1405060 А 1 блок 2 памяти тестов для хранения теста, блок 10 памяти реакций для регистрации реакций контролируемого блока, регистр 4 для хранения тестовых, слов, считанных из блока 2 памяти тестов, регистр 6 реакций для приема реакций, записываемых в. блок

10 памяти реакций, коммутатор 7 для определения направления включейия выводов контролируемого узла, счетчик 3 адреса для адресации блока 2 памяти тестов и блока 10 памяти реакций, элемент 1 задержки для форми= рования сигнала выборки, счетчик 5 для отсчета тестовых слов между сменами направления включения выводов контролируемого блока, элемент НЕ 9, элементы И 8, 12, 13, триггер 14, элемент ИЛИ 15 для распределения считываемых из блока 2 памяти тестов слов между регистром 4, коммутатором 7 и счетчиком 5. В.процессе тес140506! тирования из блока 2 памяти тестов считываются слова. Слово, определяю( щее направление включения двунаправленных выводов контролируемого блока, принимается в коммутатор 7;,слово, определяющее количество тестовых слов до смены направления включения выводов контролируемого блока, принимается в счетчик 5, тестовые слова принимаются в регистр 4 и через коммутатор 7 поступают на входы контролируемого блока 11. С выходов контролируемого блока 11 реакции через коммутатор 7 принимаются в регистр 6 реакций, с выходов которого записываются в блок 10 памяти реакций. Наличие в устройстве счетчика 5, элементов 8, 9, 12, 13, 15, триггера 14 и введение в последовательность тестовых слов пар управляющих слов позволяют изменять направление включения выводов контролируемого блока при каждом считывании из блока 2 памяти тестов пары управляющих слов. 3 ил, Изобретение относится к автоматике, вычислительной технике и может быть использовано для контроля и ди". агностики цифровых блоков.

Цель изобретения — расширение области применения за счет реализации возможности генерации тестов для тестировайия блоков, имеющих двунаправленные входы/выходы.

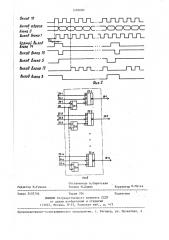

На фиг.1 показана структурная схема генератора; на фиг. 2 — временная

1 диаграмма; на фиг. 3 — коммутатор, Генератор содержит элемент 1 за.держки, блок 2 памяти тестов, счетчик 3 адреса, регистр 4, счетчик 5, регистр 6 реакций, коммутатор 7, элемент И 8, элемент НЕ 9, блок 10 памяти реакций, контролируемый блок 11, элементы И 12 и 13, триггер 14, элемент ИЛИ 15, синхровход !6, шину 17 ввода тестов в блок памяти тестов, вход 18 сброса, выходную шину 19, информационный выход 20 (не показан) реакции контролируемого блока il.

Коммутатор 7 (фиг.3) содержит триггеры 21.1-21.п, шинные формирова тели 22.1-22.п, выходы 23.1-23.п раз° рядов с данных, входы 24.1-24.п разрядов данных, входы 25.1-25.п разрядов управляющих слов, синхровход 26 приема управляющих слов (п — число входов/выходов контролируемого блока).

Устройство работает следующим образом.

Контролируемый блок 11 имеет и выводов, .каждый из которых может быть входным и выходным, Кроме того, 5 !

0 l5

ЗО

m выводов (О

Первое слово указывает входы и вы" ходы блока 11, второе слово — количество тестовых слов, которые будут считаны из блока 2 памяти тестов до смены направления включения выводов ш (до следующей пары управляющих слов). Считывание из блока 2 памяти тестов происходит непрерывно по синх" росигналам шины 16.

В исходном состоянии счетчик 3 адреса, счетчик 5 и триггер 14 сброшены сигналом сброса, поступающим на вход 18 сброса.

По шине 17 в блок 2 памяти записан тест. При поступлении тактовых импульсов с входа 16 на счетный вход счетчика 3 адреса (счетчик работает по заднему фронту тактовых импульсов) и на вход элемента 1 задержки (элемент задержки формирует сигнал выборки, задержанный относительно тактовых импульсов на время

T) из блока 2 памяти тестов считываются тестовые слова, При считывании управляющих слов выход заема счетчика 5 равен логическому нулю и

1405060 через элемент И 8 блокирует поступление тактовых импульсов через элемент И 12 на вычитающий вход счетчика 5 и вход синхронизации регистра

-5

4 и открывает через элемент НЕ 9 прохождение тактовых импульсов через элемент И 13 на вход синхронизации триггера 14, который, переключаясь, вырабатывает синхросигнал в коммута- .10 тор 7 и разрешает прохождение тактовых импульсов через элемент ИЛИ 15 на вход записи счетчика 5, Триггер 14 реализован на стандарт" ном элементе 530 ТМ2, íà R-вход которого подключен выход элемента И, который объединяет два входа сброса.

Первые их пары управляющих слов записываются в коммутатор 7, вторые в счетчик 5, после чего сигнал на вы- 20 ходе элемента И 8 становится равным логической единице, запрещая выработку сигналов записи в коммутатор 7 и счетчик 5 и разрешая прохождение так25 товых импульсов через элемент И 12.

С выхода регистра 4 тестовые слова через коммутатор 7 поступают на входы контролируемого блока 11, с выходов которого слова реакций через комсигналом переноса счетчика 3 адреса в начале каждого цикла.Счетчик 5 ðåàключен выход элемента ИЛИ.

В случае отсутствия у контролируе"

50 мутатор 7 и регистр б реакции записываются в блок 10 памяти реакций.

По окончании тестирования накопленные реакции считываются по шине 20

30 ческом считывании теста из блока 2 памяти тестов счетчик 5 сбрасывается

35 лизован на стандартном элементе

533 ИЕ7, на вход сброса которого под- щ лу тактов контроля.

Работа коммутатора 7 происходит следующим образом.

При поступлении импульса на синхровход 26, триггеры 21.1-21„n устанавливаются в состояние, соответствующее значениям сигналов на входах разрядов управляющих слов 25.1-25,п.

Состояния триггеров 21.1-21,п определяют направление передачи данных, через соответствующие шинные формирователи 22.1-22.п. Так, например, шинный формирователь 22.1 может пропускать информацию с входа 24.1 раз55 мого блока 11 двунаправленных выводов второе слово первой пары управ" ляющих слов содержит код, равный чис- д5 ряда данных на вход/выход 19.1, либо с входа/выхода 19.1 на выход 23.1 разряд данных.

Формула изобретения

Генератор тестов, содержащий регистр, триггер, коммутатор, о т л ич а ю щ и Й с я тем, что, с целью расширения области применения путем реализации возможности генерации тестов для тестирования блоков, имеющих двунаправленные входы-выходы, генератор содержит блок памяти тестов, счетчик, элемент задержки, счетчик адреса, три элемента И, элемент НЕ, элемент ИЛИ, причем вход синхронизации генератора соединен со счетным входом счетчика адреса, с входом элемента задержки, с первыми входами первого и второго элементов И и элемента ИЛИ, выход которого соединен с первым входом третьего элемента И и входом записи счетчика, выход заема, которого соединен с вторым входом третьего элемента И, выход которого соединен с вторым входом первого элемента И и через элемент HE — с вто-. рым входом второго элемента И и входом синхронизации триггера, прямой выход которого соединен со стробирую- . щим входом коммутатора, выход которого является выходом генератора, вход сброса которо" î соединен с входами сброса счетчика адреса, счетчика и триггера, инверсный выход которого соединен с D-входом триггера и с вторым входом элемента ИЛИ, выход первого элемента И соединен с синхровходом регистра и входом управления счетчика, вход блокировки которого соединен с выходом заема счетчика адреса, группа разрядных выходов которого соединена с группой адресных входов блока памяти тестов, синхровход которого соединен с выходом элемента задержки, выход второго элемента И соединен с входом сброса триггера, выходы поля тестов блока памяти соединень1 с информационными входами регистра, выходы которого соедине" ны с информационными входами коммутатора, управляющие входы которого соединены с выходами поля управления блока памяти тестов, выходы поля числа тестовых слов в текущем наборе блока памяти тестов соединены с информационными входами счетчика.

1405060

Выход 1Р

8ыход адреса

&ока 3 диход длока 7

Ц)ямой Ьиог лака 19

8ихИ 5мка 6

8ияод длока 5 дыхОУ 5АОЯ2 IZ

»ео< длва 9

Составитель А.Сиротская

Техред 11.Дидык

Редактор Н.Гунько

Корректор И.11уска

Подписное

Заказ 3.1 07/54

Тираж 704

В11ИИПИ Государственного комитета СССР по делам изобретений и открытий!

13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4