Преобразователь биимпульсного кода в код "без возврата к нулю

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, обрабатываемой в ЭВМ. Изобретение благодаря малому времени вхождения в синхронизм, обеспечивает повышение быстродействия преобразователя. Преобразователь биимпульсного кода в код без возврата к нулю содержит RS- триггер 1, два элемента 2 и 10 задержки , два элемента 3 и 8 И, D-триггер 4, блок 5 сравнения, два инвертора 6 и 7 и элемент 9 ИЛИ. 2 ил. с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУбЛИК

„„SU„„140 112 А1 (51) 4 Н 03 M 5/12

/7

ТЕНИЯ /

ОПИСАНИЕ ИЗОБРЕ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Г. с

/ фиг.!

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4074589/24-24 (22) 27.03.86 (46) 23,06.88. Бюл. N 23 (72) С.В. Шипилов, Е.А. Березина, И.А. Воропаева и Ж,П. Ложкова (53) 681.325(088,8) (56) Патент США У 3820031, кл. Н 03 К 13/00, 1974.

Патент США 11 - 4292626, кл. Н 03 К 13/24, 1981. (54) ПРЕОБРАЗОВАТЕЛЬ БИИМПУЛЬСНОГО

КОДА В КОД "БЕЗ ВОЗВРАТА К НУЛЮ" (57) Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, обрабатываемой в 3ВМ. Изобретение благодаря малому времени вхождения в синхронизм, обеспечивает повышение быстродействия преобразователя. Преобразователь биимпульсного кода в код

"без возврата к нулю" содержит RSтриггер 1, два элемента 2 и 10 задержки, два элемента 3 и 8 И, D-триггер

4, блок 5 сравнения, два инвертора

6 и 7 и элемент 9 ИЛИ. 2 ил.

1405112

Изобретение относится к вычислительной технике а именно к устройЭ

;ствам преобразования информации, об рабатываемой в ЭВМ, Целью изобретения является увели чение быстродействия преобразователя.

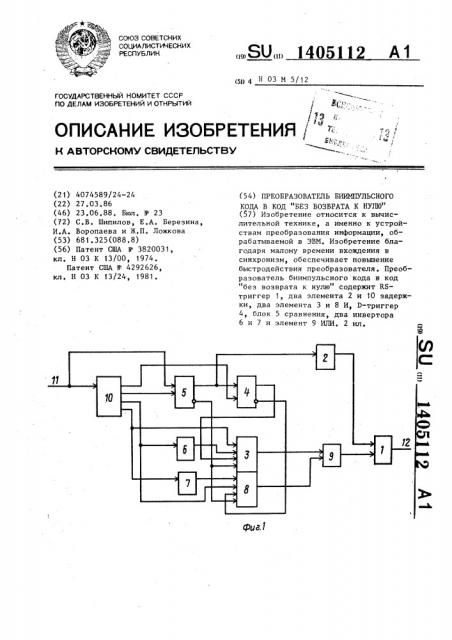

На фиг. 1 представлена функциональ ная схема преобразователя, на фиг. 2— временные диаграммы, поясняющие его ( работу, Преобразователь биимпульсного ко— да в код без возврата к нулю содержит RS-триггер 1, первый элемент

2 задержкиу первый элемент И 31 15

D-триггер 4, блок 5 сравнения, первый и второй инверторы 6 и 7, второй элемент И 8, элемент ИЛИ 9 и второй элемент 10 задержки, вход 11 и выход 12.

На фиг. 2 соответствующими индексами обозначены входной сигнал а, сигнал б на первом выходе элемента 10,.сигнал в на втором выходе элемен-! та 10, сигнал г на прямом выходе бло-25 ка 5, сигнал д на инверсном выходе блока 5, сигнал е на прямом выходе триггера 4, сигнал ж на третьем вы ходе элемента 10, сигнал з на выходе инвертора 6, сигнал и на четвер,том выходе элемента 10, сигнал к на

;выходе инвертора 7, сигнал л на вы ходе элемента 3 сигнал м на выходе

t элемента 8, сигнал н на выходе элемен-! та 9, сигнал о на выходе элемента 2, сигнал и на выходе триггера 1.

Элемент 10 задержки формирует на своих выходах сигналы, задержанные относительно исходного биимпульсного кода соответственно на первом выходе40 на четверть периода, на втором — на полпериода, на третьем — на период и на четвертом — на три вторых периода.

Блок 5 сравнения формирует сигналы, соответствующие синхроимпульсам

45 единичных бит.

D-триггер 4 запоминает уровень последнего единичного бита информации.

Элемент 2 задержки предназначен для согласования фазы синхроимпульсов единичных бит с фазой синхроимпульсов нулевых бит.

RS-триггер 1 формирует выходной код "без возврата к нулю" (БВН).

Элемент HJIH 9 суммирует синхроимпульсы нулевых бит, Элемент И 3 предназначен для выделения синхроимпульсов нулевых бит, начинающихся с высокого уровня. Элемент И 8 предназначен для выделения синхроимпульсов нулевых бит, начинающихся с низкого уровня, Преобразователь работает следующим образом.

Биимпульсный код, поданный на вход 11, поступает на вход элемента

10 задержки. В результате сравнения этого кода и задержанного на полпериода кода на выходе блока 5 сравнения появляются синхроимпульсы единичных бит, по которым устанавливается состояние D-триггера 4 в зависимости от уровня единичного бита.

Если после единичного бита следует несколько нулевых бит, то состояние

D-триггера 4 не меняется. Единичное состояние D-триггера 4 свидетельствует о том, что нулевые биты, следующие за единичным, начинаются с низкого уровня, а нулевое состояние — с высокого уровня. Задержанный на период код с третьего выхода элемента

10 задержки и инверсный код, задержанный на полтора периода, с выхода инвертора 7 подаются на вход элемента И 8. В связи с тем, что отдельные импульсы (результат совпадения в элементе И 8) совпадают с синхроимпульсами единичных бит, такие импульсы блокируются инверсными синхроимпульсами единичных бит. Нулевое состояние D-триггера 4 разрешает прохождение синхроимпульсов нулевых бит, которые начинались с высокого уровня. Аналогично элементу И 8 на выходе элемента И 3 выделяются синхроимпульсы нулевых бит, которые начинаются с низкого уровня, а на выходе элемента ИЛИ 9 образуются синхроимпульсы нулевых бит, которые задержаны относительно синхроимпульсов единичных бит на полпериода ° Поэтому синхроимпульсы единичных бит задерживаются элементом 2 задержки на полпериода и подаются на S-вход RS-триггера 1. На выходе RS-триггера 1 образуется код БВН, поскольку на R — вход

RS-триггера 1 подаются синхроимпульсы нулевых бит, на S — вход — синхроимпульсы единичных бит, Таким образом, преобразователь обеспечивает преобразование биимпульсного кода в код БВН на скорости обмена, равной предельному быстродействию применяемой элементной базы.

Для вхождения в синхронизм достаточ140 .>! 1 но одного единичного бита, по которому устанавливается D-триггер 4, который определяет, с какого уровня начинается нулевой бит.

Формула и з о б р е т е н и я

Преобразователь биимпульсного кода в код "без возврата к нулю" содержащий RS-триггер, первый элемент задержки и первый элемент И, о т л и ч а ю шийся тем, что, с целью увеличения быстродействия преобразователя, в него введены D-триггер, блок сравнения, инверторы, второй элемент И, элемент ИЛИ и второй элемент задержки, первый и второй выходы которого соединены соответ- 2О ственно с D-входом D-триггера и с первым входом блока сравнения, прямой выход которого соединен с С-вхо.дом D-триггера и входом первого элемента задержки, выход которого соеди- 25

4 нен с S — входам RS-триггера, инверсный выход блока сравнения соединен с первыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с R-входом RS-триггера, третий выход второго элемента задержки соединен непосредственно с вторым входом второго элемента И и через первый инвертор с вторым входом первого элемента И, четвертый выход второго элемента задержки соединен непосредственно с третьим входом первого элемента и через второй инвертор, с третьим входом второго элемента И, прямой и инверсный выходы D-vpzrpepa соединены с четвертыми входами соответственно первого и второго элементов И, вход второго элемента задержки объединен с вторым входом

V блока сравнения и является входом преобразователя, выход RS-триггера является выходом преобразователя.

0 q! 0 !q 0 авиа 2