Четырехвходовый одноразрядный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и предназначено для построения быстродействующих арифметических устройств. Цель -изобретения - повышение быстродействия . Сумматор содержит шесть элементов ИЛИ 1-6, два элемента сложения по модулю два 7,8 и один элемент И 9. При подаче на входы 10-13 сумматора четырех одноразрядных двоичных чисел на его выходах реализуются логические функции, соответствующие сигналам суммы первого и второго переносов . 1 ил., I табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБ ЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4139965/24-24 (22) 14.10.86 (46) 15.08.88.8юл.H 30 (72) Л.Б.Авгуль, В.П.Супрун, В.П.Якую и А.П.Криницкий (53) 681 .325.5 (088.8) (56) Авторское свидетельство СССР

У 1228099, кл.G 06 F 7/50, 1984.

Авторское свидетельство СССР

9 1 37421 6, кл .G 06 F 7/50, 1 986 .

„.SU„„1417012 А1 (5lJ4 G 06 F 7/50 (54) ЧЕТЫРЕХВХОДОВЫЙ ОДНОРАЗРЯДНЫЙ

СУММАТОР (57) Изобретение относится к области вычислительной техники и предназначено для построения быстродействующих арифметических устройств. Цель

-изобретения — повышение быстродействия. Сумматор содержит шесть элементов ИЛИ l --6, два элемента сложения по модулю два 7,8 и один элемент

И 9. При подаче на входы 10-13 сумматора четырех одноразрядных двоичных чисел на его выходах реализуются логические функции„ соответствующие сигналам суммы первого и второго переносов. 1 ил., 1 табл.

1417012

Продолжение таблицы

Изобретение с гносится к вычисли.тельной технике и предназначено для построения быстродействующих арифметических устройств.

Цель изобретения — повышение быст5 родействия.

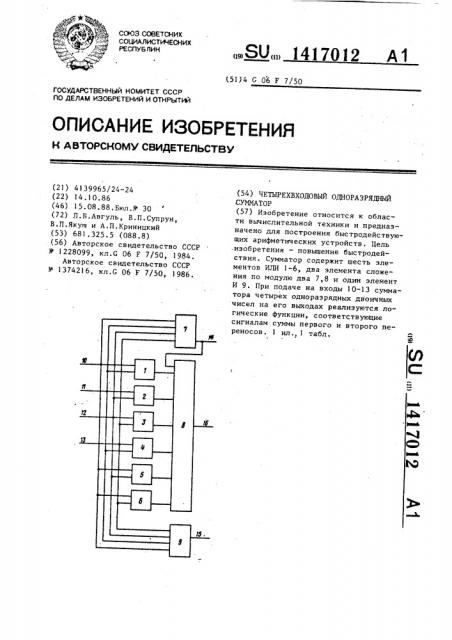

На чертеже представлена функцио,нальная схема четырехвходового од;норазрядного сумматора.

Сумматор содержит элементы

: ИЛИ еl-6„ элементы сложения по моду; лю два 7 и 8, элемент И 9, входы

: 10-13, выходы 14-16.

Сумматор работает следующим, образом.

На входы 10-13 подаются двоичные переменные Х вЂ” Х4 соответственно. На

l выходе 14 реализуется логическая функция

4 5 1 6 7

0 0 0

1 1 0

0 l !

0 0 0

1 0 0

0 1 0 0 0

9S 1

1 0 1

0 1 0

1 1 0

l l 1

Р, Х Х, ХЪ Х4

Четырехвходовый одноразрядный сумматор, содержащий два элемента сложения по модулю два и элемент И, причем входы первого элемента сложения по модулю два соединены с входами сумматора с первого по четвертый,, а выход — с первым выходом сумматора, выход второго элемента сложения по мод дулю два соединен с вторым выходом сумматора, входы элемента И соединены с входами сумматора с первого по четвертый, а выход - с третьим выходом сумматора, о т л и ч а ю щ и й— х90 с я тем, что, с целью повышения быстродействия, сумматор содержит элементы ИЛИ с первого по шестой, первые входы первого, пятого и шестого элементов ИЛИ соединены с первым

45 входом сумматора, второй вход перво- . го и первые входы второго и четвертого элементов KIN соеДинены с вторым входом сумматора, вторые входы второго и пятого и первый вход третьего элементов ИЛИ соединены с третьим входом сумматора, вторые входы третьего, четвертого и шестого элементов ИЛ4 соединены с четвертым входом сумматора, выходы элементов

ИЛИ соединены с одноименными входами второго элемента сложения по модулю два, седьмой вход которого соединен с выходом первого элемента сложения по модулю два.

О(Х Ч Х)eS, Х, S XB X О+Х ИРХ ,соответствующая сигналу суммы; на выходе 15 — логическая функция соответствующая сигналу первого переноса; на выходе 16 - логическая функция

Р, (Х,Ч Х )Д+(Х, Ч Х }О

О (Х, Ч Х )Я Х 3 Х )® (Xg Ч X4)O+) соответствующая сигналу второго переноса.

Значения логических функций S, Р, и Р> для возможных наборов переменных Х,, Ха лривецены в таблице.

Х, ХЪ Х Б Р Р7

2 3 4 5 6 7

0 0 0 0 0 0 0

0 0 0 1 1 0 0

0 0 1 0 1 0 0

0 0 1 1 0 0 1

0 1 0 0 1 0 0

0 1 0 l 0 0 1

0 0 1 0 0 1

0 1 1 1 0 !

1 1 0 0 0 0

1 1 0 1 1 0

Формула изобретения