Устройство для защиты мдп-интегральных схем от статического электричества

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Al (19) (И) ! (51) 4 Н 03 К 19/094

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4174155/24-21 (22) 06.01.87 (46) 07.09.88. Бюл. Р 33 (72) А.С. Свердлов и Б.М. Соскин (53) 621.374 (088,8) (56) Интегральные схемы на МДП-прибо рах./ Под ред. А.Н. Кармазинского.

М.: Мир, 1975, с. 130.

Авторское свидетельство СССР

N - 883300998877, кл. Н 01 L 27/04, 1985 ° (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ МДП-ИНТЕГРАЛЬНЫХ СХЕМ ОТ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА (57) Изобретение относится к области электронной техники. С целью улучше ния защитных свойств устройства путем уменьшения напряжения между шинами ин" тегральной схемы и подложкой в него введен дополнительный биполярный транзистор 5, эмиттер которого соединен с выводом 2 устройства, а коллектор и база соединены с выводом 3 устройства. Устойчивость интегральных схем к воздействию статического электричества повышается приблизительно на 200-400 В.. Это позволяет повысить надежность интегральных.схем в эксплуатации. 1 ил.! 422398

Формула изобретения

Составитель И. Горелов

Техред И.Ходанич

Корректор И.Муска

Редактор И. Горная

Заказ 4441/57

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москвар Ж 35 ° Раушская наб °, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Изобретение относится к электронной технике, а именно к устройствам

:для защиты МДП-интегральных схем (ИС) от статического электричества, и может быть использовано в полупроводниковом производстве при разработке и конструировании ИС на МДП-транзисторах.

Цель изобретения — улучшение за.: ;щитных свойств устройства в результа::те уменьшения напряжения между общей ,шиной ИС и ее подложкой.

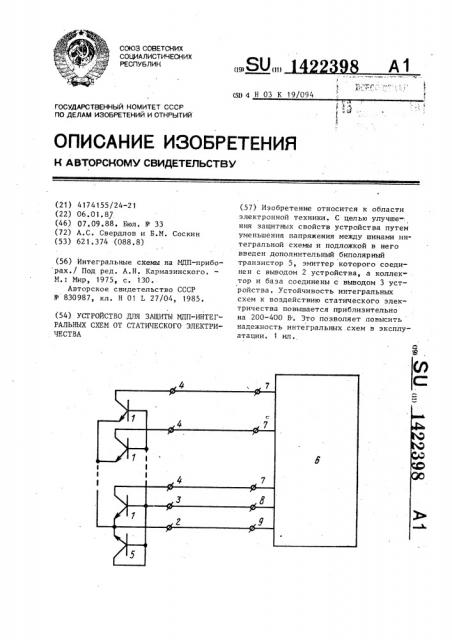

На чертеже представлена схема уст. ройства для защиты МДП-интегральных

:схем от статического электричества.

Устройство содержит биполярные транзисторы 1, первый вывод 2 устройства, соединенный с эмиттерами транзисторов 1, второй выход 3 устройст- 2(1

:ва, соединенный с базами транзисторов

1, выводы 4 коллекторов соответствую:щих транзисторов 1, дополнительный биполярный транзистор 5, эмиттер кото

:рого соединен с выводом 2 устройства, 25 а коллектор и база — с выводом 3 устройства. Устройство соединено с интегральной схемой 6. Каждый из защищаемых выводов 7 ИС соединен с одними из выводов 4. Вывод 8 подложки ЗО соединен со вторым выводом 3 устройства, а общая шина 9 ИС вЂ” с первым выводам 2 устройства.

Устройство работает следующим образом. 35

При воздействии статического электричества между выводами 7 и 9 относительно вывода 8 происходит смыкание эмиттера и коллектора транзистора 5.

Ток последнего ограничивает дальнейшее возрастание напряжения между выводами 9 и 8 ИС. Благодаря этому нарастанке напряжения на выводе 7 вызывает смыкание эмиттера и коллектора соответствующего транзистора 1, что ограничивает дальнейшее нарастание напряжения на выводе 7.

Поскольку падение напряжения на транзисторе 5 в режиме вторичного пробоя достигается короткой базой транзистора 5, меньшей напряжения пробоя обратно смещенного р — п перехода (имеет место в известном устройстве, где отсутствует транзистор 5), достигается снижение напряжения на общей шине по отношению к подложке, что улучшает защиту от пробоя внутренних транзисторов ИС, истоки которых соединены с общей шиной. Это наряду с защитой затворов входных транзисторов улучшает качество защиты от воздействия статического электричества ° .

Устройство для защиты МДП-интегральных схем от статического электричества, содержащее биполярные транзисторы по числу защищаемых выводов интегральной схемы, эииттеры которых соединены с первым выводом устройства, их базы — с вторым выводом устройства, а коллекторы соединены с остальными соответствующими выводами устройства, о т л и ч а ю щ е е с я тем, что, с целью улучшения защитных свойств устройства путем уменьшения напряжения между первым и вторым выводами, в него введен дополнительный биполярный транзистор, эмиттер которого соединен с первым выводом устройства, а коллектор и база соединены с вторым выводом устройства.