Ассоциативное суммирующее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в вычислительньк устройствах для одновременного суммирования многих чисел, представленных как в двоичной, так и в двотпю-десятичной системе счисления. Целью изобретения является повышение быстродействия и упрощение конструкцшт устройства. Устройство содержит ассоциативный запоминающий блок 1, группы элементов И 2, 3, группу элементов задержки 4, элемент И 5, группу регистров 6 сдвига , регистр 7 хранения пефеноса, регистр 8 промежуточного результата, группу элементов И 9, постояпньш запоминающий блок 10, входы 11 операндов , выходы 12, 13 результатов двоичного и десятичного сумм1фования, шины 14, 15 синхронизации. В устройстве реализуются процессы подсчета числа единиц в разрядных срезах и сумм1фование полученных кодов со сдвигом во времени на одном ассоциативном запоминающем блоке. 2 табл., 3 ил. с (/)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 4 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4165174/24-24 (22) 23.12 ° 86 (46) 15.09.88. Бюл. У 34 (71) Дагестанский политехнический институт (72) М.-M.À.Èñìàèëîâ, И.А.Айдемиров, А.А.Зурхаев и И.А.Магомедов (53) 68 1.325.5 (088.8) (56) Авторское свидетельство СССР

0- 1062689, кл. G 06 F 7/50, 1982.

Авторское свидетельство СССР

У 1233134, кл. С 06 F 7/50, 1984 ° (54) АССОЦИАТИВ HOF СУММИРУНМЦЕЕ УСТРОЙСТВОО (57) Изобретение относится к области вычислительной техники и может быть использовано в вычислительных устройствах для одновременного суммирования многих чисел, представленных как в

ÄÄSUÄÄ 1424011 А1 двоичной, так и в двоично-десятичной системе счисления ° Целью изобретения является повышение быстродействия и упрощение конструкции устройства. Устройство содержит ассоциативный запоминающий блок 1, группы элементов И

2, 3, группу элементов задержки 4, элемент И 5, группу регистров 6 сдвига, регистр 7 хранения переноса, регистр 8 промежуточного результата, группу элементов И 9, постоянный запоминающий блок 10, входы 11 операндов, выходы 12, 13 результатов двоичного и десятичного суммирования, шины

14, 15 синхронизации. В устройстве реализуются процессы подсчета числа единиц в разрядных срезах и суммирование полученных кодов со сдвигом во времени на одном ассоциативном запоминающем блоке. 2 табл., 3 ил.

1424011

1:= n + log,N . — ко.пг ество затрачиваемых тактов, за которые вычисляется сумма, где

11зобретс.ние относится к вычислительной технике и может быть использовано в вычислительных устройствах для эдновременпого суммирования многих висел, представленных как в дво5 и ной, так и в двоично-десятичной сиc TOM счисления.

Целью изобретения является повышение быстродействия и упрощение конструкции устройства.

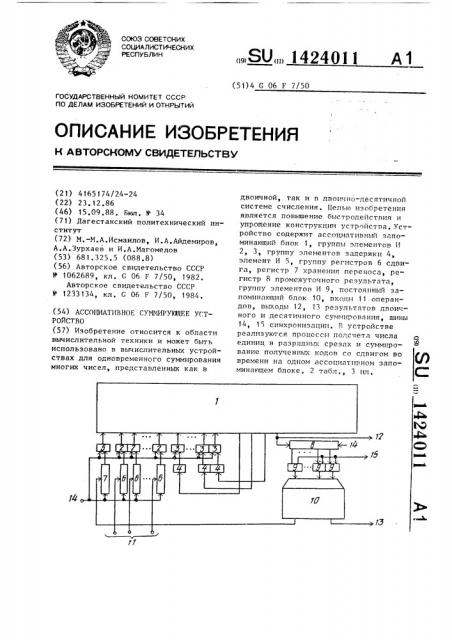

На чертеже представлена функциональная схема устройства. у.тройство содержит ассоциативный запомина|ощий блок 1, группы элементов

И 2, 3, группу элементов 4 задержки, элемент И 5, группу регистров 6 сдвига, регистр 7 хранения переноса, регистр 8 промежуточного результата, группу элементов И 9, постоянный запоминающий блок 10, входы 11 операн20 дов, выход 12 результата двоичного

o";ò èðonëí è, выход 13 результата десяти нс го суммирования, шины 14,15 синхронизации. 25

Устройство работает следующим обре sn q

11,,in,;t÷ 11 п зависимости от того, в кн;ом виде подаются слагаемые (в двоичном ини двоично десятичном) по30 ступ, нт и записt. ваются в регистры 6 глнг, емые полностью (в первом случае)

1пи .i |-ред тле тетрады всех слагаемых (во этором случае).

Р,1с-.мотрим работу устройства, когда с;:raew ñ прсдставленьt в двоичной 35 спет< ме с п сления (табл.1). !

11и подаче тактового импульса на шину 14 на первые входы элементов И

2 нодаютсн одноименные разряды слагаемых. 1:формированное слово является 40 ч.- от ю ассоциативного признака, подана .мого на входы блока 1. Остальной

Icl(т,.ю асс нц1атчвного при 3iIQKQ является слово, считываемое пз блока 1, которое задерживается на один такт при uouo fJI элементов 4 задержки. В первом такте работы слово, считываемое )tç блока 1, равно "00...0" (2).

11а вьгходе получается результат суммирования в последовательном коде, 50 причем количество тактов, за которое выпи.ляется сумма, равно

n — разрядность двоичных чисел, N — количество одновременно суммируемых чисел.

В двоично-десятичной системе счисления в коде 8-4-2-1 устройство работает следующим образом (табл.2).

Через входы 1 1 в регистры 6 поступают младшие тетрады всех слагаемых, Используя блоки, предназначенные для операции двоичного суммирования, а также шину 14, производим операцию двоичного сложения. Заметим при этом, что в регистре 7 содержатся нули.

После обработки младших тетрад в регистре 8 (в исходном состоянии он содержит нули) формируется первичная

/ двоичная сумма 81 1

При подаче первого тактового импульса на шину 15 происходит передача информации с регистра 8 через элементы И 9 на вход адреса постоянного запоминающего блока 10.

На вход блока 10 поступает информация с регистра 8 с учетом переноса из предыдущих тетрад (при сложении младших тетрад таких переносов нет) .

С выхода блока 10 по соответствующему адресу считывается слово, которое содержит два вида информации, а именно выделяет цифру результата в двоично-десятичном коде и код переноса.

11олученная информация в двоичнодесятичном коде поступает на выход

13 и входы регистра 7 (количество переносов, которые необходимо учесть при суммировании вторых тетрад всех слагаемых). Регистр 7 является регистром сдвига. Обработка последующих тетрад всех слагаемых происходит аналогично.

Формула и з о б р е т е н и я

Ассоциативное суммирующее устройство, содержащее ассоциативный запоминающий блок, три группы элементов

И, элемент И, группу элементов задержки, регистр хранения переяоса, группу регистров сдвига, регистр промежуточного результата и постоянный запоминающий блок, причем вход младшего разряда регистра промежуточного результата соединен с выходом результата ассоциативного запоминающего блока и с выходом результата двоичного суммирования устройства, выходы разрядов регистра промежуточного результата соединены с первыми входами

1424011 элементов И первой группы, выходы которых подключены к адресным входам постоянного запоминающего блока, первый выход которого соединен с выходом результата десятичного суммирования

5 устройства, остальные выходы постоянного запоминающего блока соединены с входами разрядов регистра хранения переноса, выход которого подключен к первому входу элемента И, второй вход которого соединен с первой шиной синхронизации устройства и тактовыми входами регистров сдвига группы и регистра хранения переноса, входы разрядов каждого регистра сдвига группы соединены с входами разрядов соответствующего операнда устройства, выходы регистров сдвига группы соединены с первыми входами элементов И второй группы, вторые входы которых подключены к первой шине синхронизации устройства, выходы ассоциативного sanoминающего блока соединены через соответствующие элементы задержки группы с первыми входами элементов И третьей группы, выходы которых подключены к первым входам признака ассоциативного запоминающего блока, вторые входы элементов И первой группы соединены с второй шиной синхронизации устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и упрощения конструкции, выходы элементов И второй группы соединены с вторыми входами признака ассоциативного запоминающего блока, выход элемента И подключен к третьему входу признака ассоциативного запоминающего лоха, тактовый вход регистра промежуточного реэультата соединен с первой шиной синхронизации устройства

1424011

Т а блиц

О О

О О

О О

О О

О 1

О 0

О 1 О

О 1 О

О 1

О 1

О 0

О 1

1 О 0i1

О, О 1

О 1

О 1

О ; 1

0 0 0

1 О О о (о

О 1

О 1

О 1

О 1 реносов 7

О 0,1 1

0 1i0 О

С бло" С вых. ка эл-в входных ИЗ регистров В и сблока P хранения переноса

На На вход вход Р промеэл-в жуточного

4 реэультата 8

Таблица 2

В Pr Выход устхране- ройства 13 ния пе