Устройство для функционального контроля цифровых интегральных схем

Иллюстрации

Показать всеРеферат

Изобретение относится к контрольно-измерительной технике и может быть использовано в устройствах контроля динамического функционирования цифровых интегральных схем. Устройство содержит блок 1 аналоговых компараторов , D-триггеры 7 и 8, триггеры 4 и 5 памяти, выходной триггер 6, блок 9 задержки, блок 10 коммутации. Введение блока.23 коррекции, D-триггеров 21 и 22 и входной клеммы 27 исключает возможность неоднозначной работы триггеров, следовательно, отсутствует зона неопределенного соетояния узлов устройства. 2 ил. /л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (z) 4 С 01 R 31/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (!

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4223224/24-21 (22) 07. 04.87 (46) 15.10.88. Бюл. У 38 (71) Научно-исследовательский и конструкторско-технологический институт средств контроля электронной аппаратуры и изделий электронной техники (72) В.В.Данилов, Г.И.Лобанов и В.С.Пункевич (53) 621.317. 799 (088.8) (56) Ерлашев В.П., Носачев В.М.

Система контроля динамического функционирования больших интегральных схем. — Электронная техника, Сер. 8, 1980, вып. 5(83), с.110-114, рис.2.

Авторское свидетельство СССР

У 1109687, кл. G 01 R 31/28, 1983.

„„SU„„1430915 А 1 (54) УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО

КОНТРОЛЯ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ CXEM (57) Изобретение относится к контрольно-измерительной технике и может быть использовано в устройствах контроля динамического функционирования цифровых интегральных схем. Устройство содержит блок 1 аналоговых компараторов, D-триггеры 7 и 8, триггеры 4 и 5 памяти, выходной триггер 6, блок

9 задержки, блок 10 коммутации. Введение блока 23 коррекции, D-триггеров 21 и 22 и входной клеммы 27 исключает возможность неоднозначной работы триггеров, следовательно, отсутствует эона неопределенного состояния узлов устройства. 2 ил.

1430915

Изобретение относится к контрольно-измерительной технике и может быть использовано в устройствах контроля динамического функционирования цифровых интегральных схем (ИС) и больших интегральных схем (БИС).

Цель изобретения — повышение достоверности контроля цифровых ИС с высокими рабочими частотами за счет исклю10 чения возможности неоднозначной работы триггеров и, следовательно, отсутствия зоны неопределенного состояния узлов устройства.

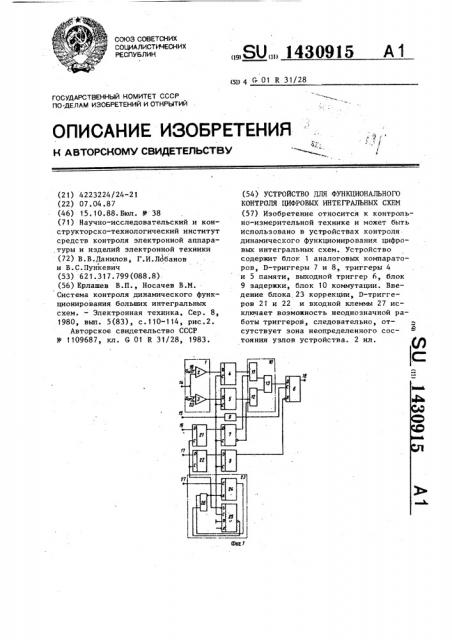

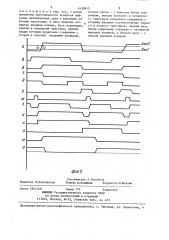

На фиг.1 изображена функциональ- 15 ная схема устройства для функционального контроля ИС по одному выводу, на фиг.2 — временные диаграммы, поясняющие работу устройства (диаграммы приведены для случая установки строба на 20 значение, равное периоду контроля).

Устройство содержит блок 1 аналоговых компараторов, выполненный на усилителях 2 и 3, триггеры 4 и 5.памяти, выходной триггер 6, Д-триггеры 25

7 и 8, блок 9 задержки, блок 10 коммутации, выполненный на элементах

И 11 и 12 и KIN 13, клемму 14 для подключения объекта контроля, входные клеммы 15-17, выходную клемму 18, источники l9 (1, „1 ) и 20 (U „2) опорных напряжений, D-триггеры 21 и 22, блок 23 коррекции, выполненный на триггерах 24 и 25 и элементе

И-НЕ 26, и входную клемму 27. Первые входы усилителей 2 и 3 блока 1 аналоговых компараторов соединены с клеммой 14 для подключения испытуемой

ИС, вторые входы усилителей 2 и 3 разделЬно соединены с источниками 40

19 и 20 опорных напряжений, задающих программируемые значения "1" и "0" соответственно, выходы усилителей

2 и 3 раздельно соединены с первыми входами триггеров 4 и 5 памяти, вторые входы которых соединены,с входной клеммой 15, входом блока 9 задержки, первыми входами D-триггеров 7 и 8. Выходы триггеров 4 и 5 раздельно соединены с первыми входами логических элементов И 11 и 12, образующих первый и второй входы блока 10 коммутации, выходы триггера 7 раздельно соединены с вторыми входами этих элементов, образующими третий и четвертый входы блока 10 коммутации.

Первый вход выходного триггера 6 сое- динен с выходом блока 10 коммутации, второй вход выходного триггера 6 соединен с выходом триггера 8, а третий вход триггера 6 — с выходом блока 9 задержки. Первые входы триггеров 21, 22 раздельно соединены с входными клеммами 16 и 17. Входная клемма 16 служит для подключения источника эталонной информации (не показан), входная клемма 17 — для подключения источника управляющих сигналов (не показан). Вторые входы дополнительных триггеров 2 1 и 22 подключены к выходу блока 23 коррекции, соединенного также с первыми входами триггеров 24 и 25 и выходом элемента И-НЕ 26. Выходы триггеров 2 1 и 22 соединены с вторыми входами триггеров 7 и 8.

Первый вход блока 23 коррекции, образованный вторым входом триггера 24, подключен к входной клемме 27, служащей для подключения источника тактовых импульсов контроля (не показан), по которым производится выдача эталонной информации и управляющих сигналов каждого периода контроля.

Второй вход блока 23 коррекции,образованный вторым входом триггера 25, подключен к входной клемме 15 устройства.

Первый и второй входы элемента

И-НЕ 26 блока ?3 коррекции соединеI ны соответственно с неинвертирующим выходом триггера 24 и инверсным выходом триггера 25, на третий вход которого подается "0", а четвертый вход используется для начальной установки. Усилитель 2 конструктивно объединен с триггером 4 памяти и выполнен на микросхеме 597СА1 с инверсией по стробирующему входу, триггеры 6-8, 21, 22, 24,25 выполнены на микросхемах 500ТИ231, блок 10 коммутации — на микросхеме 500ЛК117, блок 9 задержки — на микросхемах серии 500 (например 500ЛП116), элемент И-НЕ 26— на микросхеме 500ЛМ105.

Устройство при контроле ИС по одному выводу работает следующим образом.

На входную клемму 14 устройства поступает выходной сигнал с испытуемой

ИС с заданной частотой контроля (фиг.2а). В блоке 1 аналоговых компараторов выходные сигналы ИС сравниваются с уровнями "1" и "0", задаваемыми источниками 19 и 20 опорных напряжений. На входную клемму 16 и,следовательно, на первый вход триггера

21 поступает сигнал эталонной информа1430915 ции (фиг. 2б), на входную клемму 17 (первый вход триггера 22) постоянно поступает сигнал разрешения контроля, разрешающий работу выходного тригге5 ра 6. По достижении контролируемым сигналом уровня "0" (фиг.2а, момент времени t<) срабатывает усилитель 3 блока 1 аналоговых компараторов и на его выходе формируется сигнал, пока- 1р занный на фиг.2в). Аналогично в момент времени t< срабатывает усилитель 2 (фиг.2 г).

На входную клемму 27 — второй вход триггера 24 блока 23 коррекции, поступают тактовые импульсы, обозначающие начало каждого периода контроля (фиг.2 д). Выход триггера 24 устанавливается в "1" по переднему фронту тактового импульса. Выход триггера 25 20 устанавливается в "1" по переднему фронту строб-импульса, поступающего на клемму 15 (фиг.2е) или по сигналу начальной установки, подаваемому перед началом работы. При поступлении 25 первого тактового импульса на выходе триггера 25 присутствует "1", на выходе триггера 24 устанавливается

"1" и на выходе элемента И-HE 26 формируется передний фронт скорректированного тактового импульса первого периода контроля (фиг.2 ж). При этом выходы триггеров 24 и 25 (фиг.2з, 2и) устанавливаются в "0", на этом заканчивается формирование скорректированного тактового импульса.

По переднему фронту скорректированного импульса в триггеры 21 и 22 (фиг.2 к) заносится эталонная и уп- 40 равляющая информация с клемм 16 и 17 для первого такта контроля, При поступлении второго тактового импульса выход триггера 24 вновв устанавливается в 1, а выход триггера 25 про- 45 должает оставаться в "0". По стробимпульсу первого такта контроля выход триггера 25 устанавливается в

"1" и просходит форьырование второго скорректированного импульса на выходе элемента И-НЕ 26 (фиг.2 ж). По переднему фронту строб-импульса первого такта происходит перепись информации с триггеров 2,1 и 22 на триггеры 7 и 8 (фиг.2 л) и запоминание на триггерах 4 и 5 (фиг.2 м, о) состояния

55 на выходе компараторов 2 и 3. По второму скорректированному тактовому импульсу на триггеры 21 и 22 записывается эталонная и управляющая информации для второго такта контроля.

Выходные сигналы, поступающие с прямого и инверсного выходов триггера 7 (эталонная информация) на входы блока 10 коммутации, разрешают прохождение сигналов с выходов триггеров

4 и 5 па взяти на вход выходного триггера 6. Выходная информация с выхода блока 10 коммутации посредством задержанного в блоке 9 строб †импульса переписывается в триггер 6, при сигнале разрешения с выхода триггера 8. Если контролируемая импульсная последовательность сигналов совпадает по своим уровням с заданными значениями "0" и "1", а также соответствует своему ожидаемому местоположению, фиксируемому строб-импульсом, то на выходе триггера 6 сигнал отсутствует. Это означает, что контролируемая ИС является годной. В противном случае на выходе триггера 6 формируется сигнал, означающий неисправность контролируемой ИС. формула изобретения

Устройство для функционального контроля цифровых интегральных схем, содержащее блок аналоговых компараторов, первый и второй триггеры, два триггера памяти, выходной триггер, блок задержки, блок коммутации, три входных и выходную клеммы, клемму для подключения объекта контроля, вход блока аналоговых компараторов соединен с клеммой для подключения объекта контроля, а выходы раздельно соединены с первыми входами тригге,ров памяти, вторые входы которых соединены с входом блока задержки и первой входной клеммой, выходы триггеров. памяти раздельно соединены с первым и вторым входами блока коммутации, третий вход которого соединен с неинвертирующим выходом первого триггера, а выход — с первым входом выходного триггера, соединенного своим выходом с выходной клеммой устройства, первые входы первого и второго триггеров соединены с первой входной клеммой, инвертирующий выход

Г первого триггера соединен с четвертым входом блока коммутации, выход блока задержки — с вторым входом выходного триггера, третий вход которого соединен с выходом второго триггера, о т143091

ЙтР

IlonI

Составитель А.Коробков

Техред Л.Олийнык Корректор М.Шароши

Редактор Л.Пчолинская

Заказ 5341/49 Тираж 772 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 личающеесятем, что, с целью повышения достоверности контроля цифровых интегральных схем с высокими рабочими частотами, в него введена четвертая входная клемма, блок коррекции, третий и четвертый триггеры, первые входы которых раздельно соединены с второй и третьей входными клеммами, 5

6 вторые входы — с выходом блока коррекции, выходы третьего и четвертого триггеров раздельно соединены с вторыми входами соответственно первого и второго триггеров, первый вход блока коррекции соединен с четвертой входной клеммой, а второй вход — с первой входной клеммой.