Устройство для обработки логической информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для обработки нечеткой логической информации. Целью изобретения является, расширение функгрюнальных возможностей устройства за счет обработки нечеткой логической информации . Устройство для обработки нечеткой логической информации содержит информационные входы 1 и 2 устройства , выход 3 устройства, первый настроечный вход 4 устройства, второй настроечный вход 5 устройства, дешифраторы 6 и 7 кода, блок 8 поразрядных логических операций, регистр 9, сдви гатель 10, шифратор 11 кода, третий настроечный вход 12 устройства. На ; информационные входы ус ;оройстзз подаются значения неч.е гк1-1Х логических переменных, дешифраторы преобразуют полученную информацию в унитарный : код, блок поразрядных логических опереализует поразрядные логические функции, получанный .результат преобразуется на шифраторе в двоичный код, который является результатом логической обработки нечетт.шх переменных. 3 з.п. ф-лы, 4 ил. I

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (51)4 G 06 F 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

О

Г"

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

Il0 ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4260224/24-24 (22) 11.06.87 (46) 23. 12.88. Бюл. В 47 .(71) Дагестанский политехнический институт (72) И ° À.Айдемиров (53) 681.3(088.8) (56) Авторское свидетельство СССР

Ф 941994, кл. G D6 F 7(00, 1980.

Дроздов Е.А., Комарницкнй В.А., Пятибратов А.П. Электронные вычислительные машины. M.: Машиностроение, 1976, с. 230-231. (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЛОГИЧЕСКОЙ ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может бытЬ исгользовано для обработки нечеткой логической информации. Целью изобретения является. расширение функциональных возможностей устройства за счет обраÄÄSUÄÄ 1446616. ботки нечеткой логической информации. Устройство для обработки нечеткой логической информации содержит информационные входы 1 и 2 устройства, выход 3 устройства, первый настроечный вход 4 устройстна, второй

I настроечный вход 5 устройства, дешифраторы 6 и 7 кода, блок 8 поразрядно логических операций, регистр 9, сдвигатель 10, шифратор 11 кода, третий настроечный вход 12 устройства. На информационные входы устройства подаются значения нечетких логических переменных, дешифраторы преобразуют полученную информацию в унитарный код, блок поразрядных логических операций реализует поразрядные логические функции, полученный, результат преобразуется на шифраторе в двоичный код, который является результатом логической обработки нечет":.,их переменных. 3 з.п. ф-лы, 4 ил.

1446616

Изобретение относится .к вычислительной технике и может быть использовано для обработки нечеткой логической информации.

Целью из о бр е т ения я вля ет ся р асширение функциональных воэможностей устройства за счет обработки нечет, кой,.(многозначной) логической информации. 10

Логическая обработка нечеткой информации основана на следующем теоретико-множественном эквиваленте нечетных множеств.

Пусть U = fx 1- (конечное или счет- 15 ное) — универсум; V = (1) — некоторая система его подмножеств, называемых элементарными, таких что o(Ф О, U g = U, все о(конечны.

X Y < U обобщенно равны, если

М pt C V: I ol A X I = I A A Y l. Х обобщен но включает Y если МЫ е V: l n XI

4 I d A Y I. Тогда. множество пар Х =

= с, td.n Х !. i I a u X I = Ф 3 задает 25 класс множеств, обобщенно равных множеству Х. Множеству Х соответствует определенная на V функция Мх()=

=)Ы n x !. нормированная по Ie(1, она может рассматриваться как функция совместимости (p (Ы) = Nx(ol)/ И() нечеткого множества Х V, где - символ нечетного включения (множество Х пар (Ы, (dnХ I > есть обобщенное описание множества Х или просто обобщенное множество). Если во всех па35 рах заменить Mx(d) = Ы0 Х I на ! х(Ы) = Ып Х !/ I (, ту Х превратится в нечеткое множество 3!И,Р„(e<)7).

Такое построение нечетного множества сводит. само это понятие (нечеткое множество)- к некоторой структуре обычных множеств, что позволяет и логическую обработку нечетких (многозначных) логических переменных свести к обработке соответствующих структур двоичных переменных.

Основными логическими операциями над нечеткими переменными являются определение максимума (нечеткая, или многозначная дизъюнкция), мини50 мума (нечеткая или многозначная конъюнкция), дополнение (до единицы или другого максимального значейия, принимаемого переменной, — нечеткая или многозначная инверсия).

Любая логическая переменная (многозначная или двоичная) является предикатом принадлежности некоторому множеству, т.е. выражением вида

Элемент х принадлежит (не принадлежит) множеству Х", причем если Х— обычное множество, это выражение мо-. жет быть истинным или ложным, а если Х вЂ” нечеткое множество, степень истинности этого выражения может меняться от О до 1.

Нечеткое множество Х 5 Ч строится с помощью обычных множеств Ы Б Ч, это дает возможность заменить многозначную логическую переменную (выражение "Элемент принадлежит нечеткому множеству Х") множеством двоичных логических переменных (множеством выражений "Элемент х принадлежит множеству Ы и множеству Х"), причем общее количество двоичных переменных равно Id!, а количество истинных — величине Mx(d). При этом, поскольку при нечетком или обобщенном описании важно лишь количество истинных и ложных значений переменных можно задавать этим переменным истинные значения произвольным образом, сохраняя лишь их количество, т.е. нечеткая обработка множества двоичных переменных включает их

"обезличивание". Ниже приведены этапы такой обработки, где для обезличи вание -двоичных переменных выполняется упорядочение их истинных значений путем сдвига всех единиц в одну, а всех нулей — в другую сторону.

1, Заменить нечеткую (многоэнач-. ную) логическую переменную вектором двоичных логических переменных с количеством компонент, на единицу меньшим количества различных значений, принимаемых многозначной переменной.

2. Согласно степени истинности многозначной логической переменной присвоить соответствующим разрядам вектора единичное значение.

3. Нечеткие дизъюнкция и конъюнкция заменяются поразрядными дизъюнкцией и конъюнкцией построенных векторов. Нечеткое отрицание заменяется поразрядным отрицанием с последующим упорядочением результирующего вектора, которое состоит в сдвиге единичных разрядов в крайние правые, а нулей — в левые позиции (поскольку перечисленные операции составляют функциональный полный базис, все прочие логические операции над нечеткими (многозначными) переменными сво55

3 14466 дятся к последовательному применению перечисленных).

4. Значение результирующей нечеткой (многозначной) переменной равно количеству единиц в результирующем

5 двоичном векторе.

Любая логическая информация (т.е. любые булевы векторы) может быть подвергнута нечеткой обработке. Поскольку при этом важна лишь количественная характеристика этой информации (количество истинных и ложных . значений в соответствующих булевых векторах), то можно заменить исходные векторы любыми другими с тем же количеством истинных и ложных значений (сдвигом всех единиц в одну, а всех нулей — в другую сторону). Полученные в результате векторы, обобщенно равные исходным, подвергаются логической обработке, причем если на каком-либо шаге упорядоченность истинных и ложных значений компонент обрабатываемых векторов нарушается, 25 ее необходимо восстановить (сдвигом всех единиц в одну, а всех нулей— в другую с орону).

Результатом такой нечеткой обработки булевых векторов является век- ЭО тор с соответствующим количеством единиц и нулей, При различных спосо— бах упорядочения истинных и ложных значений в исходных векторах (и промежуточнщс) результирующие векторы

35 имеют также различное распределение единиц и нулей, однако количество их (как раз и являющееся результатом нечеткой обработки) будет одним и . тем же, .т.е. эти результирующие векторы будут обобщенно равными.

Таким образом, обеспечивается обработка как исходной нечеткой (многозначной) логической информации, так и четкой информации, представленной булевыми векторами.

Рассмотрим в качестве примера выполнение нечетких дизъюнкции, конъюнкции и отрицания над восьмеричными переменными А и В, представленными трехраэрядными двоичными числами.

Пусть А = 4 = 1001,. В = 6 110 .

АМВ = max(A,В)=В=6110, АЛВ = min(A,Â) А=.4=100д А=7 — А=3=011 ° ,Представим переменные А и В булевыми векторами с соответствующим количеством истинных и ложных зиаЧений:

16

А - (0001111);

В (0111111)

Поразрядная дизъюнкция этих векторов совпадает с вектором В, имеющим большее количество истинных значений. Поразрядная конъюнкция совпадает с вектором А: (0001111) v (0111111) = (0111111}В =

= 6; (0001 1.11) л (0111111) = (0001111) A

4.

Поразрядная инверсия вектора А дает 1(0001111) = (1110000). В этом векторе нарушено первоначальное упорядочение истинных и ложных значений, однако количество единиц равно тем. Чтобы результирующий вектор мог быть подвергнут дальнейшей обработке, а также для правильного его декодирования, он должен быть заново упорядочен (1110000) (0000111).

Упорядочение сводится к транспор тированию полученной информации.

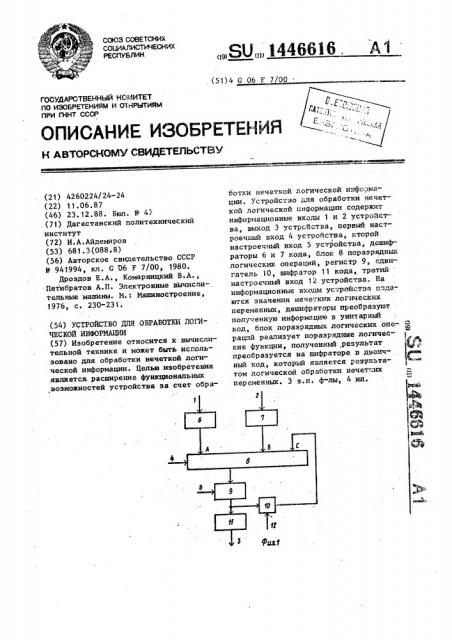

На фиг. 1 представлена функциональная схема устройства для обработки нечеткой логической информации; на фиг. 2 — схема дешифраторов кода; на фиг. 3 - схема шифратора кода; на фиг. 4 — схема сдвигателя.

Устройство для обработки нечеткой логической информации (фиг. 1) содержит первый информационный вход,3 устройства, второй информационньй вход 2 устройства, выход 3 устройст- . ва, первый настроечный вход 4 устройства, второй настроечный вход 5 устройства, дешифраторы б,и 7 кода, блок 8 поразрядйых логических операций, регистр 9, сдвигатель t0 шифратор 11 кода, третий настроечный вход 12 устройства.

Дешифраторы кода (фиг. 2) содержат дешифратор 13 и группу элементов

ИЛИ 14 ° 1-14.п.

Шифратор кода (фиг. 3) содержит шифратор 15, группу элементов ИЛИ

16.1-16.п и группу элементов ЗАПРЕТ

1 7. 1-1 7. n+1.

Сдвигатель 10 (фиг. 4) содержит .элементы ЗАПРЕТ 18.1-18.п, И 19i1"

19.п, элементы ИЛИ 20.1-20.п.

Устройство для обработки логической информации работает следушщим----; образом.

Значения нечетких (многозначных) логических переменных в виде двоичных чисел (целых беэ знака) подают5 1446 ся на первый и второй информационные входы 1 н 2 устройства. Дешифраторы

6 и 7 кода преобразуют входной двоичный код в унитарный (колнчество единиц равно значению кода на входе дешифратора, причем все единицы занимают правые, а все нули — левые позиции). Блок 8 поразрядных логических операций в зависимости от ко- 10 да операций на первом настроечном входе 4 устройства реализует поразрядные логические функции (дизъюнкцию, конъюнкцию, отрицание, передачу кода) над соответствующими разряда 15 ми кодов, полученный результат записывается в регистр 9. Сдвигатель 10 под управлением третьего настроечного входа 12 устройства выполняет единиц вправо. Шифратор 11 да преобразует унитарный код на выходах регистра 9 в двоичный код. Код на выходе 3 устройства является значением нечеткой логической переменной — результата логической обработ- 25 ки нечетких (многозначных) переменныхэ

Пусть, например, первый или вто-. рой информационные входы 1 и 2 устройства четырехразрядные, следова.тельно, нечеткие логические переменные принимают значения от 0 до 15.

Пусть на первый информационный вход

:1 поступает код 1010 (число десять), а на второй вход 2 — код 01 10у {чис35 ло шесть), над которыми необходимо выполнить многазначную логическую операцию.

С (АЛВ), где А = 10, В = 6, С вЂ” результат 40 ,операции:

С = 15 — min(AB} = 9.

Дешифраторы б и 7 кода имеют по

15 выходов, на выходе дешифратора б кода образуется код с десятью д - 45 ницами (справа) и пятью нулями (слева), на выходе дешифратора 7 кода— код с шестью единицами (справа) и девятью нулями (слева).

На первый настроечный вход 4 устройства поступает вход выбора поразрядной конъюнкции, s результате которой на выходе блока 8 поразрядных логических операций образуется код с шестыа единицами (справа} и девятью нулями (слева), эанисываемый в регистр 9. Поскольку этот код не имеет нулей, расположенных правее единиц на третий. настроечный вхадi12

616 6 устройства подается сигнал, обеспечи, вающий передачу кода через сдвигатель

10 без изменений, а ца первый вход

4 устройства подается код выбора операции поразрядной инверсии входа

С, в результате чего на входе блока

8 поразрядных логических операций образуется код с девятью единицами (слева) и шестью нулями (справа), записываемый в регистр 9. Этот код имеет нули правее единиц, следовательно, его надо .сдвинуть на шесть разрядов вправо. Это выполняется сдвигателем. 10, который меняет местами левые и правые разряды кода при подаче соответствующего сигнала на третий настроечный вход. l2 устройства. На первый настроечный вход 4 подается сигнал, обеспечивающий передачу кода через блок 8 поразрядных логических операций с входа С без изменений. Этот код (теперь уже правильно упорядоченный) снова записывается в регистр 9. Теперь на входы шифратора 11 кода поступает код с девятью единицами справа, преобразуемый им в число 1001 (девять), которое и является результатом логической обработки многозначных переменных.

Формула изобретения

Устройство для обработки логической информации, содержащее блок поразрядных логических операций и регистр, причем информационные входы регистра соединены с выходами блока поразрядных логических операций, настроечный вход которого соединен с. первым настроечным входом устройстsa второй настроечный вход устройства соединен с управляющим входом регистра, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональнЫх воэможностей за счет обработки нечеткой логической информации, оно содержит два дешифратбра кода, сдвигатель и шифратор кода, причем первый информационный вход устройства соединен с входом первого дешифратора кода, выход которого соединен с первым информационным входом блока поразрядных логических операций, выход которого соединен с информационным входом регистра, выход которого соединен с входами шифратора кода и информационными входа7 1 ми сдвигателя, выход которого соединен с вторым информационным входом блока поразрядных логических операций, второй информационный вход устройства соединен с входом второго дешифратора кода, выход которого соединен с третьим и формационным входом блока поразрядных логических операций, третий настроечный вход устройства соединен с управляющим входом сдвигателя, выход шифратора кода является выходом устройства, 2. Устройство по п. 1, о т »» и— ч а ю щ е е с я тем, что дешифратор кода содержит i-входовой дешифратор, i — количество обрабатываемых разрядов, и (n-1) элемент ИЛИ, n = 2, причем вход дешифратора кода соединен с входами дешифратора, первый вход (j-1)-го элемента ИЛИ соединен с j-м выходом дешифратора, j = 1,п, второй вход (n-1)-ro элемента ИЛИ соединен с шиной логического нуля, выход (j-1)-ro элемента ИЛИ соединен с вторым входом (j-2)-го элемента

ИЛИ и с выхсдом дешифратора кода.

3. Устройство по п. 1, о т л ич а ю щ е е с я тем, что шифратор кода содержит (n-1) элемент ИЛИ, и элементов ЗАПРЕТ, шифратор, причем

446616

8 первые входы элементов ИЛИ и первые входы (j-1)-го элемента ЗАПРЕТ соединены с входами шифратора кода, первьп» вход n-ro элемента ЗАПРЕТ соеди5 нен с шиной логической единицы, вторые входы первого элемента ИЛИ и первого элемента ЗАПРЕТ соединены с шиной логического нуля, вторые

10 входы -ro элемента ЗАПРЕТ и К-ro элемента ИЛИ соединены с выходом (K-1)-го элемента ИЛИ, К = 2, п-1, выходы элементов ЗАПРЕТ соединены с входом шифратора, выход которого является выходом шифратора кода.

4.- Устройство по п. 1, о т ич а ю щ е е с я тем, что сдвигатель содержит (n-1) элемент ЗАПРЕТ,(n-1) элемент И и (и-1) элемент ИЛИ, причем первые входы элементов И и первые входы элементов ЗАПРЕТ соединены с управляющим входом сдвигателя, выходы элементов ЗАПРЕТ соединены с первыми входами элементов ИЛИ, 25 вторые входы которых соединены с выходами элементов И, вторые входы которых соединены с входом сдвигателя, вторые входы j-го элемента ЗАПРЕТ соединены с (n-j)-м входом сдвигателя, выходы элементов ИЛИ являются выходом сдвигателя.

Фиг.2

1446616

Составитель В.Сорокин

Текред Л.Олийнык . Корректор И.Иаксимишинец

Редактор А.Ворович

Заказ 6748/53

Тираж 704 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4