Устройство для задержки цифровой информации с контролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой задержки информации. Целью изобретения Является повышение надежности устройства . Повышение -надежности достигается за счет хранения информации в каждой ячейке накопителя с максимально возможной для нее точностью, не зависящей от состояния остальных ячеек накопителя. При этом старшие разряды информационного слова по каждому адресу хранятся в ячейке накопителя 6 или 7, что определяется работоспособностью ячейки соответствующего накопителя. Признак, указывающий на положение старшей части слова для каждой ячейки накопителей 6 и 7, хранится в накопителе 8. 1 ил. G S

СОЕЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (191 (11) (Ю 4 G ll С 19 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4310457/24-24 (22) 28.09.87 (46) 28.02.89. Бюл. № 8

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ П(НТ СССР (72) В.Н.Лацин, Е.Л. Полин, А.В.Дрозд, В.П,Крапенко и В.А.Минченко (53) 68!.327.66(088.8) (56) Авторское свидетельство СССР № 556495, кл. G:.11 С 11/00, 1977.

Авторское свидетельство СССР

¹ 1383324, кл. С 11 С 9/00, 1987. (54) УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ ЦИФРОВОЙ ИНФОРМАЦИИ С КОНТРОЛЕМ (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой задержки информации. Целью изобретения является повышение надежности устройства. Повышение надежности достигается за счет хранения информации в каждой ячейке накопителя с максимально возможной для нее точностью, не зависящей от состояния остальных ячеек накопителя. При зтом старшие разряды информационного слова по каждому адресу хранятся в ячейке накопителя 6 или 7, что определяется работоспособностью ячейки соответствующего накопителя. Признак, указываюший на положение старшей части слова для каждой ячейки накопителей 6 и 7, хранится в накопителе 8. 1 ил.

1462424

Изобретение относится к вычислительной технике и может быть исполь- зовано в устройствах цифровой,задержки информации.

Целью изобретения является повышение надежности устройства, заключающееся в том, что каждая ячейка накопителя хранит свою информацию с максимально возможной для данной

10 ячейки точностью, не зависящей от состояния остальных ячеек накопителя.

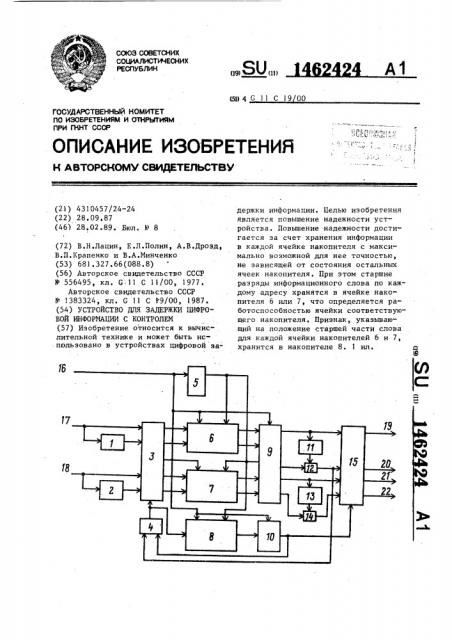

На чертеже приведена структурная схема устройства.

Устройство содержит первый 1 и второй 2 блоки свертки, входной коммутатор 3, элемент ИЛИ 4, счетчик 5 адреса, первый — третий 6 — 8 накопители, .выходной регистр 9, Э-триг" гер 10, третий блок 11 свертки, первый блок 12 сравнения, четвертый блок 13 свертки, второй блок 14 сравнения, выходной коммутатор 15, вход

16 синхронизации, информационные входы старших 17 и младших 18 разрядов, информационные выходы 19 и выходы 20. сигнала ошибки старших разрядов, информационные выходы 21 и выход 22 сигнала ошибки младших разрядов.

Устройство работает следующим об- 30 разом.

На информационные входы 17 и 18 устройства поступает последовательность информационных слов, сопровождаемая синхроимпульсами на входе 16 синхронизации устройства, причем во время первой половины такта происходит чтение информации иэ ячейки накопителя, записанной К тактов назад, а во время второй — запись информа46 ции в эту же ячейку, которая, в свою очередь, будет считана через К тактов. Величина задержки К определяется коэффициентом пересчета счетчика 5, который под воздействием синхроимпульсов последовательно переби45 рает адреса накопителей 6-8.

Старшие и младшие разряды записываются в накопители б и 7 вместе с соответствующими контрольными разрядами, которые вычисляются первым i и вторым 2 блоками свертки как сумма по модулю P. Считанная из накопите" лей информация вместе с контрольными разрядами записывается в выходной регистр 9.

Третий 11 и четвертый 13 блоки свертки вместе с первым 12 и вторым блоками сравнения вырабатывают сигналы об ошибках в старшем и младшем полусловах.

При отсутствии отказов в накопителях 6 и 7 входной 3 и выходной 15 коммутаторы передают на свои выходы информацию без перекоммутации, т.е, старшие разряды заносятся в накопитель 6, младшие — в накопитель 7.

После задержки старшие разряды поступают на выход 19 младшие — на выход 21 .

В случае отказа некоторой ячейки накопителя 6, в которой хранятся старшие разряды, на выходе первого блока 12 сравнения появится сигнал

"1", свидетельствующий об отказе, Этот сигнал будет записан. в следующем полутакте записи в третий, одноразрядный, накопитель 8. Одновременно с этим произойдет запись разрядов входного информационного слова по этому же адресу в накопители 6 и 7. Появление на управляющем входе входного коммутатора 3 сигнала "1" вызовет переключение коммутатора 3.

В результате старшие разряды слова будут записаны в ячейку второго накопителя 7, а младшие — в ячейку первого накопителя 6, где в предыдущем полутакте чтения по этому же адресу была обнаружена неисправность.

Таким образом, каждой ячейке накопителя 6 поставлена в соответствие ячейка одноразрядного накопителя 8 с таким же адресом, в которой хранится информация о работоспособности соответствующей ячейки накопителя 6. Если в ячейке накопителя 8 хранится ноль, то соответствующая ячейка накопителя.б исправна и в ней будут храниться старшие разряды, Если же в ячейке накопителя 8 хранится единица, то в соответствующей ячейке накопителя 6 существует неисправность и в нее будут заноситься младшие разряды, в то время как старшие разряды будут записаны в соответствующую исправную ячейку накопителя 7.

В этом случае при чтении в В"триггер 10 из накопителя 8 будет считываться единица, которая будет управлять переключением выходного коммутатора, для восстановления правильного .местоположения младших и старших разряцов. Кроме того, этот сигнал через элемент ИЛИ 4 будет управ" лять записью следующего слова в эту

3 14 же ячейку накопителей 6 и 7 в пере- коммутированном виде, т.е. вместо старших разрядов в накопитель 6 будут вновь записаны младшие разряды, Коммутаторы 3 и 15 коммутируют информацию вместе с соответствующими контрольными разрядами.

Таким образом, за счет введения в устройство задержки цифровой информации дополнительного накопителя элемента ИЛИ и D-триггера обеспечивается сохранение в устройстве старших разряд щ информации при возникновении отказа, что приводит к увеличению надежности устройства.

Формула и э обретения м

Составитель А.Яковлев

Техред М.Ходанич

Редактор О.Спесивых

Корректор С.Шекмар

Заказ 731/53 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,101

Устройство для задержки цифровой информации с контролем, содержащее четыре блока свертки, входной и выходной коммутаторы, счетчик адреса, первый и второй накопители, выходной регистр, два блока сравнения, причем счетный вход счетчика адреса соединен с входами управления записью/считыванием первого и второго накопителей, входом разрешения приема выходного регистра и является входом синхронизации устройства, выход счетчика адреса подключен к адресным входам первого и второго накопителей, е .информационные и контрольные входы первого и второго накопителей подключены к соответствующим выходам входного коммутатора, первый и второй информационные входы которого соединены с входами первого и второго блоков свертки соответственно и являются входами соответственно старших и младших разрядов информации устройства, выходы первого и второго блоков свертки соединены с соответствующими входами контрольных разря62424

4 дов входного коммутатора, информационные и контрольные выходы первого и второго накопителей подключены к соответствующим входам выходного регистра, первый и второй информационные выходы которого соединены с соответствующими входами выходного коммутатора и входами третьего и четвертого .блоков свертки соответственно, контрольные выходы которых соединены с соответствующими входами первого и второго блока сравнения, входы которых соединены с контрольными выходами выходного регистра, первый и второй информационные выходы выходного коммутатора являются выходами старших и младших разрядов информации устройства соответственно, о тл и ч а ю щ е е с я тем, что, с целью повышения .надежности, в устройство введены третий накопитель, элемент ИЛИ и D-триггер, причем адресный вход третьего накопителя соеди25 нен с соответствующими входами первого и второго накопителей, информационный вход третьего накопителя соединен с управляющим входом входного коммутатора и выходом элемента ИЛИ, второй вход которого соединен с управляющим входом выходного коммутатора и выходом D-триггера, информационный вход которого соединен с выходом третьего накопителя, а вход управления записью/считыванием соеди35 нен с соответствующими входами первого и второго накопителей, первый вход элемента ИЛИ соединен с выходом первого блока сравнения и первым

4О входом ошибки выходного коммутатора, . второй вход ошибки которого соединен с выходом второго блока сравнения, первый и второй выходы ошибки выходного коммутатора образует соответ45 ственно выходы сигналов ошибки старших и младших разрядов.