Оперативное запоминающее устройство с резервированием строк

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к резервированным запоминающим устройствам, изобретения повышение быстродействия устройства. В оперативное запоьшнающее устройство с резервированием строк, содержащее основной накопитель 1, резервный накопитель 2, основной дешифратор 3, резервный дешифратор 4, адресные формирователи 5, дешифратор 6, введены дополнительный столбец 10 элементов памяти и элементы И-НЕ 1 I. Перед работой программируется дешифратор 6 на выявление отказавших строк, а в элементы памяти дополнительного столбда 10, соответствующие отказавшим строкам, заносятся единицы, формирующие на выходах соответствуюцих элементов И-НЕ 11 сигнапы блокировки выходов основного адресного дешифратора 3. Сигналы с выходов дешифратора 6 через резервный дешифратор 4 подключают строку резервного накопителя 2. 2 ил. (

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

4 2426 А1 (51) 4 0 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4 ) 48815/24-24 (22) 19. 11. 86 — (46) 28,02,89, Бюл. ¹ 8 (72) В. В, Баранон, А.С, Березин, С, А, Королев, Е, М, Онищенко, П,Б,Попленин и С.A,Òðîøèí (53) 681.327,66(088.8) (56) Патент Сц)А № 4393474, кл, G 1 1 С 1 1/40, опубли к, 19 83.

Вернико вский Е. А, и др. Дефекты, выход годных и избыточность в БИС ЗУ,—

Зарубежная электронная техника, 1985, ¹- 10, с.20, (54 ) ОПЕРАТИВНОЕ ЗАПО)ЯНА)О)))ЕЕ УСТТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ СТРОК (57) Изобретение относится к вычислительной технике, в частности к резервированным запоьянающим устройствам, Цель изобретения — повышение быстроИзобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении, Целью изобретения является повьппе» ние быстродействия устройства.

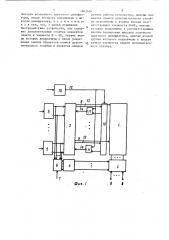

На фиг, ) изображена блок-схема устройства; на фиг, 2 — возможная реализация триггера на КМДП-транзистор ах °

Устройство содержит основной накопитель 1, резервный накопитель.2, основной адресный дешифратор 3, реэервдействия устройства, В оперативное запоминающее устройство с резернированием строк, содержащее основной накопитель 1, резервный накопитель 2, основной дешифратор 3, резервный дешифратор 4, адресные формирователи

5, дешифратор 6, введены дополнительный столбец )0 элементов памяти и элементы И-НЕ 11. Перед работой программируется дешифратор 6 на выявление отказ анших строк, а в элементы памяти дополнительного столбца 10, соответствующие отказавшим строкам, заносятся единицы, формирующие на выходах соответствующих элементов И-НЕ 11 сигналы блокировки выходов основного адресного дешифр атор а 3 ° Сигналы с выходов дешифратора 6 через резервный дешифратор 4 подключают строку резервного накопителя 2, 2 ил, ный адресный дешифратор 4, адресные формирователи 5, дешифратор 6, вход 7 программирования устройства, выходы

8 устройства, первую группу выходов

9 основного адресного дешифратора, дополнительный столбец 10 элементон памяти, элементы И-НЕ 11, вход 12 ре)кима работы устройства, вторую груп- ), пу выходов 13 основного адресного дешифратора 3 и входы 14 блокировки

Ъ. о сно вно го адр е сно го де шифр ат ор а 3.

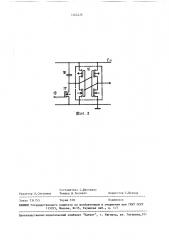

Кроме того, на фиг, 1 показан триггер

l5, Триггер 15 (фиг,2) может содержать бистабильную ячейку 16 на КМДПтранзи "торах, управляющий транзистор

146242

17 и, установочный конденсатор

1 g

Перед началом работы программируется дешифратор 6, Он может быть выrþëHeí в виде постоянной памяти, в которую заносятся адреса неисправных строк и запоминаются на постоянных запоминающих элементах с плавкими перемычками. Программирование осуществляется путем передачи напряжения программирования «s вход 7, После подачи напряжения питания на запрограммированное устройство обращение к нему некоторое время запрещена (на входе 12 поддерживается низкий уровень напряжения), Триггер 15 этоr р. жим обеспечивает следующим образам, Транзистор 1 7 э акрыт, Из-3 B на- 20 личия емкости конденсатора 18 бистабильная ячеика 16 установится в сос таяние "0", и на выходе триггера 15 буцет низкий уровень напряжения. .Зтor уровень поступит на первые входы 2 элементов И-НЕ 11, в результате чего

r=cp строки основного адреснога,цешифратора 3 окажутся незаблокированными, Сигнал с выхода триггера 15 также разрешает производить запись в элементы памяти дополнительного столбца

10, На адре сные входы устройства последовательно подаются адреса неисправных строк, в результате чего дешифратор 3 будет последовательно по35 давать на входы лементов памяти дополнител ьно ro столбца I О,, саответ ствующих неисправным строкам, сигналы вы б ар ки, Эл е менты п амя ти да пол ни т ел ьнаго столбца 10, на которые поступали выборки, переключат "я и установят на вторых входах соответствующих элементов И-НЕ 11 высокий потенциал. После перебора всех адресов неисправных строк на вход триггера 15 подается импульс положительной полярности, которой откроет транзистор 17, в результате чего зарядится емкость конденсатора 18, и бистабильная ячейка 16 переключится в состояние "1", На входе

12 установится высокий уровень напряжения, который в дальнейшем не изменится при любых изменениях на входе триггера 15 Высокий уровень на выходе триггера 15 запрещает< запись в элементы памяти дополнительного столб" ца 10 и устанавливает высокий уровень на первых входах элементов И-НЕ 11, В результате на. выходах элементов

4

И-HE 11, соответствующих неисправным строкам, установится низкий уровень., который поступит на входы блокировки этих строк основного адресного дешифратора 3, После этого разрешается обращение к устройству, Дальнейшая работа устройства осуществляется обычным образом, При поступлении на адресные входы исправной строки (данная строка дешифратора 3 не заблокирована) происходит выборка данной строки из основного накопнтеля 1, Дешифратор 6 выявляет, что обращение происходит к исправной строке и подает на резервный адресный дешифратор 4 сигнал запрещения выборки из резервного накопителя 2, При поступлении адреса неисправной строки основной дешифратор 3 не подает сигнала выборки данной строки основного накопителя 1, гак как на входе блокировки данной строки дешифратора 3 установлен низкий уровень. Дешифратор 6 по адресу, поступившему на вход, сформирует сигнал, поступающий на резервный адресныи дешифратор 4, Этот сигнал выбирает из резервного накопителя 1 строку, соответствующую неисправной строке основного накопителя 1, Таким образом, сигналы блокировки неисправных строк подаются на дешифратор 3 постоянно и независимо от адреса, поступающего на адресные входы, Поэтому отпадает необходимость подачи сигнала блокировки в каждом цикле выборки, Фар мул а изобретения

Оперативное запоминающее устройство с резервированием строк, содержащее основной накогмтель, адресные входы строк которого подключены к выходам первой группы основного адресного дешифр атор а, информационные входы которого подключены к информационным вхоцам дешифр атор а и выходам адресных формирователей, входы которых являются адресными входами устройства, информационные входы-выходы основного накопителя подключены к информационным входамвыходам резервного накопителя и являются информационными входами-выходами устройства, адресные входы строк резервного накопителя подключены к

3 )46 выходам резервного адреснога дешифратора, входы которого подключены к выходам дешифратора> о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия устройства, оно содержит дополнительный столбец элементов памяти и элементы И вЂ” HF. первые входы которых подключены к входу разрешения записи элементов памяти дополнительного столбца и являются входом

2426 6 режима работы устройства> выходы эле— ментов памяти дополнительного столбца подключены к вторым входам соответствующих элементов И-НЕ> выходы

5 которых подключены к соответствующим входам блокировки выходов основного адресного дешифратора, выходы второй группы которого подключены к входам записи элементов памяти дополнительно го стол бц а, Фиг. У

146 242б

Корректор С,Шекмар

Тираж 558

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раущская наб.9 д 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Редактор О,Спесивых

Заказ 731/53

Составитель С,йустенко

Техред N. Ходанич