Триггер на мдп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при разработке цифровых интегральных микросхем на МДП-транзисторах.Цель изобретения - повышение быстродействия триггера при сохранении потребляемой мощности. Триггер содержит инверторы 1 и 2 инверсного и прямого плеч соответственно состояндие из нагрузочных транзисторов 3, 4 обедненного типа и логических транзисторов 5, 6 обогащенного типа, входною имну 7, шину сигналов синхронизации 8, выходные шины 9, 10 инверсного и прямого плеч соответственно , стробируюищй транзистор 12 обогащенного типа, транзистор обратной связи ,13 обедненного типа. За счет подключения затвора нагрузочного транзистора 4 инвертора прямого плеча к входу 11 инвертора инверсного плеча уменьшается суммарное количество задержек распространения сигнала от входной шины 7 триггера до выходной 1иины 10, а также снижается сопротивление нагрузочного транзистора 4 при подаче на его затвор напряжения высокого уровня. Для увеличе- .ния суммарного сопротивления цепи обратйой связи введен дополнительный транзистор обратной связи 14, что приводит к стабилизации режима записи . 1 ил. с (Л

CCNO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 03 К 3/286

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4293253/?4-21 (22) 03.08.87 (46) 15.03.89. Бюл. h» 10 (72) С.Г.Ильченко и А.Ф.Дряпак (53) 621.374(088.8) (56) Патент С1!1А 1» 3775693, кл. 330-35, 29. 11. 71.

Заявка Японии h» 59-26134, кл Н 03 К 3/356, 26.02.76. (54) ТРИГГЕР HA ИДП-ТРАНЗИСТОРАХ (57) Изобретение относится к области вычислительной техники и может быть использовано при разработке цифровых интегральных микросхем на ИДП-транзисторах. Цель изобретения — повышение быстродействия триггера при сохранении потребляемой мощности. Триггер содержит инверторы 1 и 2 инверсного и прямого плеч соответственно, состоящие из нагрузочных транзисторов 3, 4 обедненного типа и логичес„„SU„„1465940 ких транзисторов 5, 6 обогащенного типа, входи ю шину 7, шину сигналов синхронизации 8, выходные шины 9, 10 инверсного и прямого плеч соответ— ственио, стробирующий транзистор 12 обогащенного типа, транзистор обратной связи, 13 обедненного типа. 3а счет подключения затвора нагрузочного транзистора 4 инвертора прямого плеча к входу 11 инвертора инверсного плеча уменьшается суммарное количество задержек распространения сигнала от входной шины 7 триггера до выходной шины 10, а также снижается сопротивление нагрузочного транзистора 4 при подаче на его затвор напряжения высокого уровня, Для увеличе,ния суммарного сопротивления цепи обратной связи введен дополнительный транзистор обратной связи 14, что приводит к стабилизации режима записи. 1 ил.

1463940

Изобретение относится к вычисли тельной технике и может быть HclloJTH завала при разработке гд.фровьгх интегральньгх микросхем на !!> П-транзиста 3 рах, Цель изобретения — поль>шение быстродействия триггера при сохранении потребляемой мощности.

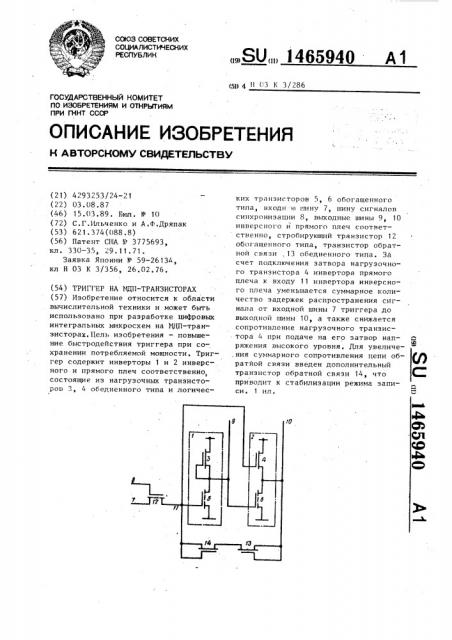

На чертеже представлена электри- i0 ческая принципиальная схема триггера на МЦП вЂ транзистор.

Триггер содержит последовательно соединенные инверторы и верслого 1 и прямого 2 плеч., сос го.->щие из нагру- 15

| зочнаго транзистора обедненного ти1 па 3 инверснагo плеча и 4 прямого

1 плеча, логического транзистора обо гащенного типа 5 инверсного плеча и, 6 прямого плеча, входную шину 7, шину20 (8 сигналов синхронизации, выходные шины 9 инверсного и 10 прямого >плеч., вход 11 инвертора инверсного плеча, стробирующий транзисгор 12 абггнщеи! наго типа, транзистор 13 обратной связи и дополнительный ..ранзистар 14 обратной связи, оба — обедненного ти па. Затвор нагрузочного транзистора 3 инвертора 1 соединен с выходок ин— вертора 1 выла 1някицик функции вь>ход-30 ной шины 9 инверсного плеча. >!ежду входной шиной 7и входом 11инвер npa инверсного пле«а вк>почен стробирующий транзистор 12, затвор которого >-.одl ключен к нине 8 сигналов синхрониза-! с ции. Затвор нагруэочнаго транзистора 4 инвертора 2 прякогс»>леча подключен к входу !1 инвертсра 1 инверсного плеча, Между выхог:,ок инвсртора прямо-го плеча, выполняк>щим функции выход> най шины 10 прямаг а плече р и входом

11 инвертора 1 последовательно вклю— челы транзистор.13 обратной связи и дополнительный транзистор 14 обратной связи, при этом затвор транзистора 13 4 подключен к выходной шине 10, а затвор транзистора 14 — к входу 11 инвертора 1.

Триггер на МДП-транзисторах работает следующим образом.

5С

Предположим, что в начальный момент времени триггер находится в режиме хранения информации, т,е, на шине 8 сигналов синхронизации действует напряжение низкого уровня и стробирукнций транзистор..12 закрыт, а на выходных шинах 9 и 10 триггера действует напряжение вь>сакого и Hp.экого уровней соответственно. Чере > высокое сопротивление открытых транзисторов 13 и 14 обратной связи напряжение с выходной шины 10 прямого плеча триггера передается на вход 11 инвертора 1 инверсного плеча и на затвор нагрузочнога транзистора 4 ин— вертора 2 прямого плеча, что позволяет асушествлять режим хранения в течение нег>граниченного времени или до выключения питания без регенера-.,г ции, нагрузочный транзистор 4 при этом находится в режиме, соответствующем токастабилиэирующему резистору.

Для г.сревода триггера из режима хранения в режим записи информации íà нн>ну 8 сигналов синхронизации следует подать напряжение высокого уровня, а ла входную шл у 7 триггера — нужную информацию> наг;рикер напряжение высоко> о уровня. При этом инвертор 1 нач»ет переключаться в состояние, соотJercvIIyII>Il;ee напряжению низкого уровня на выходной шине 9, логический гралзистар б инвертора 2 начнет закрываться, Одновременно с переключением инвертора 1 начинается заряд вы,ходной шины 10 прямого плеча через полностью GTKpbITblH нагрузочный транзистор 4 инвертора 2 за счет подачи на его затвор входного наыпряжения высокого уровня, Обратная связь в режиме записи информации в триггер практически не оказывает влияния ва счет значительно более высокого сопротивления транзистора 13 обратной связи по сравнению с сопротивлением открытого стробирующего транзистора

12, Аналогично производится запись информации, соответствуюшей напряжению низкого уровня, при которой нагрузочный транзистор 4 инвертора 2 закрывается, так как напряжение на

его истоке превышает напряжение на затворе, и, следовательно, на начальной стадии переключения инвертора 2 прямого плеча весь ток, протекающий через открывающийся логический транзистор б, будет соответствовать току разряда выходной шины 10 прямого плеча, а не суммарному току нагруэочнаго транзистора 4 и тока разряда выходной шины 10 прямого плеча, Поскольку при записи информации, соответствующей напряжению низкого уровня, сопротивление транзистора 13 обратной связи оказывается низким из-за того, что íà его истоке будет действовать напряжение низкого уров1465940

Формула из обретения

Составитель А.Цехановский

Техред Л.Сердюкова Корректор М.Самборская

Редактор А.Маковская

Заказ 953/52 Тираж 879 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35 ° Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 ня, а затвор окажется соединенным со стоком и на них некоторое время будет действовать напряжение высокого уровня с выходной шины 10, то для увеличения суммарного сопротивления цепи обратной связи введен дополнительный транзистор 14. обратной связи, у которого в этом режиме затвор оказывается соединенным с истоком, чем достига- 10 ется стабилизация режима записи.

Триггер на МДП-транзисторах,-содер-15 жащий последовательно соединенные ! инверторы инверсного и прямого плеча, состоящие иэ нагруэочного транзистора обедненного. типа и логического транзистора обогащенного типа, затвор 20 нагруэочного транзистора инвертора инверсного плеча соединен с его выходом, подключенным к выходной шине ин» версного плеча, входную шину, шину сигналов синхронизации, выход инвер-. 25 тора прямого плеча подключен к выходной шине прямого плеча, стробирующий транзистор обогащенного типа, исток,, которого подключен к входной. шине триггера, сток — к входу инвертора инверсного плеча, затвор стробирующего транзистора подключен к шине сигналов синхронизации, транзистор обратной связи обедненного типа, подключенный затвором и одним иэ электродов к выходу инвертора прямого плеча, отличающийся тем, что, с целью повышения быстродействия триггера при сохранении потребляемой им мощности, затвор,нагрузочного транзистора инвертора прямого плеча подключен к входу инвертора инверсного плеча, а между входом инвертора инверсного плеча и другим электродом транзистора обратной связи включен дополнительный транзистор обратной связи обедненного типа, затвор которого подключен к входу инвертора инверсного плеча.