Арифметико-логическое устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой обработке сигналов и позволяет повысить быстродействие арифметико-логического устройства. Устройство содержит блок 1,2 логических операций, элемент 3 РАЗНОЗНАЧНОСТЬ, мультиплексоры 4,6, элемент 5 НЕРАВНОЗНАЧНОСТЬ, коммутаторы 7,8 и элементы НЕ 9-12 с соответствующими связями. Межразрядный перенос формируется мультиплексорами, результаты операций - коммутаторами с тремя устойчивыми состояниями. Использование тактирующих сигналов позволяет организовать режим обработки данных, что повышает быстродействие устройства. 1 з.п. ф-лы, 4 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1481742

159 4 G 06 F 7 38

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4322793/24-24 (22) 29.10.87 (46) 23.05.89. Бюл. № 19 (72) С. А. Соколов и Ю. Г. Дьяченко (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 983705, кл. G 06 F 7/38, 1981.

Авторское свидетельство СССР № !309017, кл. G 06 F 7/38, 1985. (54) АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО (57) Изобретение относится к цифровой обработке сигналов и позволяет повысить быстродействие арифметико-логического устройства. Устройство содержит блоки 1, 2 логических операций, элемент 3 РАВНОЗНАЧНОСТЬ, мультиплексоры 4, 6, элемент 5

НЕРАВНОЗНАЧНОСТЬ, коммутаторы 7, 8 и элементы НЕ 9 — !2 с соответствующими связями. Межразрядный перенос формируется мультиплексорами, результаты операций — коммутаторами с тремя устойчивыми состояниями. Использование тактирующих сигналов позволяет организовать конвейерный режим обработки данных, что повышает быстродействие устройства. 1 з.п. ф-лы, 4 ил., 1 табл.

148!742

Формула изобретения

Изобретение относится к области вычислительной техники и цифровой обработки сигналов и, в частности, может использоваться при проектировании цифровых микросхем и микропроцессорных наборов.

Целью изобретения является повышение быстродействия.

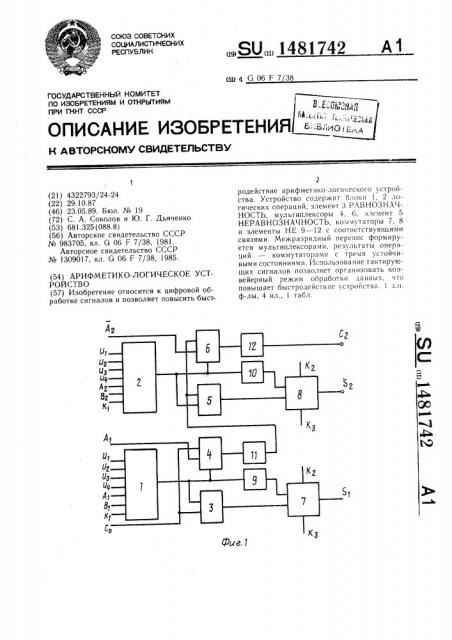

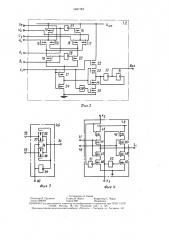

На фиг. 1 представлена схема арифметико-логического устройства; на фиг. 2 схема блока логических операций; на фиг. 3-схема мультиплексора; на фиг. 4 — схема коммутатора.

Устройство (фиг. 1) содержит первый и второй блоки 1 и 2 логических операций, элемент 3 РАВНОЗНАЧНОСТЬ, первый мультиплексор 4, элемент 5 НЕРАВНОЗНАЧНОСТЬ, второй мультиплексор 6, первый и второй коммутаторы 7 и 8, с первого по четвертый элементы НЕ 9 — 12.

Блок 1(2) логических операций (фиг. 2) содержит с первого по одиннадцатый

МОП-транзисторы 13 — 23 р-типа, с первого

«о третий МОП-транзисторы 24 — 26 п-типа, с первого по пятый элементы НЕ 27 — 31.

Мультиплексор 4 (6) (фиг. 3) содержит первый и второй информационные входы

32 и 33, выход 34, два МОП-транзистора

35 и 36 с каналом р-типа, два МОП-транзистора 37 и 38 и-типа и элемент HE 39, истоки транзисторов 35 и 37 подключены к первому информационному входу 32 мультиплексора, а их стоки — к выходу

34 мультиплексора и стокам транзисторов

36 и 38, истоки которых соединены с вторым информационным входом 33, затворы транзисторов 37 и 38 подключены к управляющему входу 40 мультиплексора и входу элемента НЕ 39, выход которого соединен с затворами транзисторов 35 и 38.

Коммутатор 7 (8) (фиг. 4) содержит первый и второй информационные входы 41 и 42 коммутатора, четыре МОП-транзистора 43—

46 р-типа, четыре МОП-транзистора 47—

50 п-типа, первый и второй элементы НЕ

51 и 52, истоки транзисторов 43 и 45 подключены к шине питания (И), а их стоки к истокам транзисторов 44 и 46 соответственно, истоки транзисторов 48 и 50 подключены к шине земли, а их стоки — к истокам транзисторов 47 и 49 соответственно, стоки транзисторов 44, 46, 47 и 49 объединены и подключены к выходу коммутатора, затвор транзистора 43 соединен с первым управляющим входом коммутатора и входом элемента HE 51, выход которого соединен с затвором транзистора 48, затворы транзисторов 44 и 47 подключены к информационному входу 41 коммутатора, затворы транзисторов 48 и 49 подключены к информационному входу 42, затвор транзистора 45 соединен с вторым управляющим входом коммутатора и с входом элемента НЕ 52, выход которого соединен с затвором транзистора 50. 10 !

Устройство (фиг. 1) работает следующим образом.

В зависимости от значений Ui — U4 на входах задания вида операции устройства и значений Кг, Ка на входах задания арифметической или логической операции формируются значения Si, S2 результата и переноса С действия над операндами Ai, Аг и Bi, В, записанными в блоки 1 и 2 по тактовому сигналу К и входным переносом Со со гл а с но табл ице.

При значениях сигналов Кг=К =1 выход устройства переходит в третье состояние, что может быть использовано для работы на общую шину.

Использование сигнала К позволяет организовать конвейерный режим работы.

1. Арифметико-логическое устройство, содержащее два блока логических операций, два мультиплексора, элемент НЕРАВНОЗНАЧНОСТЬ, два коммутатора и четыре элемента НЕ, причем с первого по четвертый входы задания вида операции устройства соединены с соответствующими управляющими входами первого и второго блоков логических операций, первый и второй информационные входы первого блока логических операций соединены соответственно с входами первых разрядов первого и второго операндов устройства, входы вторых разрядов первого и второго операндов устройства соединены соответственно с первым и вторым информационными входами второго блока логических операций, выходы первого и второго коммутаторов являются соответственно выходами первого и второго разрядов результатов устройства, вход задания арифметической операции которого соединен с первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы которых объединены и соединены с входом задания логической операции устройства, выход первого блока логических операций соединен через первый элемент HE с первым информационным входом первого коммутатора, выход второго блока логических операций через второй элемент НЕ соединен с первым информационным входом второго коммутатора, вход переноса устройства соединен с первым информационным входом первого мультиплексора, отличающееся тем, что, с целью повышения быстродействия, оно содержит элемент РАВНОЗНАЧНОСТЬ, причем выход первого блока логических операций соединен с управляющим входом первого мультиплексора и с первым входом элемента

РАВНОЗНАЧНОСТЬ, второй вход и выход которого соединены соответственно с входом переноса устройства и с вторым информационным входом первого коммутатора, вход

1481742

Арифметическая операция К = 1, К =0

U Логическая

Uü

4 2 операция

Кз

Kã

А,V В,.

1

1

1

1

1

1

1

0

0

0

0

1

1

0

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

A;v В„

А„.

А,v В„

В, А;Ю В;

А; В

А-У Вь

А,O+ В;

В„

А,. В„

A„

А.„В„.

А В;

0 первого разряда первого операнда устройства соединен с вторым информационным входом первого мультиплексора, выход которого через третий элемент НЕ соединен с первым информационным входом второго мультиплексора и с первым входом элемента НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с вторым информационным входом второго коммутатора, выход второго блока логических операций соединен с вторым входом элемента НЕРАВНОЗНАЧНОСТЬ и с управляющим входом второго мультиплексора, второй информационный вход которого является входом инверсного второго разряда первого операнда устройства, выход второго мультиплексора соединен через четвертый элемент НЕ с выходом переноса устройства, тактовый вход которого соединен с тактовыми входами первого и второго блоков логических операций.

2. Устройство по п. 1, отличающееся тем, что блок логических операций содержит одиннадцать МОП транзисторов р-типа, три МОП транзистора и-типа и пять элементов НЕ, причем истоки первого, второго и десятого МОП-транзисторов р-типа соединены с шиной питания устройства, затвор первого МОП-транзистора р-типа соединен с первым информационным входом блока логических операций и с входом первого элемента НЕ, выход которого соединен с затвором второго МОП-транзистора р-типа, сток первого МОП-транзистора р-типа соединен с истоками третьего и четвертого

МОП-транзисторов р-типа, сток второго

МОП-транзистора р-типа соединен с истоками пятого и шестого МОП-транзисторов р-типа, затворы с третьего по шестой

МОП-транзисторов р-типа являются соответственно четвертым, первым, третьим и вторым управляющими входами блока логических операций, стоки третьего и пятого МОПтранзисторов р-типа соединены с истоком седьмого МОП-транзистора р-типа, стоки четвертого и шестого МОП-транзисторов р-типа соединены с истоком восьмого MOIL-транзистора р-типа, стоки седьмого и восьмого МОП-транзисторов р-типа соединены с истоком девятого MOll-транзистора р-типа, затвор. седьмого МОП-транзистора р-типа соединен с вторым информационным входом блока логических операций и через второй элемент НŠ— с затвором восьмого МОПтранзистора р-типа, сток девятого и затвор одиннадцатого МОП-транзисторов ртипа соединены со стоком первого и затвором второго МОП-транзисторов п-типа, затворы девятого и десятого МОП-транзистора р-типа и первого МОП-транзистора и-типа объединены, соединены с тактовым входом блока логических операций и через третий элемент HE — с затвором третьего МОП-транзистора п-типа, сток десятого

25 МОП-транзистора р-типа соединен с истоком одиннадцатого МОП-транзистора р-типа, сток которого соединен со стоком второго

МОП-транзистора п-типа, с входом четвертого элемента НЕ и с выходом пятого элемента НЕ, вход которого соединен с выхо30 дом четвертого элемента НЕ и является выходом блока логических операций, исток второго МОП-транзистора и-типа соединен со стоком третьего МОП-транзистора п-типа, исток которого соединен с истоком первого МОП-транзистора и-типа и с шиной зем35 ли устройства.

С„â€” 1 — 1 (A V В„ ) + C i. — 1 (А„у В„) + С вЂ” 1

А„+ С.„- 1 (А„В„) + С; — 1 — 1 (А„ v В;)+(А„ В„) + С; — 1

А; +В, + С,— 1

А„+ (А„В ) + С; — 1 (А„.v В;)+А„+С,-1

А„-„— 1+С„-1 (A„U В; )+(A„B, )+ф— 1

А„+(А. В )+С; — 1

А,-1+С; — 1 (A; v B;)+A„+C„ — 1 (А; / В„)+А„+С вЂ” 1

А„-+А; +С,. — 1

1481742

Составитель А. Клюев

Редактор Л. Гратилло Техред И. Верес Корректор С. Черни

Заказ 2690/49 Тираж 669 Подписное

ВНИИПИ Государственного комитета-по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж вЂ” 35, Раушская на 6., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101