Устройство для вычисления квадратного корня

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может применяться в системах автоматического управления, измерения и контроля. Целью изобретения является обеспечение контроля устройства для вычисления квадратного корня. Поставленная цель достигается тем, что в состав устройства, содержащего коммутатор 2, накапливающий сумматор 3 и блок управления 4, введены сдвигающий регистр 5, триггер 6, элементы И 7,8 и ИЛИ 9. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК,.Я0„„1481753 (5в 4 G 06 F 7 552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

IlPM ГКНТ СССР

Н А BTOPCKOMY СВИДЕТЕЛЬСТВУ (21) 4349128/24-24 (22) 26.10.8?

{46) 23.05.89. Бюл. № 19 (71) Киевский политехнический институт им. 50-летия Великой Октябрьской социалистической революции (72) В. И. Жабин, В. Н. Дорожкин и Г. В. Гончаренко (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 413475, кл. G 06 F 7/38, 1972.

Авторское свидетельство СССР № 877529, кл. G 06 F 7/552, 1981.

2 (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ (57) Изобретение относится к вычислительной технике и может применяться в системах автоматического управления, измерения и контроля. Целью изобретения является обеспечение контроля устройства для вычисления квадратного корня. Поставленная цель достигается тем, что в состав устройства, содержащего коммутатор 2, накапливающий сумматор 3 и блок управления 4, введены сдвигающий регистр 5, триггер 6, элементы И 7, 8 и ИЛИ 9. 2 ил., табл.

1481753

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных машинах и устройствах.

Цель изобретения — обеспечение функционального контроля устройства.

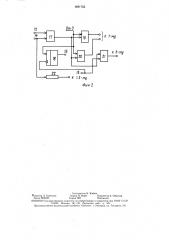

На фиг. 1 представлена структурная схема устройства для вычисления квадратного корня; на фиг. 2 — блок управления.

Устройство содержит реверсивный счетчик 1, коммутатор 2, накапливающий сумматор 3, блок 4 управления, регистр 5 сдвига, 0-триггер 6, элементы И 7 и 8, элемент

ИЛИ 9, первый 10 второй 11 информационные входы, синхровходы 12 — 14, выход 15 15 результата, выход 16 ошибки, элемент

ИЛИ 17,-0-триггер 18, элементы И 19 и 20, элемент ИЛИ 21, элемент 22 задержки.

Устройство может быть реализовано на м и кросх ем ах серн и К 155.

Устройство для вычисления квадратного корня функционирует в избыточной двоичной системе счисления с цифрами 1,0,— 1.

Для получения очередной i-й цифры результата Z= — - Х, при Х вЂ” —, используются

4 9

2 16 формулы

2 Г,,+ — Х ., R,=NL -2Z„1 Z, — Z2 2

-i.- >

1, если N,>i Z„, +2

Z,= О, если Z„. +2, N;),— Z;.,+2 " — 1,если И,! -Z;, +2 где Х; — очередная цифра операнда; 35

К; — остаток, формируемый в i-м шаге;

„V; — промежуточная переменная; очередная цифра результата; Z; — результат, содержащий i старших разрядов. При этом i=1,...,ï+1, а начальными являются значения R„=O, Z„=O.

Использование приведенного алгоритма в избыточной знакоразрядной системе счисления налагает ограничения на форму результата. Чередование цифр результата выполняется по строгим правилам. За по- 45 ложительной цифрой 1 может следовать цифра — 1 и наоборот. При этом между ними находится любое число нулей. Однако между одинаковыми зиачащами (отличными от нуля) цифрами не может быть меннее одного нуля. Например, резуль- 5G тат может иметь вид 10101101 и не может быть получен в форме 11011111, если устройство функционирует правильно.

Устройство работает следующим образом.

В исходном состоянии в сумматоре 3 и счетчике 1 записаны нули, в сдвигающем регистре 5 записаны все нули, кроме младшего разряда, где записана единица.

В первом такте каждого i-го цикла вычисления (i= 1,2,..., и+1) цифра операнда, имеющая вес 2 и принимающая значение из множества (— 1,0,1), прибавляется в i-й разряд сумматора 3 путем выдачи прямого (при Х;=1) или обратного кода (при К;= — 1) со сдвигающего регистра 5.

На вход переноса в младший разряд сумматора 3 подключен вход 10 устройства.

Затем в младший разряд счетчика 1 прибавляется единица, если в знаковом разряде сумматора 3 записан нуль, или вычитается единица, если в знаковом разряде сумматора 3 записана единица. Знаковым разрядом сумматора 3 в i-м такте считается старший разряд. Во втором такте по сигналу блока 4 управления из сумматора 3 вычитается содержимое счетчика 1, если в знаковом разряде сумматора 3 записан нуль, или к сумматору 3 прибавляется содержимое счетчика 1, если в знаковом разряде сумматора 3 записана единица.

При этом блок 4 управления формирует и выдает на выход 15 цифру результата, имеющую вес 2 + . Эта цифра равна нулю, если содержимое знакового разряда сумматора 3 не совпадает с его предыдущим значением, единице, если в знаковом разряде сумматора 3 до и после сложения был записан нуль, — 1, если в знаковом разряде сумматора 3 до и после сложения была записана единица. Одновременно происходит проверка правильности следования цифр результата. Цепочка элементов 0-триггер 6, элемент И 7 обнаруживает появление комбинаций цифр результата 11, а цепочка,D-триггер 6, элемент

И 8 — появление комбинации 11; в случае появления одной из этих комбинаций на выходе ИЛИ 9 появится сигнал ошибки.

В третьем такте по тем же правилам осуществляется сложение или вычитание кодов сумматора 3 и счетчика 1. Затем в младший разряд счетчика 1 прибавляется или вычитается единица. Цикл заканчивается сигналом на входе 14, по которому выполняется сдвиг на два разряда влево содержимого сумматора 3, сдвиг на один разряд влево содержимого сдвигающего регистра 5, счетчика 1, Для получения п-разрядного результата необходимо выполнить и+! циклов вычислений.

В таблице, где через Х; и Z, обозначены цифры аргу. мента Х и результата Z, имеющего вес 2 приведен пример вычисления квадратного корня из числа Х=0,110111

=0,110001. При этом получен результат

Z=1,01! 000=0,110000.

В устройстве для вычисления квадратного корня происходит обнаружение константных неисправностей («!» или

«О») в любом блоке, участвующем в формировании цифр результата. Отка1481753

Формула изобретения

Цикл Такт Регистр Х Счетчик 1 Сумматор 3 2

1 000000.01

000000.10

1 00000.011

00000.100

0 0000.0111

0000.0110

1 000.01101

000.01110

-1 00.011101

0000001

0000100

0001000

0010000

00.011100

-1 0.0111001

0100000

0.0111000 .01110001 .01110000

1000000 зы в схеме контроля и схеме управления также будут зафиксированы, так как нарушится разрешенный порядок следования цифр результата, Предположим, что в i-м разряде сумма- 5 тора произошел константный отказ по «1».

Если i>2, тогда в /г-м такте и ри Л де ) — 1 — 2, — f (V(<, 1+2 (Z =1. Значит N +ie)1; 2(, Z +i — — 1, N + e)$; 2;(, Zk+2=1

Появление Zy = 1; Z> =1 вызовет сигнал ошибки.

Аналогично доказывается возможность обнаружения константного отказа по «О» в любом из -х разрядов, где i)2. Возник- 15 новение константного отказа по «О» или «1» в любом блоке приводит к упомянутым ситуациям.

Устройство для вычисления квадратного корня, содержащее накапливающий сумматор, реверсивный счетчик, блок управления и коммутатор, информационный вход и выход которого соединены с выходом 25 реверсивного счетчика и входами накапливающего сумматора соответственно, отличаюи1ееся тем, что, с целью обеспечения функционального контроля, в него введены регистр сдвига, D-триггер, элементы И, ИЛИ, причем информационные входы накапливаю- 30 щего сумматора соединены с выходами регистра сдвига, первый и второй управляю1

3

2

1

3

2

1

3

2

1

3 щие входы которого подключены соответственно к первому и второму информационным входам устройства, выход старшего разряда накапливающего сумматора соединен с входом анализа знака блока управления, с первыми входами первого и второго элементов И и управляющим входом коммутатора, вход записи блока управления соединен с первым синхровходом устройства, второй синхровход которого подключен к одноименному входу D-триггера и первому входу формирования сдвига блока управления, второй вход формирования сдвига которого соединен с третьим синхровходом устройства и одноименным входом регистра сдвига, первый выход блока управления соединен с управляющим входом реверсивного счетчика, второй выход — с входами управления сдвигом реверсивного счетчика и накапливающего сумматора, третий выход — с D-входом D-триггера, с вторыми входами первого н второго элементов И и является выходом результата устройства, выход ошибки которого является выходом элемента ИЛИ, первый и второй входы которого подключены к выходам соответственно первого и второго элементов И, третьи входы которых соединены соответственно с прямым и инверсным выходами D-триггера, четвертый выход блока управления соединен с входом выполнения операции накапливающего сумматора, вход переноса в младший разряд которого соединен с первым информационным входом устройства.

00000000.01

00000000.00

11111111.11

1111111.110

0000000.001

1111111.110

111111.1000

111111.1111

000000.0110

00001.00000

00000.10011

00000.00110

0000.001000

1111.101011

0000.001000

000.0000000

111.1000111

000.0000000

00.00000000

11.10001111

00.00000000

1481753

Dm5

-му

Составитель В. Жабин

Редактор Л. Гратилло Техред И. Верее Корректор А. Обручар

Заказ 2690/49 Тираж 669 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, 7K — 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101