Матричное устройство для вычисления свертки

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах для вычисления свертки потока векторов X(L, M) ={X<SP POS="POST">1</SP>(M), X<SP POS="POST">2</SP>(M), ...X<SP POS="POST">L</SP>(M)} с вектором Ω(N). Цель изобретения - повышение быстродействия. Цель достигается тем, что устройство содержит N [M-(N-1)/2] операционных блоков, где N - "длина импульсной характеристики", причем операционный блок содержит три регистра, умножитель и сумматор. В основу работы устройства положен алгоритм вычисления свертки, который задан рекуррентными соотношениями. Особенностью функционирования устройства является параллельно-поточная организация вычислений. Время вычисления свертки составляет T(M)=M+N-1 тактов. 3 ил.

союз советских

СОЦИАЛИСТИЧЕСН ИХ

РЕСПУБЛИН (бц 4 С 06 Г 5/3l7

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ СВИ4ЕТЕЛЬСТВУ (k-0

Y, 1

У;

Y °

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4358!67/24-24 (22) 30.11.87 (46) 15.07.89. Бюл. У- 26 (72) В.П. Якуш, С.Г. Седухин, П.И. Соболевский и Н.A. Лиходед (53) 683.32(088.8) (56) Kung Н.Т. Nhy systo1ic architectures": — Сошрп er, 1 982, М- I, с.42, рис .8.

Лвторское свидетельство СССР

М 1401477, кл. Г 06 F 15/347, 1986. (54) МЛТРИЧНСЕ УСТРОЙСТВО ДЛЯ В! .ЧИСЛЕНИЯ СВЕРТКИ (57) Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах для вычисления сверт

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах цифровой обработки сигналов.

Цель изобретения — повышение быстродействия устройства.

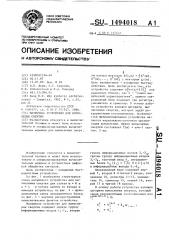

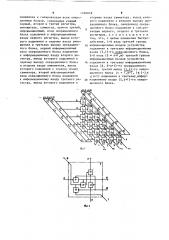

На фиг. 1 изображена структурная схема матричного устройства для вычисления свертки для случая m = 6 и и = 4 и потоки данных на входах и выходах устройства на фиг. 2 — функциональная схема операционного блока, на фиг. 3 — картина распространения вычислительных фронтов устройства.

Матричное устройство для вычисления свертки содержит первую группу информационных входов 1 -1„, вторую

„.Я0„„1494018 А 1

1 ки потока векторов Х(1,m) = (Х (m), X (m) X (m)) с вектором Q (и) .

Цель изобретения — повышение быстро; действия. Цель достигается тем, что устройство содержит num-(n-1)/2) onetl рационных блоков, где n — длина импульсной характеристики, причем операционный блок содержит три регистра, умножитель и сумматор. В основу работы устройства положен алгоритм вычисления свертки, который задан рекуррентными соотношениями. Особенностью функционирования устройства является параллельно-поточная организация вычислений. Время вычисления свертки составляет T(m) = m+n-1 тактов . 3 ил. группу информационных входов 2,-2, третью группу информационных входов

31-36, тактовый вход 4, операционные блоки 5; (i, j = 1,6, 0 - i-j 63) и информационные выходы 6, -6

Операционный блок содержит первый 7, второй 8 и третий 9 входы, синхровход 10, регистры 11 — 13, умножитель 14, сумматор 15, первый 16, второй 17 и третий 18 выходы.

В основу работы устройства положен алгоритм вычисления свертки, который задан рекуррентными соотношениями для ,((о, -у р.

1494018 где 1 i < m, max(1, i-и+1) » k и i, ш)n. операционный блок работает следующим образом.

На i-м такте на вход 9 подается значение Х, на вход 7 — значение Q на вход 8 — значение Y. В регистры

11-13 записываются соответственно значения Х,(, ) и Y. На выходе умножителя 14 формируется значение Х И, а на выходе сумматора 15 — значение

Z Y+Х Ы °

При описании работы устройства в обозначении Y в скобах указывается номер i-ro рекуррентного шага, а в обозначении У вЂ” номер i указывает такт работы устройства.

Устройство работает следующим образом.

В исходном состоянии регистры

11-13 операционного блока устанавливаются в нулевое состояние. На входы

3„,3, 3, 3, 3, 36 подаются соответственно элементы Х, Х, Х4, Хз, Х и Х,. Iia входы I .. 1, 13 и I

z. подаются постоянно соответственно элементы вектора ()4,О, И и И, °

На входы 2j (j = 1,6) подаются постоянно нулевые значения соответствующих элементов у, = 0 (фиг .1)

Рассмотрим работу устройства при вычислении свертки для вектора Х (1,6) .

На нулевом такте на входы 3 и I < подаются соответственно Х, и O . При этом в операционном блоке 5ь формируе-. < я значение Y = Y + О Х, i I (el

На nåðâoì такте йа входы 3 и 1 ! подаются соответственно элементы Х и ц . I.ðè этом в операционном блоке

5gz формируется значение У = Y< +

+ Q4X<, а в операционном блоке 56 значени» У. = У +И Х,, На втором такте на входы 34 и lз

z подаются соответственно элементы X и Я . При этом в операционном блоке ъ

5< формируется значение Y6 "- уб +

Р1» 1О

+ Ц4 Х>, а в операционном блоке 5@>значение Y 4 У +Я Х, а в операционном блоке 5 — значение Y z (à) (ol 63 Уг+>zX °

ВТ—

Йа третьем такте на вход 14 по1 дается элемент Я,. При этом в операционном блоке 5 формируется зна(й) И) чение Y з Y z + Я Х э в операционном !

55 «сп-1) подключен к втоРому информа5

45 блоке 5 — значение у = у + Я Х

5ф Ъ Ъ 2. Хъ в операционном блоке 5<< - значение

На четвертом такте на вход 3 поФ

3 дается элемент Х .При этом на операционном блоке 5у формируется значе(41 (Ы ние Y < = Y 6 + Q> Х4, в операционном блоке 5<> — эначение Y < = Y +ЯдХз, И) Р) в операционном блоке 5 — значение у у(и у(1)+ и Х

2. 1 0 Ф

Аналогичным образом формируются значения остальных элементов выходного вектора У(1,6) . На выходах 6„, 6, 6>, 6, 6 < и 6 формируются соответственно элементы Y, Y-,,Y+, 5 4 3

У, Y и У, выходного вектора Y(1,6) .

На выходах устройства,> <,6

6„„формируются соответственно элементы т элемент . ектора Y(l,m), t, =- (i+n-2)+

+(1-1) — номер так" а.

В предлагаем,>м устройстве вычисление свертки для входного вектора

X(m) осуществляется. за время T(m)

= m+n-1 тактов с периодом обработки очередного вектора Х(т) в потоке, равным единице.

Форм улан зобретени я

Матричное устройство для вычисления свертки, содержащее матрицу

n(m-(и-1) /2 ои".Рационных блоков (и — длина импульсной характеристики, m — размерность входного вектора

X(m), i-й вход (i = l,n) первой группы информационных входов устройства подключен к первому информационному входу (m,i+m-n) — ro операционного блока, j-й вход (j =,m n) второй группы информационных входов устройства подключен к втором, информационному входу (n+j-l,j) -го операционного блока, k-A вход (k =

= m-n+l,m) второй группы информационных входов устройства подключен к второму информационному входу (тп, k)-ro операционного блока, первый выход (1,р)-ro операционного блока (1 = 2,m1 р = 2,m; 0 1 - р п-1) подключен к первому информационному входу (1-1; р-1)-ro операционного блока, второй выход (1,r)-го операционного блока (r = l,m; 1 -1-r ционному входу (1-1,r)-ro операционно-

ro блока, второй выход (r r) -го операционного блока является г-м выходом устройства, тактовый вход устройства

14940l 8 подключен к сннхровходам всех операционных блоков, соде ржащих к аждый первый, второй и третий регистры, умножитель, сумматор, причем третий, 5 информационный, вход операционного блока подключен к информационному входу первого регистра, выход которого подключен к первому входу умножителя и третьему выходу операционного блока, первый информационный вход операционного блока подключен к информационному входу второго регистра, выход которого подключен к первому выходу операционного блока 15 и второму входу умножителя, выход которого подключен к первому входу сумматора, второй информационный вход операционного блока подключен к информационному входу третьего ре- рд гистра, выход которого подключен к второму входу сумматора, выход которого подключен к второму выходу операционного блока, синхровход операционного блока подключен к син: ровходам первого, второго и третьего регистров, о т л и ч а ю щ е е с я тем, что, с целью повьидения быстродействия, i-й вход третьей группы информационных входов устройства подключен к третьему информационному входу (i,1) -го операционного блока, S-й вход (S и+),m) третьей группы информационных входов устройства подключен к третьему информационному входу (S, S-п+)) -ro операционного блока, третий выход (1 t) -го операдиоииого блока (t = l,m-l, а 1-j Е а

< n-I) подключен к третьему,информационному входу (1,t+t)-го операционного блока.

1494018

Редактор А. Ревин

Заказ 4112/46 Тираж 668 Подписное в

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, И(-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

7 б

Составитель К. Кухаренко

Техред А. Кравчук Корректор И. Горная