Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть применено в микросхемах памяти. Целью изобретения является повышение устойчивости оперативного запоминающего устройства (ОЗУ) к кратковременному воздействию дестабилизирующих факторов. Поставленная цель достигается тем, что в устройство введен генератор 14 фототока, а в каждый элемент памяти - третий и четвертый нагрузочные резисторы 7,8. При воздействии на ОЗУ дестабилизирующих факторов включается генератор 14 фототока и поддерживает на резисторах 7,8 перепад напряжений, необходимый для сохранения информации. 1 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU,, 1501 2 А1 (gg 4 С 11 С 11/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМ У СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4379894/24-24 (22) 28. 12. 87 (46) 15. 08. 89. Бюл. Р 30 (71) Московский инженерно-физический институт (72) А.С. Березин, А.Г. Гарицын, С.А. Королев, И.И. Кузовлев, И.В. Черняк и А.В. Нальнов (53) 681.327.66(088.8) (56) Валиев К.А., Орликовский А.А.

Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах. H.: Советское радио, 1979, с. 115, рис. 4.23 .

Там же, с. 418, рис. 4.26. (54) ОПЕРАТИВНОЕ ЗАПОИИНАЮЩЕЕ УСТРОЙСТВО

2 (57) Изобретение относится к вычислительной технике и может быть применено в микросхемах памяти. Целью изобретения является повьппение устойчивости оперативного запоминающего устройства (ОЗУ) к кратковременному воздействию дестабилизирующих факторов. Поставленная цель достигается тем, что в устройство введен генератор 14 фототока, а в каждый элемент памяти — третий и четвертый нагрузочные резисторы 7, 8. При воздействии на ОЗУ дестабилизирующих факторов включается генератор 14 фототока и поддерживает на резисторах 7, 8 перепад напряжений, необходимый для сохранения информации. 1 ил.

3

150116

Изобретение относится, к вычислительной технике и может быть использовано при проектировании микросхем памяти.

Цель изобретения — повышение устойчивости оперативного запоминающего устройства (ОЗУ) к кратковременному воздействию дестабилизирующих факторов (ДФ),не приводящему к необрати- 10 мому изменению параметров транзисторов.элементов памяти ОЗУ.

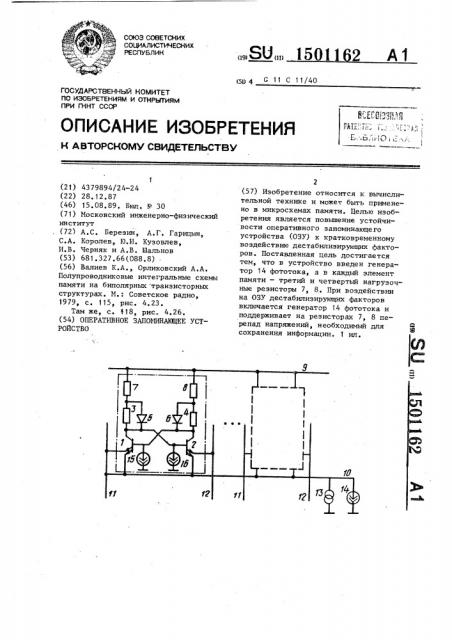

На чертеже представлена электрическая схема ОЗУ.

Предлагаемое ОЗУ содержит элемен- 15 ты памяти (ЭП), каждый из которых состоит из двух транзисторов 1 и 2, первого и второго нагрузочных резисторов 3 и 4, двух ограничительных диодов 5, 6, третьего и четвертого нагрузочных резисторов 7 и 8, адресную шину 9, шину 10 хранения, разряд.— ные шины 11, 12, источник 13 тока хранения, генератор 14 фототока.

Генераторы фототока 15 и 16 отражают суммарный ток р-п-транзисторов переходов ЭП, возникающий из-за воз действия ДФ.

ОЗУ работает следующим образом.

В режиме хранения сопротивление нагрузок плеч ЭП определяется резисторами 3, 4, так как источник 13 задает через каждый ЭП такой ток, что на резисторе 3 или 4 открытого плеча

35 триггера падает напряжение, равное примерно 0,5 V+, где V» — падение напряжения на открытом диоде 5, 6.

В результате диод 5 или 6 открытого 4О плеча оказывается под таким же прямым смещением 0,5 V, так что ток через него практически не течет. Падение напряжения на нагрузке закрытого плеча триггера определяется током базы открытого транзистора 1 или 2.

Этот ток в р раз, где p — коэффициент усиления транзистора по току, меньше тока его коллектора, поэтому и падение напряжения на резисторе 3 или 4 закрытого плеча ЭП в .II раз меньше, т.е. 0,5 V"/ p . В результате диод 5 или 6 закрытого плеча окажется под смещением, близким к нулевому;. и ток через него также не протекает.

Номиналы резисторов 7, 8 более чем на порядок меньше номиналов резиСторов 3 и 4, поэтому падением напряжения на них можно пренебречь. Таким

2 4 образом, разность потенциалов коллекторов транзисторов 1 и 2 составит

6VX = 0,5 V (i — — ) = 0,5 V

В режиме выборки повышается по тенциал адресной шины 9. В результате повышается и потенциал шины 10.

Через первые эмиттеры транзисторов 1 и 2 ток перестает протекать.

Ток записи или считывания протекает через второй эмиттер одного из транзисторов 1 и 2. При этом транзистор работает в квазинасыщенном режиме, т.е. его коллекторный переход оказывается под прямым смещением. Однако наличие ограничительных диодов 5 и 6 не позволяет доСтигнуть этому прямому смещению величины V» обеспечивая высокое быстродействие ЭП. Так как номинал резисторов 7 и 8 мал, то падение напряжения на них в режиме выборки 0,15-0,2 В не оказывает существенного влияния на быстродействие

ЭП из-за увеличения степени насыщения открытого транзистора.

При кратковременном воздействии на микросхему памяти ДФ обращение к ней запрещается, т.е. все ЭП находятся в режиме хранения. Воздействие ДФ вызывает генерацию заряда в р — п-переходах транзисторов и, следовательно, возникновение фототоков, которые отражены генераторами

15 и 16. Величина этих токов может быть значительно больше величины тока хранения ЭП более чем в 2 раза.

Фототоки возникают независимо от состояния ЭП одновременно в обоих его плечах, вызывая увеличение падений напряжений на резисторах 3 и 4 до тех пор, пока не откроются диоды 5 и 6.

Дифференциальные сопротивления открытых диодов 5 и 6 малы, поэтому небольшой ток хранения, задаваемый источником 13 тока, не в состоянии обеспечить на диодах 5 и 6 перепад напряжений, достаточный для сохранения информации. Резисторы 7, 8 обеспечивают увеличение общего дифференциального сопротивления нагрузки, так как они включены последовательно с диодами 5, 6. Однако только увеличение сопротивления нагрузок ЭП недостаточно для сохранения в нем информации, так как по-прежнему мал ток хранения. Для того чтобы ЭП сохранил записанную в нем информацию, при

v = (z. + -х — -" R) — х хР, и P

«R + liV = - - к, Т + Ix ток генератора 14; токи генераторов 15, 16; ток источника 13; сопротивление резисторов 7, 8; разница падений напряжений на прямосмещенных диодах 5, 6 открытого и saкрытого плеч триггера ЭП; количество ЭП устройства.

20

1

За счет перепада напряжений дЧх создаваемого током генератора 14, на резисторах 7 и 8 в ЭП сохранится информация во время воздействия ДФ.

Ъ

При отсутствии резисторов 7 и 8 (R = О) информация не сохраняется, I поскольку дV О.

По окончанйи воздействия ДФ гене30 рация в р — n-переходах транзисторов прекращается, т.е. выключаются генераторы фототока 15 и 16. Одновременно с ними отключается генератор 14.

Составитель А. Дерюгин

Техред Л.Олийнык Корректор М. Шароши Редактор H. Недолуженко

Заказ 4878/50 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101

15011 воздействии ДФ включается генератор

14 фототока, который может быть выполнен, например, на фототранэисторе.

Ток генератора 14 должен быть больше

5 токов генераторов 15, 16 всех ЭП.

В результате на резисторе 7 или 8 открытого плеча триггера ЭП падение напряжения будет больше на величину

62 6

Устройство переходит к работе в обычных режимах. . Формула изобретения

Оперативное запоминающее устройство, соцержащее источник тока хранения, элементы памяти, каждьп из которых состоит из двух транзисторов, двух нагрузочных резисторов, цвух ограничительных диодов, аноды которых соединены с первыми выводами соответствующих нагрузочных резисторов, а катоды — с вторыми выводами данных резисторов и соответственно с коллекторами первого и второго и базами второго и первого транзисторов, первые эмиттеры которых подключены к соответствующим разрядным шинам устройства, а вторые — к шине хранения устройства и к первому выводу источника тока хранения, второй вывод которого подключен к шине нулевого потенциала устройства, о т л и ч а ющ е е с я тем, что, с целью повышения устойчивости устройства к воздействию кратковременных дестабилизирующих факторов, в него введен генератор фототока, первый и второй выводы которого соединены с соответствующими выводами источника тока хранения, и в каждый элемент памяти — третий и четвертый нагруэочные резисторы, первые выводы которых соединены с анодами первого и второго ограничительных диодов соответственно, а вторые выводы подключены к адресной шине устройства.