Матричный накопитель для оперативного запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике и предназначено для использования в цифровых устройствах. Целью изобретения является снижение потребляемой мощности. Поставленная цель достигается за счет того, что в матричном накопителе у поверхности эпитаксиального слоя 2 р-типа между областями 3 N<SP POS="POST">+</SP> -типа и вторыми боковыми поверхностями 12 канавок сформированы области 13 р<SP POS="POST">+</SP> - типа, причем полупроводниковая подложка 1 и первые полупроводниковые слои 7 выполнены из материала р<SP POS="POST">+</SP> - типа проводимости, а вторые полупроводниковые слои 9 выполнены из материала N - типа проводимости. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИ К

РЕСПУ БЛИН

„„SU„„!506482 А 1 (Н 4 С 11 С 11/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Фиг.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4247903/24-24 (22) 25.05.87 (46) 07.09.89. Бюл. М ЗЗ (71) Московский авиационный институт им. Серго Орджоникидзе (72) Н.А. Аваев (53) 681.327.66(088.8) (56} Аваев Н.А., Наумов Ю,Е. Элементы сверхбольших интегральных схем.—

М.: Радио и связь, 1986.

Авторское свидетельство СССР

Р 1361628, кл. G 11 С 11/40, 1986. (54) МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ОПЕРАТИВНОГО ЗАПОМИНАКЗЦЕГО УСТРОЙСТВА (57) Изобретение относится к микроэлектронике и предназначено для использования в цифровых устройствах, Целью изобретения является снижение потребляемой мощности. Поставленная цель достигается за счет того, что в матричном накопителе у поверхности эпитаксиального слоя 2 р-типа между

+ областями 3 и -типа и вторыми боковыми поверхностями 12 канавок сформированы области 13 р -типа, причем

+ полупроводниковая подложка 1 и первые полупроводниковые слои 7 выполнены из материала р -типа проводимости, + а вторые полупроводниковые слои 9 выполнены из материала и-типа проводимости. 4 ил °

150648

10 разом.

Подложка и эпитаксиальный слой соединяются с нулевой шиной. Информация в запоминающем элементе хранится в виде напряжения на запоминающих конденсаторах, образованных соответственно слоями 6, 7, 8 и 7, 5, 2, 1.

Области 1 и 3 п -типа и каждом запо+ минающем элементе вместе с расположенной между ними областью р-типа

Изобретение относится к микроэлектронике и предназначено для использования в цифровых устройствах.

Цель изобретения — уменьшение

5 потребляемой мощности.

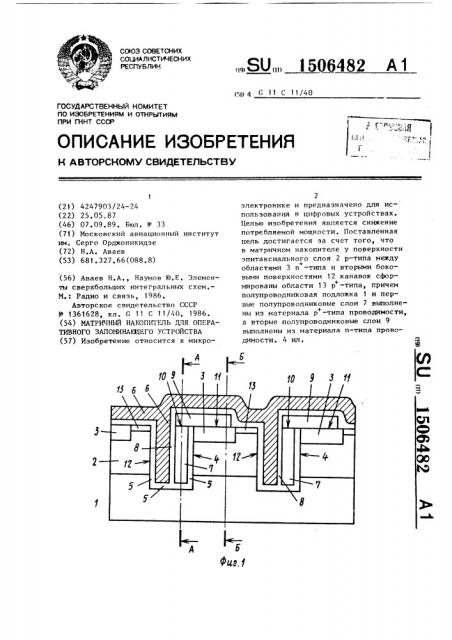

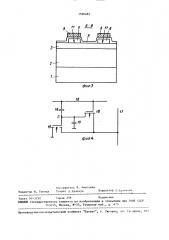

На фиг. 1 представлен матричный накопитель, поперечный разрез структуры н направлении строки; на фиг. 2 — разрез А-A на фиг ° 1; на фиг ° 3 — разрез Б-Б на фиг. i; на фиг. 4 — эквивалентная схема запоминающего элемента матричного накопителя .

Матричньп накопитель содержит по- 15 лупроводниковую, например, кремни+ еную подложку 1 и -типа и эпитаксиальный слой 2 р-типа, у поверхности

+ которого содержатся области 3 п -типа, являющиеся шинами столбцов. 20

В эпитаксиальном слое 2 выполнены канавки глубиной не менее толщины слоя 2, первые боконые поверхности 4 которых граничат с областями 3. На поверхностях канавок и эпитаксиального слоя 2 нанесены последовательно первые слои 5 диэлектрика и металлические электроды 6, являющиеся шинам« с-.рок. Между металлическими электрода .r 6 и первой б.,ковой по- 30 нерхностью 4 каждой канавки содержлтся первые полупроводниковые слои

/ и -тш а, отделенные от металличесих электродов 6 вторыми слоями 8 диэлектрика (например, двуокиси крем- 35 ния). Между поверхностью эпитаксиального слоя 2 ч металлическими электродам 6 расположены изолированные от них слоями 5 вторые полупроводниковые слои 9 и-типа, образующие оми- 40 че кие контакты 10 с первыми полупронодниковькги слоями 7 и омические контакты 1 1 с областями 3 n+-типа. У поверхности эпитаксиального слоя между областями 3 и †ти и вторыми боковы- 45 ми поверхностями 12 канавок сформированы области 14 р+-типа, Накопитель работает следующим об2 4 (частью эпитаксиального слоя) и первым полупроводниковым слоем 7 образуют МДП-транзистор с индуцированным каналом и-типа. Слои 7, 9, 3 и 6 образуют соответственно исток,, канал, сток и затвор второго МДП-транзистора со встроенным каналом и-типа.

Слой 13 р -типа предотвращает нозФ никновение параэитной связи между п -областью 3 и подложкой 1 вдоль поверхности подложки и второй боковой поверхности 12 канавки.

Таким образом, запоминающий элемент имеет эквивалентную схему (фиг. 4). На схеме обозначено; 14— запоминающий конденсатор, образованный слоями 6, 8, 7; 15 — запоминающий конденсатор, образованный слоями 7, 5, 2, 1; 16 — шина строки, 17 — нина столбца, 18 — MjgI-транзистор со встроенным каналом п-типа, образованный слоями 7, 9, 3 и 6 и предназначенный для записи информации, 19 — МДП-транзисгор 6 с индуциронанным каналом п-типа, образованный слоями 1, 2, 3, 7 и предназначенный для считывания.

В режиме записи на шину 17 столбца подается либо низкое напряжение логического "0" (V = О), либо положительное напряжение логической 1 (U ), а на шину 16 выбранной строки — положительное или нулевое напряжение U„»„ J Uîòñ где U„— модуль напряжения отсечки транзистора 18. IIa невыбрапных шинах строк напряжение отрицательно. В ныбра «ом запоминающем элементе транзистор 18 отпирается и н запоминающем узле С (фиг. 4) устанавливается напряжение U или U . . По окончании .записи и при переходе н режим хранения на шине 16 строки скачкообразно устанавливается отрицательное напряжение П „ хо . В точке С (фиг. 4) напряжени,. становится равным U „= — (Ux»z— — Ux х ) С + /(С «+ С, ) н слу хранения логического "0" или U = U (Ux дя- Ux x )С /(С1 + С 5) н случае хранения логической "1", где С1, С вЂ” емкости конценсаторов 14 и 15.

Транзистор 18 запираегся, для чего достаточно " х.хр + Псо ) 11„с . Транзистор 19 также закрыт, для этого необходимо Пс (П„,, где U<> — по1 роговое напряжение„ При считывании на шинах 17 столбцов предварительно устанавливают положительное напряже15064

10

20

25 п-типа проводимости.

AA 6 10 9

Фиг.2

5 ние (например, U ), которое по окончании импульса установки поддерживается емкостью шины. Затем повышают напряжение на шине 16 выбранной стро5 ки до величины, промежуточной между о»»p H U» ао э например до U„« ц».за 0,5(Б» ц — ц» «р ). В результате в точке С напряжение становится равйым или

При этом транзистор 18 ос гается закрытым, если выполнить условие

-U„,„ + Uco ) У . Транзистор 19 в случае считывания логического 0" должен быть закрыт (V „ < V„. ), гогда напряжение на шине 17 столбца остается неизменным. При считывании логической "1" U o U„ транзистор 19 отпирается и напряжение на шине 17 понижаегся, что воспринимается усилителем считывания, подключ е иным к ши не ° формула изобретения

Матричный накопитель для оперативного запоминающего устройства, содержащий полупроводниковую подложку с расположенным на ней эпигаксиальным слоем р-типа, в приповерхностном слое которого расположены области и+-типа, образующие шины столбцов матричного накопителя, в эпитаксиальном слое р-типа выполнены канавки, глубина которых перекрывает толщину эпитаксиального слоя р-типа, первые боковые поверхности канавок граничат с областями и -типа, на поверхностях

+ канавок и эпитаксиального слоя р-типа нанесены последовательно первые слои диэлекгрика и мегаллические электроды, образукщие шины строк матричного накопителя, между металлическими электродами и первой боковой поверхностью каждой канавки расположены первые полупроводниковые слои, отделенные от металлических элек гродов вторыми слоями диэлектрика, между поверхностью эпитаксиального слоя р-типа и металлическими элекгродами расположены изолированные от них вторые полупроводниковые слои, образукицие контакты с первыми полупроводниковыми слоями, о т л и ч а ю щ и й-, с я тем, что, с целью уменьшения потребляемой мощности, в матричном накопителе у поверхности эпитаксиальI ного слоя р-типа между областями п -типа и вторьпя боковыми поверхнос- тями канавок сформированы области р -типа, причем полупроводниковая подложка и первые полупроводниковые

+ слои выполнены из материала и -типа проводимости, а вторые полупроводниковые слои выполнены из материала

1506482 фиГ3

17

Составитель Л. Лмусьева

Редактор Н. Тупица Техред A.Кравчук Корректор O.Кравцова

Заказ 5443/52 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская иаб., д. 4!5

Производственно-издательский комбинат "Патент", г. ужгород, ул. Гаг арина, 101