Арифметико-логическое устройство

Иллюстрации

Показать всеРеферат

Изобретение касается вычислительной техники. Целью изобретения является упрощение устройства. Устройство содержит одноразрядные многофункциональные блоки 1 и блок 2 формирования переносов. Каждый блок 1 содержит многофункциональный узел 3, управляемый узел 4 инверсии и сумматор по модулю два 6. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И1 (5Р 4 G 06 F 7/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

13 и 1319

8

Ю Q

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГИНТ СССР

1 (21) 4354847/24-24 (22) 04.01.88 (46) 15. 10..89. Бюл. И 38 (72) И.Ф. Грачев и С.А. Геращенко (53) 681.325 (088.8) (56) Экспресс-информация. Вычислительная техника, 1972, ((23, с.23-38 .

Мищенко В.А. и др. Многофункциональные автоматы и элементная база цифровых ЭВМ. М.: Радио и связь, 1981, с. 208, рис. 9 4.

2 (54) АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО (57) Изобретение касается вычислительной техники. Целью изобретения является упрощение устройства. Устройство содержит одноразрядные многофункциональные блоки 1 и блок 2 формирования переносов. Каждый блок 1 содерлыт многофункциональный узел 3, управляемый узел 4 инверсии и сумматор 6 по модулю два. 1 ил, О

3 151516

Изобретение относится к вычислительной технике.

Целью изобретения является упрощение устройства.

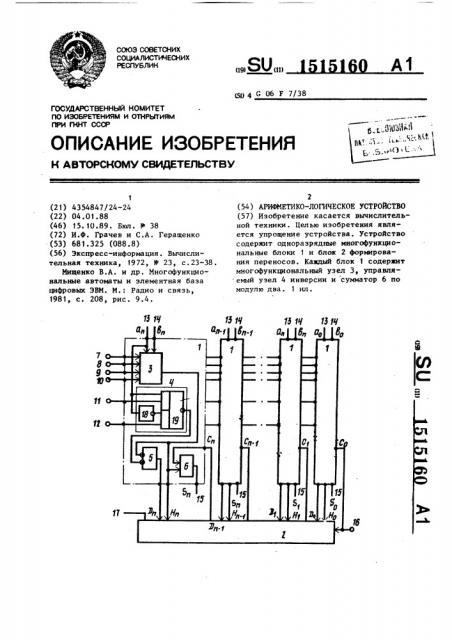

На чертеже представлена блок-схема арифметико-логического устройства.

Устройство содержит одноразрядные многофункциональные блоки 1 и блок

2 формирования переносов. Каждый блок 1 содержит многофункциональный узел 3, управляемый узел 4 инверсии, элемент НЕ-И 5 и сумматор 6 по модулю два. Устройство содержит также управля«ощие входы 7 — 12, входы 13, 14 разрядов первого и второго операндов, выходы 15 разрядов результата, вход 16 перенс .л, выход 17 переноса.

Узел 4 может быть выполнен, например, с помощью элемента НЕ 18 и элемента

И вЂ И-НЕ 19.

Устройство работает следующим образом.

При подаче шестнадцати различных комбинаций сигналов на управляющие входы 7-10 на выходах узлов 3 реализуются все булевы функции от соотвествующих разрядов оперлндов, пода-, ваемых на входы 13, 14. Для некото«эсго i-го разряда при комбинации 00 0 рел. III3уе-,ся функция тож «ествен««ь!и О, гри ООО! —. a, b;, 0010 — à b,, 0011 л;, 0100 — л; Ъ„0101 — b;, 0110 л;Ь,Va,b,, 0111 — а; V Ь;, 1РОΠ— а Ь, 1001 — л; Ь; ч à b,, 1010 — b,, 1011 л; ч Ь,, 1100 — а;, 1101 — а; V b,, 1110 — л Ч Ь,, 1111 — тожденственная 1.

Для реализации 3TIIx функций Устрo«I 40 ством подлется комбинлция 00 на уп-. равляющие JIxo«I«! 11, 12 и нулевой сигнал «л вход 16. При этом на выходе элементы И-ИЛИ-НЕ 19 формируется сигнал "1" и поэтому нл выходе элемента

НЕ-И 5 — сигнал "0", т. е. функция генерации переноса С; имеет нулевое значение и поэтому переносы блоком 2 не вырабатываются и не поступают на входы сумматоров 6 по модулю два, а следовл тельно, информация с выхода каждого уэлл 3 пр оходит Hà I «DI îäû 1 5 без изменения и устройство реализует одну пз вышеперечисленных функций, определяемую комбинацией сигналов на

55 управляющих входах 7-10 .

Для выполнения операции сложения на управляющие входы 7 — 10 подлется комбинация 0110, нл упрлвляюшие рходы 11, 12 — комбинация 10, а на вход

16 — сигнал "О". Каждый узел 3 формирует на своем выходе полусумму разрядов слагаемых: р = а;Ь; Ча;Ь = аЮЬ; передаваемую на вход сумматора 6 по модулю два, вход распространения переносов блока 2 и на вход элемента

HE — È 5. Элемент И-ИЛИ-НЕ 19 реализует функцию А = а, а элемент НЕ-И 5 ! функцию генерации переносов С = p; A;.

Блок 2 вырабатывает переносы в соответствии с выражением с „ = G ч р с., !

+! 1 ! поступающие на вторые входы сумматоров 6 по модулю два, формирующих сумму согласно выражению в, = p;Q+ с, = à Q+ Ь (+)

g+, с, на выходах 15 результата.

При вычитании из первого операнда второго устройство настраивается по управляющим входам на выполнение действий, аналогичных суммированию первого операнда с дополнением второго операнда (инверсией второго операнда плюс единица дополнения). Для этого на управляющие входы 7-10 подается комбинация 1001, на управляющие входы 11, 12 — комбинация 10; единица дополнения подается единичным сигналом на вход 16. Многофункциональный узел 3 формирует на выходе полусумму значения разряда первого операнда и инверсии значения разряда второго операнда: р;= à bjV a;b а Q+ b,«, элемент И-ИЛИ-HE 19 реализует функцию А =- .а,, а элемент НЕ-И !

5 — функцию G, = р; Aj = (а Ь ч а Ь.„)а;=

= а,b, . Блок 2 и сумматоры 6 по модулю два работают так же, как и при сложении. На выходах 15 формируется результат в соответствии с выра— жением s,= р (+) с, = а;О+ b, Ю с; .

При вычитании из второго операнда первого устройство настраивается по управляющим входам на выполнение действий, аналогичных суммированию второго операнда с дополнением пе вого операнда (инверсией первого операнда плюс единица дополнения).

Для этого на управляющие входы 7-10 подается комбинация 1001, на управляющие входы 11, 12 — комбинация 01; единица дополнения подается единичным сигналом на вход 16. Многофункциональный узел 3 формирует на выходе полусумму значения разряда второго оп =I анда и инверсии значения разряда первого операнда р; = а Ь V а Ь

1 I 1

b; 0+ а . Элемент HE 18 реализует инвепсию значения разряда первого

15151 формула изобретения

Составитель В. Березкин

Редактор M. Циткина Техред Л, Олийнык Корректор В. Гирняк

Заказ 6277/46 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 слагаемого а, а элемент И-ИЛИ-HE

19 — инверсию этой инверсии, в результате на выходе элемента И-ИЛИ-НЕ

19 реализуется функция А = а;, а на выходе элемента НЕ-И 5 — функция

G,= p,A;= (а,Ъ ч a;b;)a = Ь;а . Блок

2 и сумматоры 6 по модулю два работают так же, как и при сложении. На выходах 15 формируется результат в соответствии с выражением s = Ь (+ i3à.0+c .

1 1 1 1

Арифметико-логическое устройство, содержащее блок формирования переносов и одноразрядные многофункциональные блоки, каждый из которых содержит многофункциональный узел и сумматор по модулю два, выход которого соеди- 20 нен с выходом суммы данного одноразрядного многофункционального блока и является выходом результата соответствующего разряда устройства, первый вход сумматора по модулю два со- 25 единен с выходом многофункционального узла того же одноразрядного многофункционального блока, информационные входы многофункционального узла соединены с первым и вторым информа- 30 ционными входами соответствующего одноразрядного многофункционального блока и являются входами соответствующих разрядов первого и второго операндов устройства, управляющие входы

35 многофункционального узла соединены с управляющими входами с первого по четвертый соответствующего одноразрядного многофункционального блока и являются управляющими входами соответ- 40 ственно с первого по четвертый устройства, втброй вход сумматора по модулю два соединен с входом переноса

60 6 соответствующего одноразрядного многофункционального блока и для всех одноразрядных многофункциональных блоков, кроме первого, соединен с выходами предыдущих разрядов блока формирования переносов, вход начального переноса которого соединен с входом переноса устройства и входом переноса первого одноразрядного многофункционального блока, выход последнего разряда блока формирования переносов соединен с выходом переноса устройства, выход многофункционального узла каждого одноразрядного многофункционального блока является выходом распространения переноса этого блока и соединен с входом распространения переноса соответствующего разряда блока формирования переносов, вход генерации переноса которого соединен с выходом генерации переноса соответствующего одноразрядного многофункционального блока, пятый и шестой управляющие входы которого .соединены соответственно с пятым и шестым управляю-. щими входами устройства, о т л и ч аю щ е е с я тем, что, с целью упрощения устройства, каждый одноразрядный многофункциональный блок содержит управляемый узел инверсии и элемент

НЕ-И, входы которого соединены с выходами многофункционального узла и узла управляемой инверсии, а выход подключен к выходу генерации переноса этого одноразрядного многофункционального блока, первый информационный вход которого соединен с информационным входом узла управляемой инверсии, управляющие входы которого соединены с пятым и шестым управляющими входами этого одноразрядного многофункционального блока.