Матричное устройство для возведения в квадрат

Иллюстрации

Показать всеРеферат

Устройство относится к вычислительной технике и позволяет вычислять квадрат аргумента и осуществлять контроль вычислений по неразрешенным кодам результата. Устройство содержит элементы И 1 ячеек матрицы, определяющие всевозможные конъюнкции значений различных разрядов аргумента, сумматоры 2 ячеек матрицы, вычисляющие квадрат аргумента путем нахождения взвешенной суммы значений конъюнкций и разрядов аргумента. Устройство содержит также блок 3 свертки по модулю семь, определяющий остаток от деления кода результата на семь, блок свертки по модулю два 5, и элемент ИЛИ 4. ЭЛЕМЕНТ НЕ 6 И ЭЛЕМЕНТ И 7 ПО СИГНАЛАМ С ВЫХОДОВ БЛОКА 5 И ЭЛЕМЕНТА 4 ИДЕНТИФИЦИРУЮТ КОДЫ ОСТАТКА 3, 5 И 6, УКАЗЫВАЮЩИЕ НА НЕРАЗРЕШЕННЫЕ КОДЫ РЕЗУЛЬТАТА И СООТВЕТСТВЕННО НА НЕПРАВИЛЬНОЕ ФУНКЦИОНИРОВАНИЕ УСТРОЙСТВА. 1 ИЛ.

CCN03 СОВЕТСКИХ

СОЦИАЛИСтич ваших

РЕСПУБЛИК (59 4 С 06 Р 7/552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

lH А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

AO ИЭСЪРЕТЕНИЯМ И О НРЫТИЯМ

ПРИ ГКНТ СССР (21) 4401437/24-24 (22) 31.03.88 (46) 07.11.89. Бюл. Р 41. (71) Одесский политехнический институт (72) АоВа Дрозд, Е.Ла Полин, А.М. Романкевич, В.Н. Валуйский и C.A. Нестеренко (53) 681.325(088,8) (56) Авторское свидетельство СССР

|tt- 842804, кл. (; 06 J 7/552, 1979.

Авторское свидетельство СССР

Р 1439583, кл. Г 06 Р 7/552, 1985. (54) МАТРИЧНОЕ УСТРОЙСТВО ЦЗИ ВОЗВЕДЕНИЯ В КВАДРАТ (57) Изобретение относится к вычислительной технике и позволяет вычислять квадрат аргумента и осуществлять контроль вычислений по неразрешенным

„„Я0„„1520512 — А ) 2 кодам результата. Устройство содер жит элементы И 1 ячеек матрицы, определяющие всевозможные конъюнкции значений- различных разрядов аргумента, сумматоры 2 ячеек матрицы, вычисляющие квадрат аргумента путем нахощцения взвешенной суммы значений конъюнкций и разрядов аргумента.

Устройство содержит также блок 3 свертки по модулю семь, определяющий остаток от деления кода результата на семь, блок 5 свертки по модулю два и элемент ИЛИ 4. Элемент НЕ 6 и элемент И 7 по сигналам с выходов блока 5 и элемента 4 идентифицируют коды остатка 3, 5 и 6, указываюпцсе на неразрешенные коды результата и соответственно на неправильное функционирование устройства. 1 ил.

1520512

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Цель изобретения — повышение достоверности функционирования.

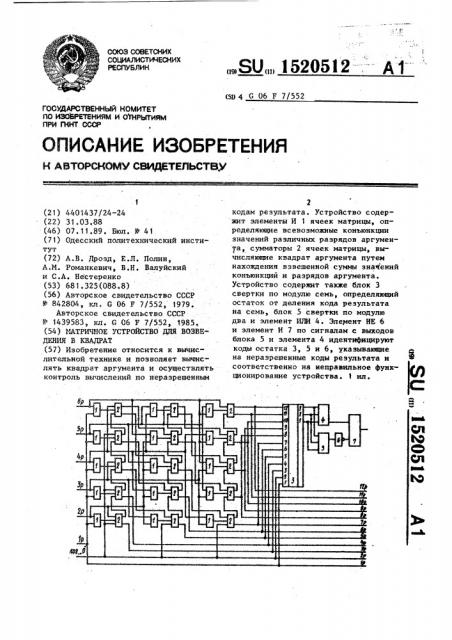

На чертеже представлена структурная схема устройства для п б.

Устройство содержит элементы

И 1, сумматоры 2, блок 3 свертки по модулю семь, элементы ИЛИ 4, блок 5 свертки по модулю два, элемент НЕ б и элемент И 7.

Устройство работает следующим образом.

Разряды операнда поступают на входы устройства. При этом первый разряд операнда подается на первый выход устройства, второй выход которого постоянно принимает значение логического нуля. Кроме того, первый разряд Ip подается на первые входы элементов И 1 первого столбца, на вторые входы которых поступают соответственно последующие разряды операнда 2р, Зр, 4р, 5р и бр. На выходах элементов И 1 первого столбца образуются EGHú HK éH 1р 2р, 1р Зр, 1р 4р, 1р 5р и 1р бр, которые поступают на вторые входы соответствующих сумматоров 2 первого столбца.

Через первые входы и выходы этих сум-. маторов 2, как и сумматоров 2 последующих столбцов, распространяется сигнал переноса (кроме первого входа 35 первого сумматора 2, который, как и в последующих столбцах, занулен, а также кроме первого выхода последующего пятого сумматора 2, с выхода которого, как и во втором столбце, 4Î сигнал переноса поступает на третий . вход четвертого сумматора 2 следующего столбца).

Третьи входы четных сумматоров первого столбца занулены, а на третьи 45 входы первого, третьего и пятого суматоров 2 первого ° столбца поступают разряды операнда, соответственно 2р, 3р и 4р.

При этом определяются третий и четвертый разряды результата, поступающие с вторых выходов первого и второго сумматоров 2 первого столбца на третий ы четвертый выходы устройства. Сигналщ суммы с вторых выходов третьего, четвертого и пятого сумматоров 2 первого столбца посту.пают, как и сигналы суммы с соответствующих сумматоров 2 второго столбца, на третьи входы соответственно первого, второго и третьего сумматоров следующего столбца. Элементы

И 1 второго столбца вычисляют в соответствии с заведенными на их входы разрядами операнда конъюнкции 2р Зр, 2р 4р, 2р 5р, 2р бр и 4р 5р, которые поступают на вторые входы сумматоров 2 второго столбца. На третий вход пятого сумматора 2 второго столбца поступает разряд операнда 5р.

При этом определяются пятый и шестой разряды результата, поступающие с вторых выходов первого и второго сумматоров 2 второго столбца на пятый и шестой выходы устройства.

Элементы И 1 третьего столбца определяют в соответствии с заведенными на их входы разрядами операнда конъюнкции Зр 4р, Зр 5р, Зр. бр, 4р бр и 5р бр, которые поступают на вторые входы соответствующих сумматоров 2 третьего столбца. На третий вход пятого сумматора 2 третьего столбца поступает разряд операнда бр. При этом определяются последую1 щие разряды результата, поступающие с вторых выходов сумматора 2 третьего столбца и первого выхода пятого сумматора 2 третьего столбца соответственно на выходе устройства с седьмого по двенадцатый.

Кроме того, все разряды результата поступают соответственно на входы блока 3 свертки по модулю семь. При этом блок 3 определяет остаток от деления результата на семь. Код остатка поступает на входы элемента

ИЛИ 4, а также на входы блока 5 свертки по модулю два. Блок 5 принимает единичное значение при нечетном количестве единиц в коде остатка.

Зто значение инвертируется элементом

НЕ 6 и устанавливает выход элемента

И 7 в нулевое значение по первому входу. По второму входу элемент И 7 устанавливается в ноль при нулевом коде остатка„ выявляемом элементом

ИЛИ 4. Таким образом, все коды остатка, имеющие четное количество единиц, отличное от нуля, установит выход элемента И 7, являющийся контрольным выходом устройства в единичное значение.

Правильно вычисленный результат возведения операнда в квадрат не может иметь кода остатка с четным количеством единиц,,отличным от нуля, 20512

15 поэтому при правильной работе устройства его контрольный выход принимает нулевое значение, а возникновение единичного значение на контрольном выходе устройства указывает на его неправильное функционирование.

Формула и э обретения

Составитель А.дрозд

Техред А.Кравчук

Корректор Л. Бескид

Реда кт ор В . Данко

Заказ 6758/49 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101

Иатричное устройство для возведения в квадрат, содержащее элементы

НЕ и И, а также матрицу ячеек из и/2 столбцов и и-1 строк, где n— четное число, разрядность операнда, причем каждая ячейка содержит сумматор и элемент И, первый выход сумматора i-й строки (i=1, п-2) каждого столбца соединен с первым входом сумматора (i+1)-й строки того же столбца матрицы, выход элемента И каждой ячейки соединен с вторым входом сумматора этой же ячейки, первый выход сумматора (n-1)-й строки j-ro столбца ()=1, n/2-1) соединен с третьим входом сумматора (и+2)-й строки (j+1)-го столбца, второй выход сумматора i-й строки (i=3, и-1)-го столбца соединен с третьим входом сумматора {i-2)-й строки (j+1)-го столбца, первые входы элеыевтов И деевых л-к строк

j-го столбца (3 1, и/2) объединены между собой и подключены к входу

j-го разряда операнда устройства, второй вход элемента И 1-й строки

j-го столбца (i=1 n-i) соединен с входом (j+1)-ro разряда операнда устройства, первые входы элементов И последних (j-1)-х строк j ro столбца (для j > f) объединены между собой и подключены к входу (n/2+j)-го разряда операнда устройства, второй вход элемента И i-й строки j-го столбца (i=j+1, п-1, j ) 1) соединен

1О

45

6 с входом (j+i-n/2)-ro разряда опера."сда устройства, третий вход сумматора (2j-1)-й строки первого столбца подключен к входу (j+1)-ro разряда операнда устройства ° а третьи входы сумматоров первых строк первого столбца и первые входы сумматоров первых строк всех столбцов подключены к входу логического нуля устройства, третий вход сумматора (и-1)-й строки j-ro столбца (j ) 1) соединен с входом (j+n/2)-го разряда операнда устройства, первый и второй выходы устройства соединены соответственно с входом первого разряда операнда устройства и входом логического нуля устройства, вторые выходы сумматоров первой и второй строк

j-го столбца подключены к (2)+1)-му и (2j+2)-му входам устройства соответственно, второй выход сумматора

i-й строки и/2-ro столбца соединен с (+п)=м выходом устройства, 2п-й выход которого соединен .с первым выходом сумматора (п-1)"й строки и/2-ro столбца, выход элемента НЕ соединен с первым входом элемента И, выход которого является контрольным выходом устройства, о т л и ч а ющ е е с я тем, что, с целью повышения достоверности функционирования, в него введены блок свертки по модулю семь, элемент ИЛИ и блок свертки по модулю два, причем информационные выходы устройства соединены с входами блока свертки по модулю семь, первый, второй и третий выходы которого соединены соответственно с одноименными входами элемента ИЛИ и соответствующими входами блока свертки по модулю два, выход которого соединен с входом элемента НЕ, а выход элемента ИЛИ подключен к второму входу элемента И.