Устройство для компенсации реактивной мощности

Иллюстрации

Показать всеРеферат

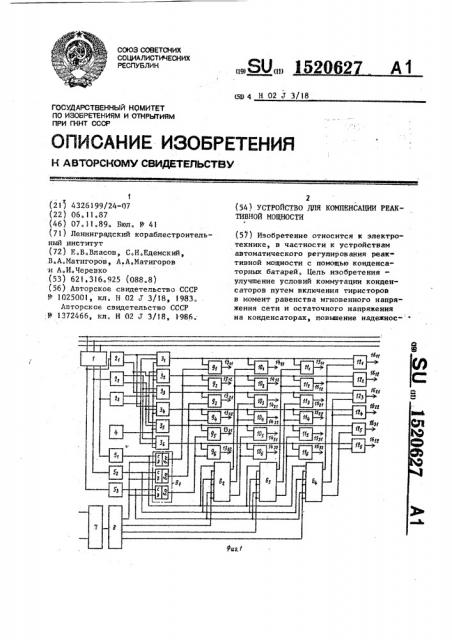

Изобретение относится к электротехнике, в частности к устройствам автоматического регулирования реактивной мощности с помощью конденсаторных батарей. Цель изобретения - улучшение условий коммутации конденсаторов путем включения тиристоров в момент равенства мгновенного напряжения сети и остаточного напряжения на конденсаторах, повышение надежности и точности регулирования реактивной мощности в электрических сетях. Устройство содержит четыре секции конденсаторных батарей с соотношением мощностей 1:2:4:8, конденсаторы каждой секции соединены в треугольник и подключены в узел нагрузки посредством последовательно соединенных с ними встречно-параллельных тиристоров. Блок управления устройством содержит трехфазный синхронизирующий трансформатор 1, формирователи 2<SB POS="POST">1</SB>-2<SB POS="POST">3</SB> импульсов, логические элементы 3<SB POS="POST">1</SB>-3<SB POS="POST">6</SB>, генератор 4 высокочастотных импульсов, нуль-органы 5<SB POS="POST">1</SB>-5<SB POS="POST">3</SB>, блоки 6<SB POS="POST">1</SB>-6<SB POS="POST">4</SB> задержки сигналов управления, каждый из которых состоит из трех D-триггеров, датчик 7 реактивной мощности, блок 8 логики, усилительно-коммутирующие устройства 9<SB POS="POST">1</SB>-9<SB POS="POST">5</SB>, 10<SB POS="POST">1</SB>-10<SB POS="POST">6</SB>, 11<SB POS="POST">1</SB>-11<SB POS="POST">6</SB>, 12<SB POS="POST">1</SB>-12<SB POS="POST">6</SB>. 5 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

SU» 152062 са 4 Н 02 .7 3/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPbITHRM

ПРИ ГКНТ СССР

1 (21) 4326199/24-07 (22) 06.11.87

{46) 07.11.89. Вюл. № 41 (71) Ленинградский кораблестроительный институт (72} F..Â.Âëàñîâ, С.Н.Едемский, В.А.Матигоров, А.А.Матигоров

-и А.И.Черевко (53} 621.316.925 (088.8) (56) Авторское свидетельство СССР № 1025001, кл. Н 02 Г 3/18, 1983.

Авторское свидетельства СССР

-№ 1372466, кл. Н 02 Г 3/18, 1986.

2 (54) УСТРОЙСТВО ДЛЯ КОМПКНСАЦИИ РКАКТИВНОЙ МОЩНОСТИ (57) Изобретение относится к электротехнике, в частности к устройствам автоматического регулирования реактивной мощности с помощью конденсаторных батарей. Цель изабретенияулучшение условий коммутации конденсаторов путем включения тнристоров в момент равенства мгновенного напряжения сети и остаточного напряжения на конденсаторах, повышение надежнос1520627 ти и точности регулирования реактив" най мощности в электрических сетях.

Устройство содержит четыре секции конденсаторных батарей с соог!»Ошен!»ем мощностей 1:2:4:8, конденсаторы каждой секции соединены в треугольник и поцключены в узел нагрузки посредством последовательно соединенных с ними встречно-параллельных тиристоров. Блок управления устройством содержит трехфазный синхронизирующий т" 1 трансформатор 1, формирователи

?,-2з импульсов, логические элементы 3„-36,, генератор 4 высокочастотных импульсов, нуль-органы 5<--5З, блоки 6 -6 . задержки сигналов управления, каждый иэ которых состоит из трех D-триггеров, датчик 7 реактивной мощности, блок 8 логики, усилительно-коммутирующие устройства

9»-9, 10Ä-106, 11q-11, 12)-126.

5 ил.

Изобретение относится к электротехнике, в частности к устройствам автоматического регулирования реактивной мощности с помощью конденсаторных батарей.

Цель изобретения — улучшение условий коммутации конденсаторов путем включения тиристоров в момент равенства мгновенного напряжения сети и остаточного напряжения на конденсаторах, повьппение надежности и точности регулирования реактивной мощности в электрических сетях. 30

На фиг, 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 — схема силовой части уст-. ройства; на фиг. 3 — схема усилительно-коммутирующего устройства; на фиг. 4 и 5 — временные диаграмь>ы,поясняющие принцип работы устройства.

Устройство содержит трехфаз!»ьп» синхронизирующий трансформатор 1,формирователи 2„-2 q синхроимпульсов, 40 логические элементы ЗИ 3< -36, генератор 4 высокачастотиых импульсов, нуль-органы 5»-5> блоки 6,-6 задержки сигналов управления, каждый из которых состоит из трех Э-триггеров 6« -б,з, датчик 7 реактивной мащHocTHр блок 8 лОгики усилительнО коммутирующие устройства 9,-96, 10< -10,, 11» -!7e 12„-126 тиристоры

1З-)6, конденсаторные батареи 17-20.

Устройство работает следующим образом.

Первичные обмотки синхронизирующеФ ( го трансформатора 1 подключаются к линейным напряжениям трехфазной питающей сети U !> U>z 11 п (фиг.! ).

С выхода трансформатора 1 фазные напряжения,1*, U!>, U (фиг,4,вых,1) подаются на входы формирователей

1 синхроимпульсав (ФСИ) 2,-2 (фиг,1), на одних выходах которьгл формируются сиихроимпульсы длительностью !80 эл.град., а на других— инверсные !М сиихроимпульсы той же длительностью (фиг.4, вых. ?»-2 ).

С прямого выхода ФСИ 2, синхроимпул!.сы поступают на первые входы логических элементов ЗИ 3 „ и 34., с прямого выхода ФСИ 2 (фиг.4,вых.2 ) синхроимпульсы поступают на первые входы логических элементов ЗИ Зз и

3, а с прямогс выхода ФСН 2З (фиг.4, вых.?>) на первь>е входы логических элементов ЗИ 3 и 3 (фиг.1). С инверсного выхода ФСИ 2 (фиг,4, вых.2 1, синхроимпульсы поступают на вторые входы логических элементов

3Н З и 3» с инверсного выхода ФСИ

2 {фиг,4, вых. 2 ) с!п»хроимпульсы поступают иа вторые входы логических элементов ЗИ 34. и 3> а с инверсного выхода ФСИ 2 (фиг.4, вых.29) на вторые входы логических элементов

ЭИ З„и 3 (дл»г,1). На третьи входы шести логических элементов ЗИ 3» -З поступают импульсы с генератора 4 импульсов (фиг. 4, выл.4 ), При такой организации связей ФСИ

2!-2 > и логических элемеитбв ЗИ

3,-36 на выходе последних будут сформированы частотно-заполненные »п>пульсы длительностью 120 эл.град. (фиг,4, вых. 3,-3 ), причем передние фронты выходных импульсов логических элементов 3» и Зе (фиг.4, вых. 3, и 3<) совпадают соответственно с началом положительной и отрицательной полу-, волн фазного напряжения 11, что соответствует точке максимума отрицатель-. ной и положительной полуволн линейного напряжения U» передние фронты вы5 152062 ходных импульсов логических элементов

3 и 3,(фиг.4,вых.З > и 3 )совпадают соответственно с началом положительной и отрицательной полуволн фазного напряжения U<, что соот5 ветствует точке максимума отрицательной и положительной полуволн линейного напряжения U, а передние фронты выходных импульсов логических элемен- !О тов ЗИ 3 и З (фиг.4,вых,З и 36) совпадают соответственно с началом положительной и отрицательной полуволн фазного напряжения U<, что соответствует точке максимума отрицатель- !5 ной и положительной полуволн линейного напряжения Ucp

С выхода логического элемента ЗИ

З. частотно-заполненные импульсы 2О поступают на входы усилительно-коммутируыщих устройств (УКУ) 91, !О,, 11,, 12 с выходов которых импульсы подаются на управляющие электроды тиристоров 13«, 14 «, 15 „и 16„,, включенных в проводящем направлении для положительной полуволны напряжения UА . С выхода логического элемента 3 импульсы поступают на УКУ 9

102, 112 и 12Z с выхода которык 3р они подаются на управляющие электроды тиристоров 13,, 14,, 15, и

l6«, включенных в проводящем направлении для отрицательной полуволны напряжения U<

Аналогично с выхода логического элемента 3 импульсы через УКУ 9 »

10з, 11 и 12 поступают на управляющие электроды тнристоров 13

142,, 152, и 162» а с выхода логи- 4О ческого элемента 3 через УКУ 9

10, 11 и 12+ — на управляющие электроды тиристоров 13, 1422, ) 5 и 16 2, включенных в каждой секции на напРяжение U>c. С выхода логичес- 45 кого элемента 3 - импульсы через УКУ

9, 10, 11z и 12 поступают на управляемые электроды тиристоров 13», 14> 15» и 16 з,, а с выхода логического элемента 3 через УКУ 96, 106, 11 и 12 — на управляющие электроды тиристоров 13,, 14 2, )5 и 1б, включенных в каждой секции на напряжение U<>.

Сигнал с выхода датчика реактивной мощности (ЛРИ) 7, который является управляющим сигHBJIQM устройства, поступает на вход блока логики (БЛ)

8, на выходе которого вырабатывает(7 6 ся четырехразрядный двоичный код, ° пропорциональный величине реактивной мощности нагрузки. Способ формирования этих управляющих сигналов определяется соотношением мощностей секций

КБ компенсатора. Если мощности отдельных секций KR соотносятся между собой как 1 : 1 : 1 : 1, то блок логики представляет собой пороговый элемент, срабатывание которого проис,ходит в момент превышения уставки Rl сигналом, пропорциональным реактивной мощности в питающей сети. При этом на выходе БЛ 8 формируется сигнал логической "1", разрешающий включение секции устройства. Если же соотношение мощностей секции КБ равно 1 : 2 : 4 : 8, БЛ 8 работает по принципу аналого-цифрового преобразователя. При этом сигнал на выходе БЛ 8 описывается выражением

„3 2 (N=a2 +a 2 +a„2+

3 2

+ а 2, где N — цифровой код на выходе БЛ 8; а — коэффициент при разрядах 2, принимающий значения 0 или l.

Логический сигнал с первого выхода БЛ 8 соответствующего младшему разряду поступает на D-входы Dтриггеров 6« -6,> блока 6, задержки сигнала управления, а логические сигналы старших разрядов с второго, третьего и четвертого выходов БЛ 8 поступают соответственно на D-входы D-триггеров 6,-62, 6, -бээ и

6, -6 > блоков 6., бэ и 6 задержки.

Фазные напряжения U>, V > H Uz с трансформатора 1 напряжения поступают соответственно на входы нульорганов (НО) 5<, 5, 5, причем на выходе НО 5(формируются короткие импульсы с периодом следования

180 эл.град., передние фронты которых совпадают с началом частотно-заполненных импульсов с выходов логических элементов БИ 3, и 3 (фиг.4, вых.5,).

На выходе НО 5 формируются короткие импульсы с периодом следования 180 эл.град., передние фронты которых совпадают с началом частотно-заполненных импульсов с выходов логических элементов ЗИ 3 > и 3 (фиг.4, вых,52), а на выходе нО 5 (фиг.4, вых. 5 >) формируются им. 1520627 пульсь< с периодом следов ания

180 эл,град,, передние фронты которого совпадают с началом частотно-заполненных импульсов с выходов логи5 ческнх злементОв ВИ 3 — и 3

С выходя НО 5, короткие импульсы поступа|от на счетные С-входы D-триггеров 6 «, 6 <, 6 -.„и 6<1 с выхода

ПО 5z на С вЂ” входы D — триггеров 6 <, 6zz,lp

6 н О „с выхода НО 5 > — на С-входь< D — триггеров 6<, 6z, 6 E-, н 64.з °

Вы <одные. сиг<налы элементов 6„-6+ задержки являются управляющими сигналамн УЕ(У 9-12 (фиг.1 и 3). При этом выходной сигнал D-триггера 6« осуществляет включение УКУ 9 „ и (фиг,l), управляющих работой тиристоров первой секции 13 « н 13

13д,, вклю"-тенных на напряжение П,, выходной сигнал D-триггера 6< осу- 25 ществляет включение УКУ 9 и 9<-,, управля<ощих работой тиристоров 13 z< H

13, вкл<оченньгх ЕЕа напряжение Uc .

Аналогично Осуществляется управление УКУ других секций с помощью блоков б,, б и 6, задержки с< гналов управления (фиг.l).

Такая Оргапнзация управления УКУ

9-12„ т.е. передача управляющих сигналои с БЛ 8 через блоки 6 -6 за<

35 держки, позволяет искл<очить неоднозначность включения тиристоров управляю..цих коммутацией КБ, Коммутация секций конденсаторных батарей осуществляется следующим Об- 40 разом.

В момент времени t первая секция КБ находится во включенном состоянии, при этом выходной сигнал

ДРМ / 71одцерживаеT БЛ 8 в PGGo÷1 h< 45 состоянии. <а младшем разряде которого имеется логическая "1", а на остальных -- логические 0 (фиг„5, << << вых.8), Логический сигнал с младшего разряда БЛ Я через D-триггер 6« (фиг.5, вых.б „ ),поступающий на управляющие входы УКУ 9< и 9 (фиг.2)„ разрешает прохождение частотно-заполненных импульсов с выхода логических элементов 3 „ и 3 через УКУ 9 < и 9

55 (фиг.5, вых. 9,, и 9, момент t,o) на управляющие электроды тиристоров

13 „< EE 13<, Аналогично логический сигнал младшего разряда БЛ 8 через триггеры 6«и 6 „ (фиг.5,вых.б,> и

6 <з), поступающие на управляющие входы УКУ 9> -9, разрешают прохождение частотно-заполненных импульсов с логических элементов 3>, 3, Зз и 36 через УКУ 9 -9 (фиг.5,вых.9>-96), на управляющие электроды тиристоров первой секции 13z,, 13, 13 < и

i3 . В этом режиме все тиристоры первой секции КБ открыты и конденсаторы 17 подключены к сети (фиг.5, Вых, .Хдь <7 < E У. бс<7 .» и ? сд <7 ) °

В момент временй ti сигнал с выхо-. да ДРИ 7 равен нулю. При этом все разряды БЛ 8 переходят в состояние логического "0" что соответствует команде на отключение первой секции

КБ (фнг.5, вых,8). Логический "0" младшего разряда БЛ 8 поступает на динамические входы D-триггеров 6 „,, 6 <7 и 6 „з блока 6„ задержки. В момент времени t соответствующий максимальному отрицательному значению полуволны линейного напряжения питающей сети IJE

D-триггер 6 « в нулевое состояние (фиг.5, вых,5 и 6 и ). Логический

"0" на выходе триггера 6,< запрещает прохождение частотно-заполненных импульсов с выходов логических элементов 3, и 3 через УКУ 9.< и 9 (фиг.5, вых. 9, и 9 ) на управляющие электроды тиристоров 13„, и 13, при этом фазный ТоК 3 рр <7 ?????????? ???????? (??????.5, ??????, j.?? <7, ), ?? ?????????????????????? 17, (??????.2) ?????????????????????? ???? ????????. ???????????????????? ?? ?????????????? ?????????????? ?? t4. ??????.6 „ 6<?? ) ?????????????????????? ???????????????????????? 17> (фиг.2). При этом в момент отключения конденсаторы 17 остаются заряженньпш до максимального значения линейного напряжения сети (фиг.5, вых U 11cA <7 5 момент 13), Включение секций происходит следующим образом.

В момент времени t c выхода, BJI 8 поступает команда логической

"1" младшего разряда БЛ 8 на включение первой секции КБ (фиг.5, вых.8), причем поступление команды происходит в течение времени, меньшего периода питающего напряжения, следующего за отключением секций КБ в момент <+ » В момент Времени t,б им» пульс с выхода ИО 5,2 переключает

1520627

10 состояние D-триггера 6„ и на его выходе появляется логическая "1" (фиг.5, вых. 6, ).

Этот сигнал поступает на управляющий вход УКУ 9> и 9+ и тем самым разрешает прохождение частотно-заполненных импульсов с логических элементов 3 и 34 через УКУ 9q и 9+ (фиг. 5, вых. 9 и 9+ ) на управляющие электроды тиристоров 13, и 13 .(фиг,2) первой секции КБ. При подаче управляющего импульса в момент времени t 6 на тиристор 13 последний не открывается, для него не выполняются условия включения из-за наличия остаточного напряжения на конденсаторе 17 (фиг.5, вых. ц

TJ ьс (7

В момент времени tz импульс с 20

Н0 5< изменяет состояние D-триггера

6 (фиг.5, вых. 6,„ ), выходной сигнал которого разрешает прохождение частотно-заполненных импульсов с логических элементов 3 и 3 через

УКУ 9 „и 9 (фиг.5, вых. 9, и 9 ) на управляющие электроды тиристоров

13 и и 13,, включенных на линейное напряжение 1J>>, С момента времени tz происходит подключение к сети кон- 30 денсатора 17 (фиг. 5, вых.Тдв 1,).

Аналогично в момент. времени t npo8 исходит подключение к сети конденсатора 17 (фиг.5, вых. Тсд,т момент времени t, когда остаточное напряжение на койденсаторе 17 равно напряжению сети U8c, для тиристора 13, выполнено условие включения и при подаче управляющего импульса с выхода логического элемента ЗИ 3 40 через УКУ 9 > (фиг.5, вых. 9, момент t>) тиристор 13, открывается и в конденсаторе 17 начинает про2 текать ток (фиг.5, вых. Ie „) .

Таким же образом происходит подклю- 45 чение к сети второй, третьей и четвертой секций КБ, при этом разрешающий сигнал па включение секций поступает соответственно с второго, третьего и четвертого выходов старших разрядов БЛ 8.

Управление тиристорами в момент равенства мгновенного напряжения сети и остаточного напряжения на конденсаторных батареях эа счет исполь55 зования в устройстве трех формирователей синхроимпульсов и шести логических элементов ЗИ позволяет добиться улучшения условий коммутации конденсаторньж батарей.

Введение в схему трех нуль-органов и четырех блоков задержки сигналов управления позволяет исключить срабатывание тиристоров при длительности импульсов управления менее

120 эл.град. и добиться их включения в наиболее благоприятные моменты, что повышает точность и надежность регулирования реактивной мощности

Формула изобретения

Устройство для компенсации реактивной мощности, содержащее четыре секции конденсаторных батарей,конденсаторы каждой из которых соединены в треугольник и подключены в узел нагрузки посредством последовательно соединенных с ними встречно-параллельных тиристоров, четыре группы усилительно-коммутирующих устройств, каждая из которых состоит из шести усилительных элементов, трехфазный синхронизирующий трансформатор,датчик реактивной мощности, блок логики, генератор высокочастотных импульсов, о т л и ч а ю щ е е с я тем, что, с целью улучшения условий коммутации конденсаторов путем включения тиристоров в момент равенства мгновенного напряжения сети и остаточного напряжения на конденсаторах, повышения надежности и точности, в устройство дополнительно введены три формирователя синхроимпульсов,шесть логических элементов ЗИ, три нуль-органа, четыре блока задержки сигнала управления, каждый из которых состоит из трех D-триггеров, при этом первичные обмотки трехфазного синхронизирующего трансформатора подключены к выводам для подключения к трехфазной питающей сети, к вторичным обмоткам трансформатора подключены формирователи синхроимпульсов, а также нуль-органы, причем входы формирователей сичхроимпульсов и нуль-органов подключены к выводам для подключения к соответствующим фазам сети, прямой выход первого формирователя синхроимпульсов соединен с первыми входами первого и второго логических элементов ЗИ, а его инверсный выход — с вторыми входами третьего и четвертого логических элементов ЗИ, прямой выход второго фор15206?7 мирователя синхроимпульсов соединен с первыми входами четвертого и пятого логических элементов ЗИ, aего инверсный выход - с вторыми входами

5 второго и шестого логических элемен- . тов ЗИ, прямой выход третьего формирователя синхроимпульсов соединен с первыми входами третьего и шестого логических элементов ЗИ, а его инверсный выход — с вторыми входами первого и пятого логических элементов ЗИ, выход генератора высокочастотных импульсов подключен к третьим входам всех шести логических элементов ЗИ, выходы логических элементов

ЗИ соединены с информационными входами соответствующих усилительных элементов каждой группы усилительнокоммутирующих устройств, выходы этих усилительных элементов подключены соответственно к управляющим электродам тиристоров каждой секции конденсаторных батарей, подкгпоченпых к выводам для подключения на соответствующее линейное напряжение, выходы нуль-органов соединены соответственйо со счетными входами D-триггеров каждого блока задержки сигнала управления, выход датчика реактивной мощ- ности соединен с блоком логики„предназначенным для преобразования величины реактивной мощности нагрузки в цифровой код, выходы блока логики соединены соответственно с D-входами Л-триггеров блоков задержкп сигнала управления, выходы D-триггеров каждого блока задержки сигнала управления соединены соответственно с управляющими входами первого и второго усилительных элементов, третьего и четвертого усилительных элементов, пятого и шестого усилительных элементов соответствующей группы усилительно-коммутирующих устройств.

1520627 фиг.Ф

1520627 дих,5

8b9.9»

4 4

Фиаf

Составитель О.Наказная

Техред И, Ходанич

Редактор A.Мотыль

Корректор Т.Палия

Заказ 6767/55 Тираж 608 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д, 4/5

Производственно-издательский комбинат "Патент, г. Ужгород, ул. Гагарина, 101