Оперативное запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к оперативным запоминающим устройствам с самоконтролем, и может быть использовано при создании последних в интегральном исполнении. Целью изобретения является упрощение и повышение быстродействия устройства. Устройство содержит накопитель с разрядными шинами информационного и контрольного разрядов, основные и дополнительные усилители записи информационного и контрольного разрядов, усилители считывания информационного и контрольного разрядов, ключи, блоки восстановления уровня, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй элементы ИЛИ, блок синхронизации, элемент НЕ. Для повышения надежности работы и увеличения выхода годных кристаллов в устройстве используется структурно-временная избыточность, заключающаяся во введении дополнительного контрольного разряда и в разбиении цикла записи на три этапа: запись - контрольное считывание - установка контрольного разряда и перезапись инвертированного бита в случае обращения к дефектной ячейке. Цель изобретения достигается за счет сокращения цикла записи путем использования однокаскадной схемы обработки считанных сигналов и асинхронной цепочки включения усилителей записи, а также введением дополнительных усилителей записи, исключающих необходимость схемного объединения записываемых данных перед входами усилителей записи. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (д1) 4 G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А STOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4309254/24-24 (22) 23.09.87 (46) 15.11.89. Бюл. ¹ 42 (72) Н.Г. Григорьев, И.В. Поляков и С.В. Сушко .(53) 681.327.6(088.8) (56) Авторское свидетельство СССР № 1144153, кл. G 11 С 29/00, 1983.

Патент CTJA № 3768071, кл. 340-146.1, опублик. 1973. (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ (57) Изобретение относится к вычислительной технике, в частности к оперативным запоминающим устройствам с самоконтролем, и.может быть использовано при создании последних в интегральном исполнении. Целью изобретения является упрощение и повышение быстродействия устройства. Устройство содержит накопитель c разрядными шинами информационного и контрольного разрядов, основные и дополнительные усилители записи информационного и контрольного разрядов, усилиИзобретение относится к вычислительной технике, в частности к оперативным запоминающим устройствам с самоконтролем, и может быть использовано при создании последних в интегральном исполнении.

Цель изобретения — упрощение и повышение быстродействия устройства, 2 тели считывания информационного и контрольного разрядов, ключи, блоки восстановления уровня, первый и второй элементы ИСКЛЮЧАЦЦЕЕ ИЛИ, пер вый и второй элементы ИЛИ, блок син.хронизации, элемент НЕ. Для повышения надежности работы и увеличения выхода годных кристаллов в устройстве используется структурно-временная избыточность, заключающаяся во введении дополнительного контрольного разряда и в разбиении цикла записи на три этапа: запись — контрольное считывание — установка контрольного разряда и перезапись инвертированного бита в случае обращения к O дефектной ячейке. Цель .изобретения достигается за счет сокращения цикла записи путем использования однокасканной сиани обработки счнтанньсс сигналов и асинхронной цепочки включения усилителей записи, а также введением дополнительных усилителей записи, исключающих необходимость схемного объединения записываемых данных перед входами усилителей записи. 3 ил.

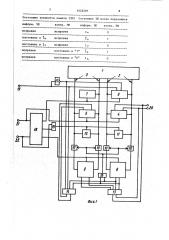

На фиг. 1 представлена структурнологическая схема оперативного запоминающего устройства с самоконтролем, на фиг. 2 — пример реализации блока синхронизации; на фиг. 3 — временные диаграммы работы устройства в режимах записи и считывания, 1522291

Таблица состояний информационного и контрольного элементов памяти до и после операции перезаписи (режим внешней записи).

Устройство содержит накопитель 1, разрядные шины информационного 2 и контрольного 3 разрядов, основные усилители записи информационного 4 и контрольного 5 разрядов, дополнитель- 10 ные усилители записи информационного

6 и контрольного 7 разрядов, усилители считывания информацибнного 8 и контрольного 9 разрядов, ключй 10, блоки восстановления уровня разрядных шин информационного 11 и контрольного 12 разрядов, первый 13 и второй .14 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 15 и второй 16 элементы ИЛИ, эле мент НЕ 17, блок синхронизации 18, информационные вход 19 и парафазный выход 20, вход режима 21 и вход выборки 22 устройства.

Блок синхронизации 18 содержит первый 23 и второй 24 элементы задержки с инверсией, первый 25 и второй 26 элементы ИЛИ-НЕ, первый 27, второй 28, третий 29 .элементы И-НЕ, первый 30 и второй 31- элементы НЕ.

Устройство работает следующим образом.

Йа "временной диаграмме фиг. 4 отображены сигналы на входе 21 ðåжима (Ь), на входе 22 выборки уст- ройства (0) на выходе элемента .

И-НЕ 29 (6), на выходе элемента ИЛИ

15 (2), на выходе элемента И-НЕ 27 (g) и на выходе элемента ИЛИ 16 (e).

На этапе предварительной записи (состояние "0" на входе 21 устрой:ства) разрешена работа дополнительных усилителей записи 6 и 7, на управляющие входы которых с выхода блока синхронизации поступает сигнал низкого уровня (фиг. 4 a ), причем в информационный разряд записывается бит данных с входа 19 устройства, а в контрольный разряд — нулевой бит. При этом. длительность этапа предварительной записи определяется задержкой элемента 23 блока синхронизации 18. Далее в ОЗУ производится восстановление потенциалов . разрядных шин 2 и 3 с помощью бло- . ков 11 и 12, что является обязательной и стандартной процедурой для, например, КИОП ОЗУ, на базе которых предполагается практическая реализация предлагаемого устройства.

Длительность этапа восстановления уровней (фиг. 42) задается элементом задержки 24 блока синхронизации 18 (состояние "1" на его первом выходе).

После этапа восстановления, который имеет также место в перерывах между обращениями к ОЗУ, выполняется считывание ранее записанных данных, их сравнение с истинными значениями и повторная запись должным образом нреобразованных данных. Преобразование считанной информации в предлагаемом устройстве осуществляется с помощью двух элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ 13 и 14, причем элемент 13 используется также и в режиме считывания для возможного инвертирования считанного информационного сигнала.

В таблице приведены примеры результатов преобразования данных для случаев записи в информационный разряд бита данных (напомним, что допускается наличие дефекта только в одном элементе памяти пары, в информационном нли в контрольном).

По завершении преобразования считанных данных устройство переходит в режим повторной записи. Традиционным решением формирования сигнала на перезапись является использование в блоке синхронизации 18 третьего элемента задержки, задающего длительность этапа считывания. Однако в данном ОЗУ переход в режим перезаписи осуществляется автоматически, при срабатывании усилителя считывания 8 информационного разряда. Так, в отсутствие сигнала уровня "1" на управляющих входах усилителей считывания

8 и 9, иа всех их парафазных выходах поддерживаются состояния "0" (это можно наблюдать в стандартных синхронных усилителях считывания на

КИОП-транзисторах), а на парафазных выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

14 и 13 — состояния " 1". Это обеспечивает удержание в закрытом состоянии основных усилителей записи 4 и

5. После срабатывания усилителя считывания 8 на одном из его входов установится сигнал уровня "1", который проходит на выход элемента

ИЛИ 16 и обеспечивает отключение усилителей считывания 8 и 9 от разрядных шин 2 и 3 с помощью ключей

10. Далее, изменение состояния на выходах усилителей считывания 8 и 9 приводит к переключению элементов

5 152229

ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и 14 и, следовательно, к включению усилителей запи.си 4 и 5 на запись вновь сформированных данных (фиг. : e ).

В режиме внешнего считывания цикл работы устройства по сравнению с режимом записи намного короче, поскольку он состоит только из считывания данных усилителями 8 и 9 и инвертиро- 10 вания информационного бита, если контрольный бит равен "1". В режиме считывания сигнал с входа режима 21 устройства запрещает работу основных усилителей записи 4 и 5. Это предотвращает возможность перезаписи истинного значения информацйонного бита, когда элемент памяти контрольного разряда постоянно находится в состоя-.

HHH "1",,т.е. обеспечивает инвертиро- 20 ванне считанной информации.

Формула изобретения.

Оперативное запоминающее устройство с самоконгролем, содержащее накопитель, разрядные шины .нуля и единицы информационно:o H: контрольного разрядов которого соединены с одноименными разрядными выходами основных усилителей записи соответственно ин-.. формационного и контрольного разрядов, усилители считывания информацноиного и контрольного разрядов, первый и второй элементы ИСКЛЮЧАЮЩЕЕ

ИЛИ, первый и второй элементы ИЛИ, элемент НЕ, о т л-и ч а ю щ е е с я тем, что, с целью упрощения и повышения быстродействия устройства, в него введены дополнительные усилите.ли записи информационного и контрольного разрядов, первый и второй блоки восстановления уровня, ключи.по одному на каждую разрядную шину накопителя и блок синхронизации, причем управляющие входы основных усилителей записи информационного и контрольного разрядов являются входом режима устройства и соединены с первым: входом блока синхронизации, второй вход которого является входом выборки устройства и подключен к первому входу первого элемента ИЛИ, вьмод которого соединен с управляющими вхо1 6 дами первого и второго блоков восстановления уровня, разрядные шины нуля и единицы KQTopblx подключены к разрядным шинам нуля и единицы соответственно информаиионного и контрольного разрядов накопителя и. к информационным входам соответствующих ключей, второй вход первого элемента ИЛИ соединен с первым выходом блока синхронизации, второй выход которого подключен к управляющим входам дополнительных усилителей записи информационного и контрольного раз рядов, третий выход блока синхронизации соединен с управляющими входами усилителей считывания информационного и контрольного разрядов, разрядные тины нуля и, единицы которых подключены к выходам соответствующих ключей, парафазные выходы усилителя считывания информационного разряда соединены с парафазнымн входами первой группы первого и второго элементов ИСКЛЮЧАЮЦЕЕ ИЛИ и с входами второго элемента ИЛИ, выход которого подключен к управляющим входам ключей, парафазные выходы усилителя считывания контрольного разряда соединены с парафазными входами второй группы первого элемента ИСКЛЮЧАЮ@ЕЕ ИЛИ, парафаэные выходы которого являются парафазными информационными выходами устройства и подключены к парафазным информационным входам основного усилителя записи информационного разряда, парафазные информационные входы основного усилителя записи контрольного разряда соединены с парафазными выходами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, парафазные входы второй группы которого подключены к парафазным информационным входам дополнительного усилителя записи информационного разряда и соответственно к входу и выходу элемента НЕ, вход которого является информационным входом устройства, разрядные шины нуля и единицы дополнительного усилителя записи информационного разряда соединены с одноименными разрядными шинами накопителя; разрядная шина нуля дополнительного усилителя записи контрольного разряда подключена к одноименной разрядной. шине накопителя.

Состояние элементов памяти (ЭП) Состояние ЭП после перезаписи информ. ЭП контр. ЭП постоянно в In. исправен пОстОЯннО В 1 IÃ3 1 постоянно в "О" 0 информ. ЭП исправен постоянно в Iz,. исправен исправен контр. ЭП исправен исправен

1522291

Т т„

1522291

am /

am22 к8У

Фиг.й

Составитель. О.Исаев

Техред M. Ходанич

Корректор Л.Бескид

Редактор И.Товтин

Заказ 6970/50 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101