Схема сквозного переноса на кмоп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к электронике и вычислительной технике. Цель изобретения - повышение надежности и быстродействия схемы сквозного переноса в сумматорах и арифметико-логических устройствах. Схема содержит элемент, обеспечивающий генерацию инверсии функции распространения переноса, выполненный на элементе И-НЕ, блок, обеспечивающий генерацию сквозного переноса и включающий инвертор и элемент ИЛИ-И-НЕ, и блок, обеспечивающий генерацию инверсии функции формирования сквозного переноса, реализованные на КМОП-транзисторах. Входами схемы служат прямые или инверсные значения входного переноса и поразрадных функций формирования и распространения переноса. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) (И) 1. я) 4 H 03 К 19/0) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

flPH ГННТ СССР

1 ,(21) 4441483/24-2) (22) 14.06.88 (46) 15.)2.89. Бюл. У 46 (72) )O.Г. Дьяченко и С.Г. Селихов (53) 681.325.67(088.8) (56) Ohta К. et. аll. А.High-Speed

Logic LSI Using Diffusion seltAligned Enhancement Depletion.

MOSIS-IEEE Journal of Solid State

Circuits 1975, р. 318, fig 7.

Дроздов Е.А. и др. Электронные вычислительные машины единой системы.-М.: Машиностроение, )981, с.162, рис.4.41. (54) СХЕМА СКВОЗНОГО ПЕРЕНОСА НА

КМОП-ТРАНЗИСТОРАХ (57) Изобретение относится к электронике и вычислительной технике. Пель

Изобретение относится к вычислительной технике и электронике и может использоваться при построении многоразрядных сумматоров и арифметико-логических устройств в составе КЛОП БИС.

Цель изобретения — повышение надежности и быстродействия схемы сквозного переноса.

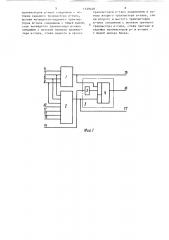

На фиг. 1 изображена схема сквозного переноса, на фиг. 2 — схема первого блока на КМОП-транзисторах.

Схема сквозного переноса содержит элемент И-НЕ ) и функциональные блоки 2 и 3. Блок 3 реализован на элементе ИЛИ-И-1!Е 4 и инверторе 5.

На фиг. ) показаны также входные 614 и выходные 15-)7 шины. Входы

2 изобретения — повышение надежности и быстродействия схемы сквозного переноса в сумматорах и арифметикологических устройствах. Схема содержит элемент, обеспечивающий генерацию инверсии функции распространения переноса, выполненный на элементе И-НЕ, блок, обеспечивающий генерацию сквозного переноса и включающий инвертор и элемент ИЛИИ-НЕ, и блок, обеспечивающий генерацию инверсии функции формирования сквозного переноса, реализованные на КМОП-транзисторах. Входами схемы служат прямые или инверсные значения входного переноса и пораэряд — ф рядных функций фочмирования и распространения переноса. 2 ил. элемента И-НЕ ) подключены к входным шинам 6-9, а его выход — к первой шине 15 схемы и первому входу первой группы выходов по ИЛИ элемента ИЛИ-И-НЕ 4. С первого по седьмой входы первого блока 2 соединены с входными шинами схемы 7-)3, а его выход — с третьей выходной шиной 17 схемы и входом второй группы входов по KIH элемента ИЛИ-И-НЕ 4. Вход инвертора 5 подключен к входной шине )4 схемы, а его выход — к второму входу первой группы входов по ИЛИ элемента ИЛИ-И-НЕ, выход которого подключен к второй выходной шине 16 схемы.

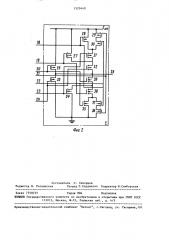

Первый блок содержит семь входных шин 18-24, выходную шину 25, семь

МОП-транзисторов 26-32 р-типа и семь

1529440

15

f + f г4 + з 4

QP, +G

25

35

55 трлн игторов 33-39 п-типа, причем . атноры тран<исторов 26 и 39 27 и

38, 29 и 36, 30 и 35, 31 и 34, 32 и 33 п парно подклн" ень! к шинам 20, 19, 18, 21, 22, ?3 и 24 соответственно,истоки транзисторов 26-29 coepvиены с шиной питания 1 „„, сток тран 3Hcтора 29 подключен к исток) транзистора 30, стоки транзисторов 28 и

30 соединены с истоком транзистора 31, стоки транзисторов 27 и 31 — с истоком транзистора 32, истоки транзисторов 33 — 36 и-типа подключены к шине земли (общей), сток транзистора 36 соединен с истоком транзистора 37, стоки транзисторов 37 и 35 подклн чены к истоку транзистора 38,стоки транзисторов 34 и 38 подключены к истоку транзистора 39, стоки транзисторов

26 и 32 р-типа и транзисторов 33-39 и-типа подключены к выходной шине 25.

Схема работает следующим образом.

При подаче на первые четыре входа схемы 6-9 инверсий f — f функций

4 формирования поразрядного переноса, а на входы, с пятого по восьмой (1013), — инверсий r, — r функций распространения поразрядного переноса с первого по четвертый разряды АЛУ или сумматора, на девятый вход 14 инверсии входного переноса Р,, на первом 15, втором 16 и третьем 17 выходах схемы реализуются функции, реализуемые прототипом, — инверсии функции распространения инверсии

< сквозного переноса 8, инверсии

1 сквозного выходного переноса Р и инверсии функции формирования инверf сии сквозного переноса F соответ1 ственно. Функции описываются следующими формулами т з °

P" =RP + F. о

F =r< + r>f< + r fzfq + r f,f, f4

Частичные функции фомпрования 1 и распространения r — r пораз(1 рядпого переноса описываются формулами (для сумматоров) = А,В,, r = А;+ В, (i = 1-4), где А ., В; — 1 — e разряды обрабатываемых операндов А и В.

При подаче на первые четыре входа схемы прямых значений частичных функций распространения переноса г, — r а на входы, с пятого по восьмой, прямых значений частичных функций формирования поразрядного переноса на девятый вход — прямого значения входного переноса Р, на первом выходе схемьr реализуется инверсия функции распространения прямого значения сквозного переноса 0 на

1 втором выходе — прямое значение

f сквозного переноса Р, а на третьем — инверсия функции формирования прямого значения сквозного переноса

G . .Эти функции описываются формулами:

3 1

1 f r

Формул а изобретения

Схема сквозного переноса на KNOIIтранзисторах, содсржащая два блока и элемент И-НЕ, входы которого подключены к первым четырем входам схемы, а выход — к первой шине выхода схемы, входы первого блока подключены к входам схемы с второго по восьмой, а выход его — к третьей шине выхода схемы, выход второго блока соединен с второй шиной выхода схемы, о тл и ч а ю щ а я с я тем, что, с целью повышения надежности и быстродействия схемы, второй блок включает в себя элемент ИЛИ-И-НЕ и инвертор, первые входы первой и второй групп входов по ИЛИ элемента ИЛИ-И-НЕ подключены соответственно к первой и третьей выходным шинам схемы, вход инвертора соединен с девятой входной шиной схемы, а его выход — с вторым входом первой группы входов по

ИЛИ элемента ИЛИ-И-НЕ, выход которого является выходом второго блока, а первый блок содержит семь POP-транзисторов р-типа проводимости и семь

NOII-транзисторов п-типа, затворы первых-седьмых транзисторов р- и птипа подключены соответственно к одноименным входным шинам блока, истоки первого-четвертого транзисторов р-типа подключены к шине питания, сток четвертого и исток пятого транзисторов р-типа объединены, стоки первого и пятого транзисторов р-типа подключены к истоку шестого транзистора р-типа, стоки второго и шестого

15 транзисторов р-типа соединены с истоком седьмого транзистора р-типа, истоки четвертого-седьмого транзисторов и-типа соединены с общей шиной, сток четвертого транзистора и-типа соединен с истоком первого транзистора п-типа, стоки первого и пятого

6 транзисторов и-типа подклкчены к истоку второго транзистора п-типа, сто. ки второго и шестого транзисторов и-типа соединены с истоком третьего

5 транзистора п-тина, стоки третьих и седьмых транзисторов р- и и-типа с шиной выхода блока.

Составитель О. Скворцов

Редактор Л. Пчолинская Техред Л.Сердюкова Корректор М.Самборская

Заказ 7759/55 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул . Гагарина, 101