Устройство для сопряжения аналого-цифрового преобразователя с микропроцессором

Иллюстрации

Показать всеРеферат

Изобретение относится к электронной технике и может быть использовано для сопряжения первичных преобразователей информации, например аналого-цифровых, с микропроцессором. Цель изобретения - повышение быстродействия устройства за счет автоматического перехода устройства сопряжения в исходное состояние непосредственно после считывания признака завершения очередного цикла работы преобразователя и формирования сигнала готовности. Устройство содержит два триггера, элемент И, буферный регистр, селектор адреса, буферный усилитель. 2 ил.

4, ЬФ б - .ВМЪВ Я% МЪ -.: и 4 ВЮ

Всесоюзная

1li H ;,, нQ-тQ 1; )нu окя, я 1с Д

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 06 F 3 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ П НТ СССР (21),4427240/24-24 (22) 17.05.88 (46) 23.02.90. Бюл, И - 7 (72) М,А.Гуранчик, А,В.Рывкин, В.Л.Черняк и Ф.Ф.Братский (53) 681.3 (088.8) (56) Кофрон Дж. и,Понг В. Расширение микропроцессорных систем.

М.: Машиностроение, 1987, с. 194.

Ломтев Е.А. и др. Сопряжение преобразователей формы информации с микропроцессорными средствами.

Изд, †.во Саратовского университета, 1986, с. 131-133. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ

С МИКРОПРОЦЕССОРОМ

Изобретение относится к электронной технике и может бить использовано для сопряжения первичных преобразователей информации, например аналого-цифрового преобразователя (АЦП), с микропроцессором., Целью изобретения является повышение быстродействия устройства за счет оптимизации процесса асинхронного обмена и автоматического перехода устройства сопряжения в исходное состояние непосредственно после считывания признака завершения очередного цикла работы преобразователя.

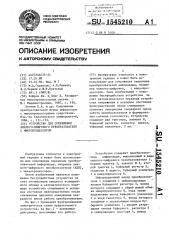

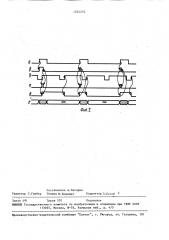

На фиг,1 приведена функциональная электрическая схема предлагаемого устройства; на фиг,2 — временные диаграммы, поясняющие его работу.

1545210 А 1 (57) Изобретение относится к элек" тронной технике и может быть исI пользовано для сопряжения первичных

:преобразователей информации, например аналого-цифровых, с микропроцессором. Цель изобретения — повышение быстродействия устройства за счет автоматического перехода устройства сопряжения в исходное состояние непосредственно после считывания признака завершения очередного цикла работы преобразователя и формирования сигнала готовности, Устройство содержит два триггера, элемент И, буферный регистр, селектор адреса, буферный усилитель, 2 ил.

Устройство содержит преобразова тель информации, выполненный в. виде аналого-цифрового преобразователя 1, первый триггер 2, элемент И 3, второй триггер 4, буферный регистр 5, селектор 6 адреса, буферный усилитель

7 и микропроцессор 6.

Информационный выход преобразователя .1 соединен с информационным входом буферного регистра 5, выход которого соединен с общей шиной обмена микропроцессора 8, куда также подключены выход буферного усилителя

7 и вход селектора 6, выход которого соединен с управляющим входом буферного усилителя 7, входом разре" шения чтения буферного регистра 5 и синхровходом триггера 4, выход

15452 которого соединен с информационным входом буферного усилителя /, входом разрешения записи буферного регистра 5, вторым входом элемента И 3 и

Й-входом триггера 2, синхровход ко5 торого подключен к выходу синхронизации преобразователя 1, а выход соединен с первым входом элемента И 3, выход которого соединен с S-входом

10 триггера 4, на D-вход триггера 2 подан уровень логической 1, на

D-вход триггера 4 — уровень логического "0", Преобразователь 1 может являться, например, аналого-цифровым преобразователем, имеющим информационный выход и выход сигнала готовности, являющийся вторым выходом преобразователя I. В качестве преобразователя

1 может использоваться, например, микросхема К1113ПВI, включенная в режиме автономного периодического запуска, Буферный регистр 5 обеспечивает фиксацию выходного состояния преобразователя 1 по окончании каждого цикла аналого-цифрового преобразования, а также подключение его к общей шине обмена микропроцессора 8.

Б качестве буферного регистра 5 в предлагаемом устройстве может быть использована микросхема К588ИР1, имеющая управляющие входы записи и чтения, а также при отсутствии сигнала чтения — третье состояние выходных шин (состояние высокого импеданса), Г>уферный усилитель 7 служит для подключения выхода триггера 4 к

40 общей шине микропроцессора 8 (при наличии на управляющем входе усилителя 7 сигнала чтения от селекторов сигналов) и может быть выполнен, например, на основе микросхемы

К561ЛН1, имеющей третье состояние

45 выхода (состояние высокого импеданса) .

Селектор 6 служит для выработки сигнала чтения (при обращении микропроцессора 8 к предопределенному адресу, соответствующему выбранному для чтения первичному преобразователю информации), по которому буферный регистр 5 и буферный усилитель

7 выходят из третьего состояния, подавая на интерфейсные шины (>данных ) 55 соответствующую информацию, которая затем считывается микропроцессором 8.

Практическая реализация селектора 6

1О а зависит от типа микропроцессора 8 и может быть выполнена по любой из известных схем, так, например для микропроцессора К1801БМ2 может быть выполнен на основе микросхем детифратора адреса К588ВТ1 и элемента ИЛИНЕ микросхемы 1 561ЛЕ5. При этом элемент ИЛИ-НЕ при наличии на его вы- . ходах сигналов 1>1: и Д 1Т с соответствующих выходов микросхемы К5888БТI вырабатывает выходной сигнал .селектора 5. Г>озможны и другие варианты технической реализации селектора 6 формирования управляющих сигналов.

- Микропроцессор 8 может иметь, например, встроенные или внешние оперативно-запоминающие и постоянно-запоминающие блоки памяти (03Y и ПЗУ), включенные по тиновой схеме. В ПЗУ хранится программа работы микропро-О цессора, а ОЗУ является буфером для хранения всех промежуточных результатов и операций, б

Устройство работает следующим образом.

При работе преобразователя 1 на его выходе синхронизации периодически вырабатываются сигналы, свидетельствующие об окончании"процесса преобразования входной информации (фиг.2, q ), по которым взводится триггер 2 (фиг, 2, б).

Микропроцессор 8 постоянно осуществляет чтение состояния триггера

4 (посредством буферного усилителя 7) и буферного регистра 5. При этом селектор 5 периодически вырабатывает сигнал чтения, посредством которого производится подключение буферного регистра 5 к общей шине обмена микропроцессора 8 (фиг,2, ь).

Ввиду того, что опрос микропроцессором 8 выходного состояния триггера

4 и буферного регистра 5 несинхронизирован с моментами окончания работы преобразователя 1 (готовности преобразуемой информации к передаче в микропроцессор 8) возможны несколько различных вариантов работы устройства, что схематически показано на фиг.2, Если триггер 2 взводится во время формирования сигнала чтения на .выходе селектора 6, то последний. посредством элемента И 3 блокирует . срабатывание триггера 4, что исключает передачу в микропроцессор 8 ошибочной информации, которая может

5 15452 произойти из-эа переходных процессов, связанных с перезаписью информации с первого ekxoga преобразователя 1 в буферный регистр 5. Триггер 4 взводится непосредственно после исчез5 новения на выходе селектора 6 присутствующего там сигнала чтения, а передача в микропроцессор 8 выходной информации от преобразователя 1 в данном случае производится при выработке селектором 6 следующего сигнала чтения, При срабатывании триггера 4 триггер 2 сбрасывается сразу, а триггер 4 сбрасывается по окончании сигнала чтения с выхода селектора 6 (фиг. 2, ) .

Если триггер 2 взводится в промежутках между сигналами чтения, формируемых на выходе селектора .6, то 20 выходной сигнал триггера 2 .непосредственно вводит триггер 4, выходной сигнал которого, в свою очередь, сбрасывает триггер 2. Триггер 4 сбрасывается при этом по окончании оче- 25 редкого сигнала чтения с выхода селектора 6.

Формула изобретения

Устройство для сопряжения аналого- ЗО цифрового преобразователя с микропроцессором, содержащее селектор адреса, буферный регистр, информационный вход которого является входом устройства для подключения к информационному выходу аналого-цифрового преобраэова10 6 теля, а выход является выходом уст ройства для подключения к шине данных микропроцессора, информационный вход селектора адреса является входом устройства для подключения к шине управления микропроцессора, выход селектора адреса соединен с входом разрешения чтения буферного регистра, о т л и ч а ю щ е е с я тем, что, с целью. повышения быстродействия устройства, в него введены элемент И, первый и второй триггеры и буферный усилитель, выход которого подключен к выходу устройства для подключения к шйне данных микропроцессора, синхровход первого триггера является входом устройства для подключения к выходу готовности аналого-цифрового преобразователя, выход первого триггера соединен с первым входом элеI мента И, выход которого соединен с установочным входом второго триггера выход которого соединен с входом сброса первого триггера, входом раз" решения записи буферного регистра и информационным входом буферного усилителя, управляющий вход которого подключен к выходу селектора адреса, второму входу элемента И и к синхро входу второго триггера, информационный вход первого триггера подключен к шине единичного потенциала устройства, а информационный вход второго триггера — к шине нулевого потенциала устройства.

Рие 7

Составитель А.Засорин

Редактор Г.Гербер Техред И.Ходанич Корректор Л,Патай

Заказ 491 Тираж 570 Подписное

ВНКИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская.наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101