Устройство для вычитания

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах ЦВМ с повышенной достоверностью обработки данных. Целью изобретения является увеличение быстродействия. Это достигается тем, что устройство для вычитания содержит два регистра 6 и 7 чисел, два блока элементов И 8 и 9, элементы И 10 и 11, блок 12 элементов ИЛИ, триггеры 13 и 14, блоки 15 и 16 постоянной памяти, регистры 17 и 18 переносов, элементы ИЛИ 19 и 20 с соответствующими связями. 1 ил., 1 табл.

СОЮЗ СОВЕТСКИХ сОциАлистичесних

PECflVSllHH (!9! (В (51)5 С 06 F

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ пО изОБРетениям и ОтнРытиям

ПРИ ГКНТ СССР (21) 4468872/24-24 (22) 01.08,88 (46) 15.05.90. Бюл. N - 18 (72) В.В. Роздобара, Г.В. Кремез и Ю.И. Прохоров (53) 681.325,5 (088.8) (56) Авторское свидетельство СССР

В 141 1734, кл. С 06 F 7/49, 1987.

Авторское свидетельство СССР М 1259249, кл. G 06 F 7/40, 1985. (54) УСТРОЙСТВО ДЛЯ ВЬИИТАНИЯ (57) Изобретение относится к цифровой

2 вычислительной технике и может быть использовано в процессорах ЦВИ " повьппенной достоверностью обработки данных. Целью изобретения является увеличение быстродействия,. Это достигается тем, что устройство для вычитания содержит два регистра 6 и 7 чисел, два блока элементов И 8 и 9, элементы И 10 и 11, блок 12 элементов ИЛИ, триггеры 13 и 14, блоки 15 и 16 постоянной памяти, регистры 17 и 18 переносов, элементы ИЛИ 19 и

20 с соответствующими связями. 1 ил., 1 табл.

15646 l 2

Изобретение относится к вычисли( тельной технике, предназначено для вычитания многоразрядных кодов золотой пропорции и может быть исполь5 зовано в процессорах ЦВИ с повышенной достоверностью обработки данных.

Цель изобретения — повышение быстродействия.

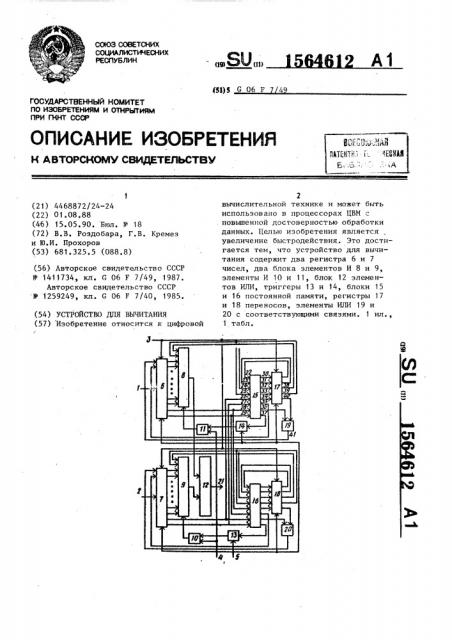

Ча чертеже представлена схема уст- 10 ойства для вычитания.

Устройство содержит вход 1 умень1 аемого устройства, вход 2 вычитае мого устройства, первый и второй так( новые входы 3 и 4 устройства, вход

5 начальной установки устройства, 1 первый и второй регистры 6 и 7 чисел„ первый и второй блоки 8 и 9 элемен г ов И, второй и первый элементы И 10

11, блок 12 элементов ИЛИ, второй 20 первый триггеры 13 и 14, первый второй блоки 15 и 16 постоянной амяти, первый и второй регистры 17

18 переносов, первый и второй эле2 енты ИЛИ 19 и 20, выход 21 устройст- 25 а, входы 22-25 разрядов с третьего цо шестой адресного входа блока 15 постоянной памяти, входы 26-29 разрядов восьмого, второго, седьмого и

Первого адресного входа блока 15 пос- 30 тоянной памяти, выходы 30-37 разрядов с первого по восьмой блока 15 постоянной памяти, выходы 38-40 разрядов с третьего по пятый первого регистра

17 переносов и выход 41 элемента

ИЛИ 19.

Первый и второй триггеры служат для выбора рабочей половины устройства и фиксирования ошибок во время выполнения операции устройством.

Первыи и второй блоки 15 и 16 постоянной памяти предназначены для хранения таблицы.

Первый и второй регистры 17 и 18 переносов обеспечивают запись и выдачу переносов для следующего такта и запоминание значения младшего из двух формируемых разрядов в каждом такте.

Первый и второй элементы ИЛИ 19 и 20 предназначены для формирования значения младшего разряда разности каждого такта.

Первый и второй регистры 6 и 7 чисел служат для хранения операндов и их сдвига на два разряда в сторону старших разрядов.

Устройство работает следующим образом.

Рассмотрим случай вычитания прямых и-разрядных золотых 1-кодов, где и кратно двум.

Для выполнения вычитания на входы

1 и 2 устройства подаются прямые золотые 1-коды соответственно уменьшаемого и вычитаемого. На вход 5 устройства поступает сигнал, который устанавливает в "1" триггеры 13 и 14, обнуляет регистры t7 и 18 переносов, разрешает запись кодов чисел с входов 1 и 2 соответственно на первый и второй регистры 6 и 7 чисел. По два старших разряда записанных чисел поступают на четыре входа каждого блока постоянной. памяти.

На входы первого блока постоянной памяти поступает следующая информация: вход 29 = n-й разряд уменьшаемого; вход 28 = (n-1)-й разряд уменьшаемого; вход 27 = n-й разряд вычитаемого; вход 26 = (n-1)-й разряд вычитаемого.

На аналогичные входы второго блока постоянной памяти поступают те же разряды, но вычитаемое и уменьшаемое меняются местами, Входы 22-25 = значения четырех разрядов регистров переносов, которые в первом такте равны нулю.

На выходах блоков постоянной памяти образуется. информация, соответствующая входным сигналам согласно таблице.

Если значение разрядов уменьшаемого больше значений разрядов вычитаемого, то на выходе 37 первого блока

15 постоянной памяти присутствует "0", а на аналогичном выходе второго блока 16 постоянной памяти — "1", которая устанавливает триггер 13 в "0".

Это свидетельствует о том, что знак разности положительный, и вычитание производится первым блоком 15 постоянной памяти. Если вычитаемое больше уменьшаемого, то на выходе 37 первого блока 15 постоянной памяти присутствует "1", которая устанавливает триггер 14 в "0". Это свидетельствует о том, что знак разности отрицательный, и вычитание производится вторым блоком 16 постоянной памяти.

Если значения разрядов уменьшаемого и вычитаемого равны, то и на выходе

37 первого блока 15 постоянной памяти и на аналогичном выходе второго бло5

15 ка 16 постоянной памяти присутствует "0". " 1" на одном из этих выходов появляется в том такте, в котором . значения выбранных разрядов уменьшаемого и вычитаемого различны, на другом выходе после этого всегда присутствует "О" независимо от значений поступающих разрядов, за исключением случаев нарушения работоспособности устройства.

Рассмотрим случай, когда уменьшае-. мое больше вычитаемого, т.е. значения двух его старших разрядов больше значения двух старших разрядов вычитаемого. На выходах первого блока 15 постоянной памяти образуется информация соответствующая таблице, триггер 13 устанавливается в "0" (в соответствии с описанным). Подается сигнал на вход 3 устройства, по которому осуществляется сдвиг на два разряда в регистрах чисел и запись в два младших разряда регистра 6 значений с выходов 35 и 41, запись на регистр

17 переносов значений с выходов 30-3 первого блока 15 постоянной памяти.

На этом первый такт вычитания закончен.

В кажцом последующем такте на входы первого блока 15 постоянной памяти поступает новая информация и подается сигнал на вход 3 устройства. Таких тактов будет и/2. После этого

1 подается сигнал на вход 4 устройства. На выходе элемента И 10 присутствует "0", а на выходе элемента И 11 появляется "1", которая открывает блок 8 элементов И, и формируется результат вычитания:

1-й, 2-й разряды = значения выходов 39 и 38 регистра 17 переносов;

3-й — n-й разряды = 1-й — (и-2)-й разряды регистра 6 чисел.

Этот результат через блок 12 элементов ИЛИ поступает на выход 21 устройства.

64612

Устройство для вычитания, содержащее первый и второй регистры чисел, первый блок постоянной памяти и первый регистр переносов, причем входы уменьшаемого и вычитаемого устройства соединены соответственно с информационными входами первого и второго регистров чисел, входы разрешения сдвига которых соединены с входом;

Формула из обретения разрешения записи первого регистра переносов и с первым тактовым входом устройства, выходы п-х (n — разрядность чисел) разрядов первого и второго регистров чисел соединены соответственно с входами первого и второго разрядов адресного входа первого блока постоянной памяти, выходы с первого по четвертый разрядов которого соединены с входами соответствующих разрядов первого регистра переносов, выходы с первого по четвертый разрядов которого соединены соответственно с входами с третьего по шестой разрядов адресного входа первого блока постоянной памяти, вход начальной установки устройства соединен с входом установки в "0" первого регистра переносов и с входами разрешения записи первого и второго регистров чисел, о т л и ч а— ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит второй блок постоянной памяти, второй регистр переносов, первый и второй блоки элементов И, блок элементов ИЛИ, первый и второй элементы И, первый и второй триггеры. первый и второй элементы ИЛИ, причем вход начальной установки устройства соединен с входами установки в "1" первого и второго триггеров, с входом установки в 0 второго регистра переносов, первый тактовый вход устройства соединен с входом разрешения записи второго регистра переносов, выходы и-х разрядов второго и первого регистров чисел соединены соответственно с входами первого и второго разрядов адресного Входа второго блока постоянной памяти, выходы с; первого по четвертый разрядов которого соединены с входами соответствующих разрядов второго регистра пе-. реносов, выходы с первого по четвертый разрядов- которого соединены соответственно с входами с третьего по шестой разрядов адресного входа второго блока постоянной памяти, выходы (n-1)-х разрядов первого и второго регистров чисел соединены соответственно с входами седьмого и восьмого разрядов адресного входа первого блока постоянной памяти, выход пятого разряда которогo соединен с входом соответствующего разряда первого регистра переносов, выход шестого разряда первого блока постоянной памяти

1564612 переносов, выход шестого разряда второго блока постоянной памяти и выход второго элемента ИЛИ соединены соответственно с входами двух младших разрядов второго регистра чисел, выходы разрядов, кроме двух старших, которого и выходы третьего и четвертого разрядов второго регистра переносов соединены соответственно с входами разрядов первого входа второго блока элементов И, выход которого соединен с вторым входом блока элементов ИЛИ, выходы седьмого и восьмого разрядов второго блока постоянной памяти соединены соответственно с первым входом второго элемента ИЛИ и с входом установки в "О" второго .. триггера, выход которого соединен с первым входом второго элемента И, выход которого соединен с вторым входом второго блока элементов И, выходы пятых разрядов первого и второго регистров переносов соединены соответственно с вторыми входами первого и второго элементов ИЛИ, второй тактовый вход устройства соединен с вторыми входами первого и второго элементов И. и выход первого элемента HJIH соединены соответственно с входами двух младших разрядов первого регистра чисел, выходы разрядов, кроме двух старших, которого и выходы третье5 го и четвертого разрядов первого регистра переносов соединены соответственно с входами разрядов первого входа первого блока элементов И, выход которого соединен с первым входом блока элементов HJIH выход кото рого является выходом устройства, выМоды седьмого, восьмого разрядов пер вого блока постоянной памяти соедине- I> ны соответственно с первым входом, первого элемента ИЛИ и с входом уста новки в "О" первого триггера, выход которого соединен с первым входом первого элемента И, выход которого соединен с вторым входом первого блоа элементов И, выходы (и-1)-х разяпов второго и первого регистров чисел соединены соответстенно с вхо- ! рами седьмого и восьмого разрядов 25 адресного входа второго блока постоянной памяти, выход пятого разряда которого соединен с входом соответствующего разряда второго регистра .

Г Г (Г Т Т Т1

33 32 31 30

25 24 23 22 29 28 27 26

О О О О О О

О 1

1 О

1 1

0 О О 1 О О

О 1

1 О

О О 1 О О О

О

О

0

0

О

О

О

1

О

О

1

О

1

О

О

О

О

О t

О

О

О

0

О

О

1

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

36 35 34

0 О О

О О О

О О О

О О О

О О О

О О О

О О О

О О О

0 О О

О О 0

О О О

О О О

О О О

О 0 О

О О О

0 О О

О О О

О 0 О

О О О

О О 1

О О О

О О О

О О О

О О О

О О О

О О О

О

О 1

О О

1 О

О О

О О

1 1

1 О

О 1

О О

О 1

0,0

1 О

О

О О

1 1

О

О 1

О О

О 1

1 1

О

О 1

1 О

О О

О О

О О

О О

О О

О О

1 О

О О

О О

О О

О О

О О

О О

О О

О 1

О О

0 1

О О

О О

О О

О О

О О

О О

О 1

О О

О, О

1 О

О 0

1564612

Продолжение таблицы, Выходы ПЗУ

1 1

33 32

35 34

26

27

О 1

О

1 0

1 1

1 О

О. О

1 О

1 1

О

О О

О

О

1

1

О 1

0 . 1

1 О

1 1

1 О

О 1

Входы ПЗУ

Гт lt t

25 24 23 22 29 28

О 1 О О О О

О 1 О 1 О О

1 О О О О О

О

О

1

О

О

1

О

1 .1

О

1

О

О

1

О

1

0

1

0

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

1

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

1

0

О

О

О

О

О

1

О

О

1

1

О

О

О

О

1

1

О

О

1

1

1

1

1

О

О

О

1

О

1

1

О

О

1

1

О

1

1

1

1

О

О

1

1

О

1

О

О

О

1

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

l2

1564612

Продолжение таблицы

Выходы ПЗУ

Т Т

ГТГГ|ГГ

34 33 32 31 30

25 24 23 22 29 28 27

36 35

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О 1

1 1

О -1

О 1

О 1

О 1

О

О

О

О

О

О

О

О

О 1

1 О

1 1

1

О О О О

О

0

О

О 1

1 1

О

1 0

1 О О 1 0 0

1 О О 1 1 0

1 0 1 О О О

О

О

1

О

О

1

0

1

О

1

О

О

1

О

О

О

О

0

О

1

О

О

1

О

О

1

О.

О

1

О

О

О

О

О

О

О

О

О

О

0

О

О

О

О

О

О

О

О l

О

О

О

О

О

О

О

О

О

0

О

О

О

О

О

О

О

О

О

О

О

О

О

О о

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

1

О

О

О

О

О

1

О

О

О

1

О

О

О

О

О

О

1

О

О

О

О

О

О

О

О

О

О

О

1

1

О

О

0

О

1

О

О

1

О

О

1

О

1

1

1

О

1

1

О

4

1

О

О

1

1

О

1

О

О

1

О

О

О

О

1

О

О

О

О

13.

1564612

Продолжение таблицы

Входы ПЗУ Выходы ПЗУ

27 26 37 33 32

25 24 23 22 29 28

31 30

1 1 1 О О 0

1 О

1 1

Составитель А. Клюев

Техред М.Дидык

Редактор А. Orap

Корректор Н. Король

Заказ 11.60

Тираж 560

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãoðoä, ул. Гагарина,101

0 О О

0 1 О

1 О О

1 1 О

О О О

О 1 О

1 0 0

1 О

0 О О

О I О

1 Q О

1 1 О

О О О

О 1 О

1 О О

1 1 О

О О О

0 .1 О

1 О О

1 1 О

36 35 34

l О О

1 О 0

О О

О 1 0

1 О О

О 1 О

О 1 О

О 1 О

1 О О.О . О

1 О О

О 1 О

1 О О

1 О О

1 О О

О 1 О

1 О 1

1 О О

1 .О О

1 0 О

I 1

1 0

О 1

1 1

1 О

1 1

1 1

1 О

1 1

1 О

О 1

1 1

1 1

1 О

1 О

1 О

1 1

1 1

1 О

О О

О 0;

О О

О 0

0 О

1 О

О О

О 0

О О

О О

О О

О О

1 О

1 О

О О

1 О

О О

1 О

О О

О О