Оптоэлектронный элемент матрицы для выделения контура изображения

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам для обработки изображений. Цель изобретения - расширение функциональных возможностей за счет выполнения логических операций с двумя изображениями. Поставленная цель достигается введением блока формирования логических функций и блока инвертирования оптического сигнала. Оптоэлектронный элемент матрицы для выделения контура изображения работает в четырех режимах: - режим выделения контура режим выполнения операции дизъюнкции режим выполнения операции конъюнкции режим выполнения операции сложения по модулю два. Выбор режима осуществляется комбинацией сигналов на шинах управления и на пятом входе элемента ИЛИ. 1 ил.

СОЮЗ СОВЕТСКИХ социАлистических

РЕСПУБЛИК

А2

„„SU„„ l58 948 () С 06 К 9 .36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ по изОБРетениям и очнРытиям пРи Гннт сссР (61) 1439637 (21) 4434293/24-24 (22) 01.06,88 (46) 07. 08. 90. Бюл. № 29 (71) Грузинский политехнический институт им. В.И. Ленина и Винницкий политехнический институт (72) В.П. Кожемяко, В.А. Подорожнюк, О.Г. Натрошвили, Л.Ш. Имнаишвили, С.Н. Белан и Е.И. Котлярова (53) 68),327.12(088.8) (56) Авторское свидетельство СССР № 1439637, кл. G 06 К 9/36, 1987. (54) ОПТОЭЛЕКТРОННЫЙ ЭЛЕМЕНТ МАТРИЦЫ

ДЛЯ ВЫДЕЛЕНИЯ КОНТУРА ИЗОБРАЖЕНИЯ (57) Изобретение относится к автоматике и вычислительной технике, а

Изобретение относится к автоматике и вычислительной технике, а именно к оптоэлектронным элементам матрицы для выделения контура изображения, а также к элементам, выполняющим логические операции, и является усовершенствованием изобретения по авт.св.

¹ 1439637.

Цель изобретения — расширение функциональных возможностей путем выполнения логических операций с двумя изображениями.

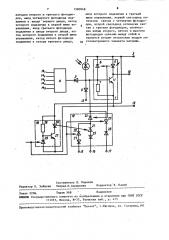

На чертеже представлена функциональная блок-схема устройства.

Оптоэлектронный элемент матрицы для выделения контура изображения содержит запоминающий элемент 1, фо-. топриемный элемент 2, шину 3 питания, 2 йменно к устройствам для обработки изображений. Цель изобретения — расширение функциональных возможностей за счет выполнения логических операций с двумя изображениями. Поставленная цель достигается введением блока формирования. логических функций и блока инвертирования оптического. сигнала. Оптоэлектронный элемент матри" цы для выделения контура изображения работает в четырех режимах. режим выделения контура; режим выполнения операции диэъюнкции; режим выполнения операции конъюнкции; режим выполнения операции сложения по модулю два.

Выбор режима осуществляется комбина- д цией сигналов на шинах управления и на пятом входе элемента ИЛИ. 1 ил. элемент ИЛИ 4, выпрямительные элементы 5 и 6, первый резистор 7, первый фотодиод 8, первый светодиод 9, выходную шину 10, транзистор ll, шину 12 нулевого потенциала, шину 13 установки элемента матрицы в исходное состояние, входы 14 -14, первые четыре иэ которых подключаются к выходам смежных оптоэлектронных элементов, а пятый соединяется с входом выделения контура матрицы, три шины ,1.5-17 управления, блок 18 инвертирования оптического сигнала, блок 19 формирования логических функций, второй — пятый фотодиоды 20-23, три диода 24-26, второй транзистор 27, второй резистор 28, шестой фотодиод 29, второй светодиод 30.

1583948

Оптоэлектронный элемент матрицы для выделения контура изображения может работать в четырех режимах: режим выделения контура иэображения; режим выполнения операции дизъюнкции; режим выполнения операции конъюнкции; режим выполнения операции сложения по модулю два.

Выделение контура бинарного изображения осуществляется путем выделения возбужденного оптоэлектронного элемента матрицы, у которого хотя бы один из четырех соседних (смежных ) элементов является невозбужденным (неосвещенным). В данном режиме на второй оптический вход оптический сигнал не подается, а на шинах 15-17 управления могут присутствовать любые сигналы. — — 20

Если на фотоприемный элемент 2 попадает свет, то от шины 3 питания через него начинает протекать ток.

В результате на, базе транзистора ll запоминающего элемента 1 создается 25 напряжение, отпирающее его 1транзистор 11 открывается ). Светодиод 9, подавая свет на фотодиод 8, включает его, тем самым реализуя положительную обратную связь. Это приводит к тому, что.на базу транзистора ll через фотодиод 8 протекает ток, удерживая транзистор 11 постоянно в режиме смещения. На его коллекторе появляется нулевой сигнал, который по35 дается на выходную шину 10.

Если все смежные с данным оптоэлектронные элементы матрицы возбуж дены (освещены }, то на входах 14—

14 элемента 4 ИЛИ присутствуют d or Hческие "0!! Если на пятом входе 14 !! !! присутствует логическии О, то с !! !! выхода элемента ИЛИ 4 логическии 0 поступает на катод первого выпрями тельного элемента 5, в результате чего шунтируется переход база - эмиттер транзистора 11, и данный элемент матрицы обнуляется. Если элемент матрицы не был возбужден, то остается в том же состоянии. В случае присут50 ствия хотя бы на одном входе 14 „-14 4, !! !! элемента 4 ИЛИ логической 1 изменения состояния оптоэлектронного элемента не происходит. Если на пятом входе 14 элемента 4 ИЛИ присутст5 55 вует логическая 1, то выделение контура не происходит.

Дпя установки оптоэлектронного элемента в начальное состояние на шину 13 подается нулевой потенциал, поступающий на катод второго выпрямительного элемента б, в результате чего транзистор il запирается. Светодиод 9 служит также для внешней индикации результата, а резистор 2 смещения служит для задания напряжения смещения на базе транзистора 11.

В режиме выполнения операции дизьюнкции (логическое сложение) на все три шины 15-17 управления и пятый вход 14< элемента 4 ИЛИ подаются высокие положительные потенциалы, Включение первого и второго диодов 24 и

25 блока 19 формирования логических функций не дает возможности протекания тока в базу транзистора 11 от первой и второй шин 15 и 16 управления

Операция дизъюн!кции производится с сигналом, поступающим на второй оптический вход, и с собственным состоянием запоминающего элемента 1 (сигналом на выходе светодиода 9), а результат получается на выходе запоминающего элемента 1 (состояние светодиода 9). Присутствие оптического сигнала на втором оптическом входе либо на светодиоде 9 соответствует логической 1", а отсутствие — логическому "0". Если присутствует два логических "0"1 то элемент матрицы остается в том же состоянии (логичес-кий "0"). Если на светодиоде 9 присутствует оптический сигнап (s огическая "1"), а на втором оптическом входе логический "0", то элемент остается в состоянии логической "l при этом транзистор 27 блока 18 инвертирования оптического сигнала открыт и первый светодиод 30 этого же блока 18 горит за счет протекания тока от шины 3 питания через резистор 28 в базу транзистора 27.

В случае, если на втором оптическом входе присутствует оптический сигнал, а на светодиоде 9 не присутствует, то запоминающий элемент 1 переходит в состояние логической "1" (светодиод 9 горит) за счет того, что с второго оптическсго входа на пятый фотодиод 23 поступает оптический сигнал, и ток протекает от третьей шины 17 управления через третий диод 26 и пятый фотодиод 23 в базу транзистора 11, отпирая его.

В случае присутствия двух логичес ких "1", элемент матрицы остается в том же состоянии.

158

В режиме выполнения операции конь- юнкции на первую, вторую и третью шины 15-17 управления подаютея соответственно единичный, нулевой и нулевой потенциалы напряжения.

Если присутствует два логических л 11

О, то элемент матрицы остается в состоянии логического "0" .

Если на светодиоде 9 присутствует оптический сигнал, а на втором оптическом входе не присутствует (комбинация IO» то элемент матрицы перехо1 дит в состояние логического "0" так как оптический сигнал от светодиода 9 поступает на фотодиод 22 блока 19, а транзистор 27 блока 18 открыт, и от светодиода 30 свет .поступает на фотодиод 21 блока 19.

Открытые фотодиоды 2l и 22 блока 19 шунтируют переход база — эмиттер транзистора 11, запирая его. Ток будет протекать не в базу транзистора 11, а через фстодиоды 22 и 21 и второй диод 25 к второй шине 16 управления.

В случае, если на втором оптическом входе присутствует оптический сигнал, а на светодиоде 9 не присутствует (комбинация 01), то элемент матрицы остается в состоянии логического "0", а транзистор 27 блока 18 заперт, так как на его фотодиоде 29 присутствует свет, который шунтирует переход база — эмиттер транзистора 27 и запирает его.

Если присутствует комбинация ll, то элемент матрицы остается в состоянии логической "1", так как третий диод 26 включен -,àê, что не допускает протекания тока к третьей шине 17 управления.

В режиме выполнения операции сложения по модулю два на третью и вторую шины 17 и 16 подается высокий положительный потенциал, а на первую шину 15 управления — нулевой потен.— . циал.

Если присутствует комбинация 00, то элемент матрицы остается в состоянии логического "0". Если присутствует комбинация 10, то элемент матрицы остается в состоянии логической !, так как нет при данной комбинации цепи обнуления.

В случае присутствия комбинации

01, на фотодиоде 23 присутствует свет, и ток йротекает от третьей шины 17 угравления через третий диод 26 и фо3948 6 тодиод 23 в багу транзистора IJ отпирая его. Элемент матрицЫ переходит в состояние логической "1".

В случае присутствия комбинации 11, на фотодиодах 20 и 22 блока 19 присутствует свет, который переводит их в проводящее состояние. Через них и первый диод 24 протекает ток, запирая транзистор 11, Элемент матрицы переходит в состояние логического

"0". Блок 18 инвертирования оптического сигнала выполняет инверсию оптического сигнала на втором оптическсм входе, а блок 19 формирования логических функций реализует основные логические функции и управляет состоянием транзистора Il Под нулевыми потенциалами, подаюшимися на шины 15-17 управления, подразумеваются такие, которые достаточны для запирания транзистора 11 °

Изобретение по сравнению с известным облацает широкими функциональными возможностямп за счет того, что с его помощью появляется возможность

25 параллельно выполнять операции коньюнкции, дизьюнкции и сложения по модулю два с двумя бинарными изображениями, а результат представляется на этой же матрице.

30 фотодиода, анод которого подключен к

Форму ", а и з с б р е т е н и я

Оптоэлектронный элемент матрицы для выделения контура изображения по авт. св. Р 1439637, о т л и ч а ю— шийся тем, что, с целью расширения функциональных возможностей путем выполнения логических операций с двумя изсбражени -.ми, в него введены блок формирования логических функций, содержащий второй — пять и фотодиоды и три диода, и блок инвертирования оптического сигнала, содержащий шестой фстодиод,второй резистор, второй светодиод и второй транзистор, коллек-. îð к.оторого подключен к катоду второго светодиоца, анод которого подключен к шине питания и к первому выводу второго резистора, другой вывод которого подключен к базе второго транзистора и катоду шестого фотодиода, аноц которого подключен к змиттеру второго транзистора и ,шине нулевого потенциала, база первого транзистора подключена к аноду пятого фотодиода и катоду четвертогс

15839ч8

Составитель Л. Баранов

Редактор Л. Зайцева -Техред Л.Сердюкова Корректор Т. Палий

Заказ 2256. Тираж 568 Подписное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 катодам второго и третьего фотодио-. дов, анод четвертого фотодиода подключен к- аноду первого диода, катод которого подключен к первой шине управления, анод третьего фотодиода подключен к аноду второго диода, ка-, тод которого подключен к второй шине управления, катод пятого фотодиода подключен к катоду третьего диода, анод которого подключен к третьей шине управления, первый светодиод оптически связан с четвертым фотодиодом, второй светодиод оптически связан с третьим фотодиодом, оптичес" кие входы второго, пятого и шестого фотодиодов связаны между собой и являются вторым .оптическим входом оп1п тоэлектронного элемента матрицы.