Устройство для синхронизации памяти

Иллюстрации

Показать всеРеферат

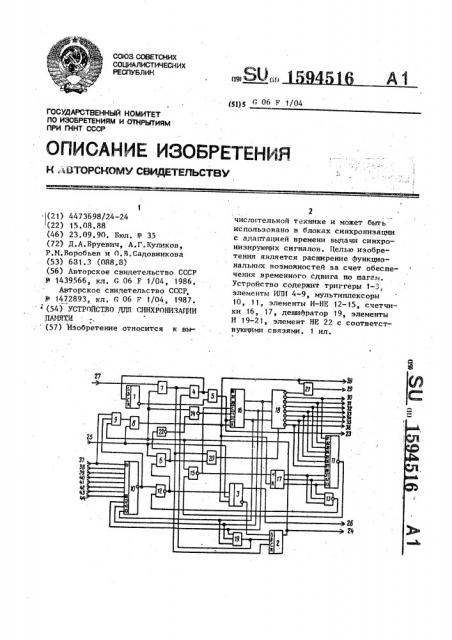

Изобретение относится к вычислительной технике и может быть использовано в блоках синхронизации с адаптацией времени выдачи синхронизирующих сигналов. Целью изобретения является расширение функциональных возможностей за счет обеспечения временного сдвига по шагам. Устройство содержит триггеры 1-3, элементы ИЛИ 4-9, мультиплексоры 10,11, элементы И-НЕ 12-15, счетчики 16,17, дешифратор 18, элементы И 19-21, элемент НЕ 22 с соответствующими связями. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТ НЕ(НИХ

РЕСПУБЛИК

w>®U аи щ) 06 Р 1/04

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И О ПОКРЫТИЯМ

ПРИ ГННТ СССР

- (21) 4473698/24-24 ,(22) 15.08.88 (46) 23.09.90. Бюл. Р 35 (72) Д.А.Бруевич, А.Г.Куликов, P..È.Âîðîáüåÿ и О.Б.Садовникова (53) 631.3 (088.8) (56) Авторское свидетельство СССР !! 1439566, кл. С 06 F 1/04, 1986.

Авторское свидетельство СССР, !! 14?2893, кл. С 06 F 1/04, 1987. (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗМЯИ

ПАНЯНКИ . (57) Изобретение относится к вы2 числительной технике и может быть использовано в блоках синхронизации с адаптацией времени выдачи синхронизируюших сигналов. Целью изобретения является расширение функциональных возможностей sa счет обеспечения временного сдвига по шагам.

Устройство содержит триггеры 1-3,. элементы ИЛИ 4-9, мультиплексоры

10, 11, элементы И-НЕ 12-!5, счетчики 16, 17, дешифратор 19, элементы

И 19-21, элемент НЕ 22 с соответствуют ими связями. 1 ил.!

594516

ЗО

Изобретение от«оснтся к вычислительной технике и мо>«ет быть использовано в блоках синхронизации с адаптацией времени выдачи синхронизирующих сигналов, Целью изобретения является расширение Аункциональных возможностей за счет беспечения временного сдвига ло шагам, 10

Па чертеже представлена схема устройства.

Устройство содержит первый 1, второй 2 и "ðåòèé 3 триггеры, первый

А> второй 5, третий 6> четвертый 7, пятый 8 и шестой 9 элементы ИЛИ, первьй 10 и второй 11 мультиплексоры, первый< 12, второй l3, третий 14 и четвертый 15 элементы И-11Е, первый

16 и второй 17 счетчики, деши<1>ратор

18,первый 19,второй 20 и третий 21 элементы И, элемент 11Е 22, выход 23 признака начала такта, выход 24 признака режима настройки, вход 25 разрешения ,увеличения временного сдвига выходных синхросигпалов устройства, выход 26 признака огкаэа устройства, вход 27 разрешения работы устройства, выход 28 признака начального состояния устройства, выход 29 признака уменьшения периода устройства, тактовые вь<ходн 30-36, входы 37-44 групны входов задания начальных условий устроиства.

Устройство работает следующим об35 разом, 1

В начале устройство устанавливается в исходное состояние путем сброса в "0" триггеров 1--3 и счетчиков

16 и 17 (цепь начальной установки не показана) .После этого устройство переходит в режим настройки синхроспгналов (СС), в процессе которой с помощью ЭВ11 или средств встроенного контроля проводится тестирование управляемого объекта, например, оперативной памяти, при .каждом обращении к ней устройство ьыдает последовательность СС, время задержки между которымп определяется как числом, так и величиной разделяющих их элемЕнтарных шагов, причем начальная последовательность СС <>ормируется с максимальными интервалами, что гарантирует надежную работу памяти, но не

55 обеспечивает высокого быстродействия.

Для повышения быстро><ей<ствия устройство выдаег в <)ормирователь синхроснгналов управляющие сигналы, вызываюп <е сдвиг CC. Настройка заканчивается установкой синхросигналов вблизи границы области устойчивой работы на рассгоянии, обеспечивающем надежнуи работу оперативной памяти при небольших колебаниях температуры и питающих напряжений. По окончании настройки устройство переходит в рабочий режим, в течение котброго производится запись и считывание из

ОЗУ полезной ив<1>ормации.

При достаточно малой величине элементарного шага E. (увеличение Е приводит к снижению быстродействия) в оперативной памяти возможно появление сбоев, например, ввиду значитель-ных изменений температуры или питающих напряжений, вероятность которых возрастает с увеличением продолжительности работы ОЗУ. Прн этом установленных в реж><ме .<астройки интерва- лон между СС может оказаться недостаточно для наде><ного Аункционирования памяти в новых условиях. В последнем случае устройство <>ормирует управляющие сигналы, вызывающие сдвиг

СС в глубину области. устойчивой работы на небольшое число элементарных шагов, повышая тем самы надежность . работы ОЗУ без значительного снижения быстродействия.

Назначение входных и выходных сигналов устройства состоит в следующем.

Выход 28 — импульс на этом выходе восстанавливает исходное число шагов между всеми СС, Выход 29 — последовательность импульсов на этом выходе позволяет. выбрать в <Ъормирователе синхросигналов величину дискретности

I (элементарного шага) сдвига СС. Первый импульс вызывает уменьшение дискретности с некоторого начального значения до величины Е» последующие импульсы - постепенное ее увеличение до значения Я, Выходы 30-36 последовательность импульсов. на каждом из этих выходов вызывает постепенное увеличение задержки соответствующего СС с шагом f,;. Выход 23— каждый импульс означает переход к настройке очередного СС, вызывая его смещение к началу <)ормирования временной диаграммы. Выход 26 — высокий уровень означает наличие в памяти устойчивого отказа (УО), не зависящего от ее временной диаграммы.

Выход 24 — низкий уровень — режим ет н;. вход 25, что вызывает повторное увеличение дискретности. Этот процесс продолжается до тех пор, S пока она не достигает некоторого значения f; при котором тестирование памяти заканчивается успешно и отрицательный импульс не поступает на вход 27.

С входа 27 отрицательный импульс через элемент ИЛИ, элемент И 20, дешифрат р 18 и элемент И 2 1 проходит в Аормирователь синхросигналов, где вызывает дополнительное увеличение дискретности до величины Е;, что необходимо дюж последующей надежной работы памяти (успешное прохождение теста при дискретности F; может носить случайный характер). Одновре20 менно отрицательный импульс с выхода элемента ИЛИ 7 через элемент ИЛИ 4 поступает на первый вход элемента

ИЛИ 5. Так как íà его втором входе присутствует низкий уровень напряже25 ния с инверсного выхода триггера 1, то отрицательный импульс через элемент ИЛИ 5 проходит íà cvMYHÐóâïèé вход счетчика 16 и своим задним Аронтом записывает в него .единицу. Крома того,с выхода 23 устройства он выдает30 ся в Аормирователь синхросигналов и переключает его с режима выбора дис-кретности на настройку первого СС, в результате чего последний смещается к началу Аормирования временной

35 дна граммы.

В случае, если его сдвиг вызывает нарушение работоспособности памяти, отрицательный импульс поступает на вход 25 и, пройдя элемент ИЛИ

4ц 6, элемент И 20 и дешифратор 18, выдается на выход 30 устройства (на инАормационных входах дешиАратора в этот момент присутствует код 001), что вызывает увеличение задержки пер45 вого CC на один шаг, При поступлении отрицательного импульса вновь на вход 25 процесс повторяется.

Постепенное наращивание числа шагов между началом временной диаграм5О мы.и первым СС происходит до тех .пор, пока работоспособность памяти не восстанавливается и отрицательный импульс на поступает на вход 27.

Пройдя элемент ИЛИ 7, элемент И 20, 55 дешиАратор 18, он выдается на выход

30, обеспечивая дополнительный сдвиг,первого GC на орин шаг в глубину области устойчивой работы (успешное прохождение теста в этом случае также может

1594516 6 настройки, высокий — рабочий режим (РГ), Входы ?7 и 25 — появление импульса на одном из этих входов означает соответственно работоспособность и неработоспособность памяти при данной временной диаграмме. Вход

37 — высокий уровень указывает на невозможность дальнейшего увеличения дискретности. Входы 38-44 — высокие уровни указывают на невозможность дальнейшего увеличения задержки выдачи соответствующего СС.

Так как начальная последовательность СС устанавливается Аормирователем синхросигналов с максимальными интервалами между всеми синхронизирующими сигналами, то тестирование памяти заканчивается успешно и на .вход 27 поступает отрицительный импульс. Поскольку на обоих входах элемента ИЛИ 7 оказываются логические нули (низкие уровни напряжения), то отрицательный импульс с его выхода через элемент И 20 проходит на стробирующий вход дешиАратора 18.

В этот момент на .информационных вхо; дах депифратора присутствуют логические нули, поэтому отрицательный импульс появляется на его первом выходе и через .элемент Н 21 выдается на выход 29 устройства. Поступив в формирователь синхросигналов, он вы-. зывает уменьшение дискретности сдвига СС с некоторой начальной величины до значения . Хотя число элементарных шагов между СС при этом не изменяется, однако за счет .значительного уменьшения величины шага происходит резкое сжатие временной диаграммы памяти. Одновременно отрицательный импульс с вьйода элемента

ИЛИ проходит элемент ИЛИ 4 и своим задним Аронтом устанавливает в "1" триггер 1, Если быстродействие памяти недоста-. точно высоко для работы с новой временной диаграммой, то средства встро-! енного контроля обнаруживают ошибки . и отрицательный импульс выдается на вход 25. Пройдя элемент ИЛИ 6, элемент И 20, дешиАратор 18 и элемент

И 21, он поступает в формирователь синхросигналов, который увеличивает .дискретность на некоторую небольшую величину до значения f . Если рас-.

1 ширения временной диаграммы оказывается недостаточно для восстановления работоспособности памяти, то

1 отрицательный импульс вновь поступа159451 быть случайным) . Одновременно отрицательний импульс через элементы

ИЛИ 4 и 5 поступает на суммирующий вход счетчика 14, увеличивая его содержимое на единицу и выдается на выход 23 устройства, в результате установка первого синхросигнала заканчивается, а второй синхросигнал смещается к началу Формирования временной диаграммы.

Установка синхросигналов с второ,го по шестой происходит аналогично„

При настройке седьмого синхросигаала в счетчике 16 записан код 111 и 15

1 йа выходе элемента И 19 присутствует логическая единица (нысокий уровень

:напряжения). Поэтому отрицательный импульс, пришедший с входа 27 на первый вход элемента ИЛИ. 4, на его 20 выход.не проходит. Однако он поступает на выход Зб через элеме IT И 20 и дешиФратор 18, вызывая дополнительный сдвиг седьмого СС на один шаг. Одновременно по заднему Фронту отри- 25 цательного импульса на выходе элемента ИЛИ 7 устанавливается в " 1" триггер 2, в результате чего на выход

24 устройства выдается признак рабочего режима, свидетельствующий о го- 30 тонности памяти к работе. Прохождение последующих импульсов с входа 27 на выход элемента ИЛИ 7 блокируется логической единицей на его втором входе. 35

Если в памяти присутствует неисправность, не зависящая от ее временной диаграммьг, то отрицательный импульс после первого тестирования поступает не на вход 27, а на вход 40

25, В этот момент на управляющих входах мультиплексора 10 присутствуют логические нули, а на первом информационном входе — логическая единица, свидетельствующая о невозможнос- 45 ти дальнейшего увеличения дискретности (начальная временная диаграмма Формируется с максимальными задержками между всеми СС). Поэтому на выходе мультиплексора 10 оказывается 50 логический ноль, а на выходе элемента И- IE 12 — логическая единица, поступающая на второй вход элемента

ИЛИ б и информационньп вход тригге.— ра 3, В результате отрицательный импульс с входа 25 на выход элемента»

ИЛИ 6 не проходит. В то же время по его заднему Фронту устанавливается в

"1" триггер 3, что приводит к выдаче на выход 26 устройства признака устойчивого отказа. Одновременно логический ноль с инверсного выхода триггера 3 поступает на установочный вход триггера 2, переводя его н единичное состояние и вызывая выдачу на выход 24 признака рабочего режима.

В процессе установки СС может возникнуть ситуация, когда дополнительный сдвиг какого-либо из синхросигналов в глубину области устойчивой работы принодит к недопустимому сокращению задержки между ним и одним из еще не настроенных СС. Например, если в результате дополнительного сдвига третьего СС задержка между ним и шестым синхросигналом окажется меньше допустимой, то при настройке следующего, четвертого СС, отрицательные импульсы на вход 25 приходят до тех пор, пока на вход 4 1 устройства не поступает логическая единица. Так как на управляющих входах мультиплексора 10 в этот момент присутствует код 100., то на его выходе оказывается низкий уровень напряжения, поступающий на второй вход элемента ИЛИ 9. При наличиии возможности увеличения дискретностИ на. его первом входе также присутствует низкий уровень. В результате логический ноль поступает на первый вход элемента ИЛИ 8.

С приходом отрицательного импульса на вход 25 на- обоих входах элемента ИЛИ 8 оказываются низкие уровни и отрицательный импульс с его выхода проходит на вход сброса триггера 3. Так как переключение последнего происходит по положительному перепаду напряжения на синхронходе (заднему Фронту отрицательного импульса), то триггер 3 остается в нулевом состоянии и выдачи признака устойчивого отказа не происходит, Одновременно логическая единица с выхода элемента И-HE 12 блокирует прохождение отрицательного импульса через элемент ИЛИ 6 °

С выхода элемента ИЛИ 8 отрицательный импульс поступает также на вход сброса счетчика 16 и через элемент И 21 в

Формирователь синхросигналов, где увеличивает величину дискретности.

Кроме того, он выдается на выход 28 устройства, восстанавливая исходное число шагов между всеми СС, В резуль15945 1о

1П

1О тате процесс установки синхросигналов начинается сначала (н счетчике 16 записан нулевой код), но уже с большей величиной дискретности. Таким

5 образом, искчючается возможность сбоев при настройке временной диаграммы, вызванных JToполнительным сдвигом синхросигналов в глубину области устойчивой работы, В рабочем режиме при отсутствии ошибок в памяти на вход 27 периодически поступают отрицательные импульсы. Однако присутствие высокого уровня на втором входе элемента

ИГЙ 7 не позволяет им пройти на его выход и сАормированная при настройке последовательность СС сохраняется.

При значительном изменении температуры или питающих напряжений блок встроенного контроля может обнаружить в памяти ошибку, и на вход

25 поступает отрицательный импульс.

Если в сАормированной последовательности СС сер;мой синхросигнал устанавливается в .срайнем положении и возможность его сдвига в глубину области устойчивой работы отсутствует, то на вход 44 устройства поступает логическая единица. Так как на

30 управляющих входах мультиплексора 10 присутствует код 111,то íà его выходе появляется логический ноль, а на выходе элемента И-НЕ 12 и информационном входе триггера 3 — логическая единица. В результате отрицатель-35 ный импульс с входа 25 поступает на синхровход триггера 3 и устанавливает его в "1", что приводит к выдаче на выход 26 признака устойчивого отказа. При этом временная диаграм- 40 ма СС не изменяется.

Если седьмой синхросигнал не находится в крайнем положении, то отрицательный импульс с входа 25, 45 пройдя элемент ИЛИ 6, элемент И 20, поступает на стробирующий вход дешифратора 18. Так как на его информационных входах присутствует код 111, то отрицательный импульс оказывается 0 на выходе 36, обеспечивая, сдвиг седьмого СС на один шаг в глубину области устойчивой работы. Одновременно отрицательный импульс с выхода элемента ИЛИ 6 инвертируется элементом . НЕ 22, и на втором входе элемента

И-HF..14 появляется положительный импульс. Так как на первом входе элемента И-HF. 14 в рабочем режиме присутствует логическая единица, то на его выходе оказывается отрицательный импульс, который поступает на вычитаюглй вход счетчика 16. По его заднему фонту происходит уменьшение содержимого счетчика 16 на единицу и на его выходах оказывается код

110.

Если сдвиг седьмого СС не приводит к устранению ошибки в памяти, то на вход 25 выдается отрицательнйй импульс.

При отсутствии логической единицы на входе 43 устройства отрицательный импульс, пройдя элемент ИЛИ 6, элемент И 20, дешифратор 18, выдается на выход 35 устройства (на информационных входах дешиАратора присутствует код 110), что вызывает увеличение задержки шестого СС на один шаг

Одновременно с выхода элемента ИЛИ 6 отрицательный импульс через элемент

НЕ 22 и элемент И-НЕ 14 проходит на вычитающий вход счетчика 16 и уменьшает его содержимое на единицу, в

\ результате чего на его выходах оказывается код 101. Сдвиг синхросигналов с пятого по второй происходит аналогично.

При сдвиге первого синхросигнала отрицательный импульс выдается на выход 30 устройства и поступает на первый вход мультиплексора 11. Поскольку счетчик 17 находится в нулевом состоянии и на управляющих входах мультиплексора 11 присутствует код

000, то на его выходе появляется положительный импульс, который поступает на второй вход элемента И-НЕ 15.

Так как на первом входе элемента

И-НЕ 15 в рабочем режиме присутствует высокий уровень напряжения, на его выходе появляется отрицательный импульс, который поступает на вход предварительной записи счетчика 16. По его переднему Аронту происходит занесение в счетчик 16 инАормации с информационных входов, которые соединены с ниной единичного потенциала.

В результате на выходах счетчика

16 появляется код 1 11. Одновременно с выхода элемента И-НЕ 15 отрицательный импульс поступает на суммирующий вход счетчика 17 и своим задним Аронтом увеличивает его содержимое на единицу. На выходах счетчика 17 оказывается.код 001, который поступает на управляющие входы мультиплексора

11. Таким образом, на первом этапе

1594516

40 перенастройки осуществляется сдвиг с первого на седьмой СС в глубину области устойчивой работы. Тем самым происходит увеличение времени задерж5 ки между всеми СС и началом Аормирования временной диаграммы.

При последующих поступлениях отрицательного импульса на вход 25 устройства процесс повторяется, начиная с седьмого СС. Однако, так как на управляющих входах мультиплексора 11 присутствует код 001, то на его выходе появляется положительный импульс ,при сдвиге второго СС. При этом на выходе элемента И-HF, 1.5 оказывается отрицательный импульс, поступающий на суммирующий вход счетчика 17 и вход предварительной записи счетчи ка 16. В результате содержимое счетчика 17 увеличивается на единицу и на его выходах появляется код 010,, а счетчик 16 переводится в состояние

1tI1I. Таким образом, при следующей выдаче отрицательного импульса на 25 вход 25 происходит сдвиг на один шаг седьмого, а не первого СС (время выдачи первого синхросигнала не изменяется). Тем самым на втором этапе перенастройки происходит увелиЗО чение времени задержки между первым и всеми остальными:еинхросигналала на величину Я..

Дальнейшая выдача отрицательных импульсов на вход 25 приводит к сдвигу. с седьмого по третий СС. При этом З5 после третьего этапа перенастройки время задержки между BTopbIM и оставшимися синхросигналами увеличивается на величину

Таким образом, в рабочем режиме при, значительном изменении температуры или питающих напряжений происходит расширение временной диаграммы синхросигналов. Этот процесс мо- 45 жет прололжаться до тех пор, пока очередной сдвиг СС не приведет к восстановлению надежного Аункционирования памяти.

Если .того не происходит, то после увеличения интервалов между всеми СС в счетчике 17 оказывается код

111. При этом логические единицы появляются на всех входах элемента

И-ЛЕ 1" и на его выходе оказывается логический ноль, который поступает на второй вход элеме:нта И-IIE 12. С выхада последнего логическая единица поступает на инАс рмационный вход триггера 3 и на второй вход элемента ИЛИ 6. ГГри поступлении очередного отрицательного импульса на вход 25 триггера 3 устанавливается в единичное состояние и на выход 26 устройства выдается признак устойчивого отказа.

Формула изобретения

Устройство для синхронизации па( мяти, содержащее три триггера, шесть элементов ИЛИ, три элемента И,дешифратор, элемент НЕ,первый счетчик и первый мультиплексор, причем синхровход первого триггера соединен с выходом первого элемента ИЛИ и с .первым входом второго элемента ИЛИ, выход которого соединен с суммирующим входом первого .счетчика и является выходом признака начала такта устройства, разрядные выходы первого счетчика

Г соединены с инйормационными входами . дешиФратора, с управляющими входами первого мультиплексора и с входами первого элемента И, первый вход первоro элемента ИЛИ соединен с выходом четвертого элемннта ИЛИ, с первым входом второго элемента И и с синх-. ровходом второго триггера, прямой выход которого соединен с первым входом шестого элемента ИЛИ, с первым входом четвертого элемента ИЛИ и является выходом признака режима настройки устройства, выход первого элемента И соединен с вторым входом первого элемента ИЛИ и, с информационным входом второго триггера, первый вход третьего элемента ИЛИ соединен с первым входом пятого элемента ИЛИ, с синхровходом третьего триггера и является входом разрешения увеличения временного сдвига выходных синхросигналов устройства, прямой выход третьего триггера является выходом признака отказа устройства, инверсный выход третьего триггера соединен с входом установки в "1" второго триггера, инйормационньй вход первого триггера соединен с шиной единичного потенциала устройства, инверсный выход первого триггера соединен с вторйм входом второго элемента ИЛИ, стробирующий вход дешифратора соединен .с выходом второго элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ, второй вход которого соединен с индюрмационным входом

159451С

Составитель Е.Торопов

Редактор М.Бланар Техред M.Õoäàíè÷ Корректор 0. Ф пле

Заказ 2829 Тираж 561 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 третьего триггера„второй вход четвертого элемента ИЛИ является входом разрешения работы устройства„выход пятого элемента ИЛИ соединен с входа и сброса в "0" первого счетчика и третьего триггера, с первым входом третьего элемента И и является выходом признака начального состояния устройства, первый инверсный выход дешифратора 10 соединен с вторым входом третьего элемента И, выход которого является выходом признака уменьшения периода выходных импульсов устройства, выход шестого элемента ИЛИ соединен с вто- 15 рым входом пятого элемента ИЛИ, инверсные выходы дешиАратора-с второго по и-й являются тактовыми выходами соответственно с первого по и-й устрочства, первый инАормационный вход пер- g0 вого мультиплексора соединен с Вто» рым входом шестого элемента ИЛИ и яв. ляется первым входом группы задания начальных условий стройства, инАормационные входы первого мультиплек- 25 . сора с второго по и-й являются входами соответственно с второго по и-й задания начальных условий устройства, инверсный выход первого мультиплексора соединен с третьим входом шесто- 30

ro элемента ИЛИ, о т л и ч а ю ш е ес я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения временного сдвига по шагам, в него введены четы35 ре НЕ, второй счетчик и второй мультиплексор, причем первый вход первого элемента И-НЕ соединен с инверсным выходом первого мультиплексора. второй вход первого элемента И-НЕ со динен с выходом второго элемента И-НЕ, входы которого соединены с управляюгртми входами второго мультиплексора и с разрядными выхо-. дами второго счетчика, первый вход третьего элемента И-НЕ соединен с первым входом четвертого элемента

И-НЕ и с прямым выходом второго триггера, выход первого элемента И-НЕ соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с входом элемента НЕ, выход которого соединен с вторым входом третьего элемента И-НЕ, выход которого соединен с вычитаюшим входом первого счетчика, выход четвертого элемента

И-НЕ соединен с входом разрешения записи первого счетчика и с сукмнруюшим входом второго счетчика, вход сброса в "0" которого соединен с выходом пятого элемента ИЛИ, второй вход .четвертого элемента И-НЕ соединен с инверсным выходом второго мультиплексора, информационные входы которого с первого по и-й соединены с инверсными выходами дешифратора соответственно с второго по п-й, (n+1)-й йнформационный вход второго мультиплексора.соединен с инАормационными входами первого счетчика и с шиной единичного потенциала устройства;