Элемент памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах, реализуемых на базовых матричных кристаллах. Целью изобретения является повышение надежности элемента памяти. Для этого в элемент памяти введены третий и четвертый элементы НЕ и третий и четвертый ключевые элементы на транзисторах. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (g1)g G l1 С 11/40

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯЧ

ПРИ ГКНТ СССР (21) 4487478/24-24 (22) 28,09,88 (46) 23.09.90. Бюл . N - 35 (72) А,И.Моторин, В,В.Теленков, А,Д.Прохоров и Ю,П,Фомин (53) 68! .327.66 (088.8) (56) IEEE journal of Solid-State

Circuits, Vol, $с.-20, 9- 5, October, 1985.

EP К- 0224887, кл, G 11 С 1 1/40, о публи к. 19 86, Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, реализуемым на базовых матричных кристаллах.

Цель изобретения — повышение надежности элемента памяти.

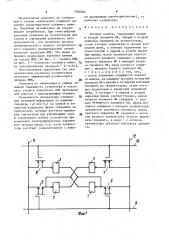

На фиг, 1 представлена принципиальная схема элемента памяти; на фиг. 2 — топология ячейки БМК; на фиг, 3 — топала гическая реализация элемента памяти, Элемент памяти содержит первый !, второй 2, третий Зи четвертый 4 элементы НЕ, третий 5, первый 6, четвертый

7 и второй 8 ключевые элементы на транзисторах, первую 9 и вторую 10 адресные шины, прямую i! и инверсную

12 разрядные шины, Элемент памяти работает следующим образом.

Элементы НЕ 1 и 2 образуют триггерное кольцо, которое осуществляет функцию хранения информации. Элементы НЕ 3 и 4 предназначены для операции чтения, Поскольку информация с

„„ЯО„„Ы946О4 (54) ЭЛЕМЕНТ ПАМЯТ!! (57) Изобретение относится к вычислительной технике и может быть использовано в запоминаицих устройствах, реализуемых на базовых матричных кристаллах, Целью изобретения является повышение надежности элемента памяти.

Для этого в элемент памяти введены третий и четвертый элемент НЕ и третий и четвертый ключевые элементы на транзисторах. 3 ил„ триггерного кольца поступает на входы элементов КЕ 3 и 4, то влияния ем.кости разрядных шин 1 и 12 при операции считывания (открываются транзисторы 7 ii 8 р канальные) при поступлении на их затворы сигнала 0 нет, I1 11

Следов ат ель но, пар азитная емкость на разрядных шинах 1 и 12 не оказывает илия пия па со стоя ние три г,"ер а, При этом считывается парафазная информация (разрядные шины 11 и 12) поэтому момент истинной считанной информации легка определяется при наличии парафазы 1,0 или 0,1, Запись информации осуществляется поступлением парафазной информации на разрядные шины 11 и 12 и открыванием транзис торов 5 и 6 (n-канальные транзисторы) поступление по шине 9 уровня "1". По скольку при з апис! все равно необходим этап воздействия на триггерное кольцо, то в этом случае не важно наличие паразитной ем<ости на шинах 11 и 12, ! 594604

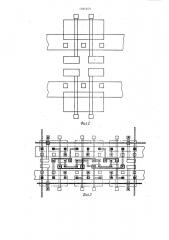

Предлагаемая развязка по считыванию и записи значительно повышает на дежные характеристики элемента памяти. Подобная организация не ограничивает потребителя„ При этом выбраны ключевые элементы на транзисторах длй записи и считывания различного типа проводимости, что позволяет достичь симметричности и полного топологичес- !и кого покрытия принципиальной схемой ячеистой структуры Б!1К, Это видно на примере реализации элемента памяти на основе SNK, На фиг. 2 — ячейка БИК, на фиг, 3 — топология элемента памя- ти (двухуровневая разводка — А !и A2 ).

Использование однотипных (по геометрическим размерам) транзисторов позволяет эффективней использовать площадь BMK 4 20

Развязка по считыванию и записи повышает надежность устройства и позво-. ляет строить накопитель ОЗУ произвольной емкости с неразрушающим чтением, Возможность определения считыва- 25 ния истинной информации по наличию парафазы 1,О или О, на прямой и инверсной разрядных шинах позволяет не производить сложных расчетов времен,ных параметров дпя управляющих схем gg и гарантирует работу устройства при изменении электрофиэических парамет1 ров транзисторов, т. е. если транзисторыы работают (переключаются с любыми временными характеристиками ), то работает устройство.

Формул а и зо бр ет ения

Элемент памяти, содержащий пер вый и второй элементы НЕ, первый и второй ключевые элементы. на транзисторах, стоки которых подключены к прямой разрядной шине, а затворы подключены соответственно к первой и второй адрес" ным шинам, исток транзистора первого ключевого элемента соединен с входом первого элемента НЕ и выходом второго элемента НЕ, вход которого соединен с выходом первого элемента НЕ, отличающийся тем,что, с целью повышения надежности элемента памяти, он содержит третий и четвертый элементы НЕ и третий и четвертый ключевые элементы на транзисторах, стоки которых подключены к инверсной разрядной шине, а затворы - к первой и второи адресным шинам соответственно,. выход второго элемента. НЕ соединен с вхо дом четвертого элемента НЕ, выход которого соединен с истоком транзистора четвертого ключевого элемента, выход третьего элемента НЕ соединен с истоком второго транзистора второго ключевого элемента а вход — с истоком транзистора третьего ключевого элемента.

1594б04

Фиг.2