Элемент памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в постоянном 3 aпo инaroщeм устройстве на МДП-транзисторах, программируемых технологически. Цель изобретения повьпиение надежности элемента памяти - достигается тем, что расстояние между краями первой и третьей полупроводниковых областей составляет 0,3-0,4 от расстошшя между краями первой и второй полупроводниковых областей, i йвП. ф-лы, 4 ил.

, ИВ (Ш

СОЮЗ COBETCHHX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51)5 а l l С 17/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОЧМРЬП ИЯМ

ДРИ П Нт СССР (46) 23. 09. 92. Бюл. Р 35 (21) 4682708/24 (22) 27.04. 89

1 (71) Научно-исследовательский инсти" тут нВосток (72) В.И. Овчаренко (53) 681.327.66{088.8) (56} Патент ClllA Р 4546453, кл . С 11 С 17/00, 1980.

Патент США У 4328563, кл. Г 11 С 17/00, 1982. (54) ЭЛЕИЕЖ ПАМЯТИ

Изобретение относится к вычислительной технике н может быть использовано в матричном накопителе для постоянного запоминающего устройства на ИДП-транзисторах с различной дли" ной какала, программируемой технологически.

Целью изобретения является повышение надежности элемента. памяти.

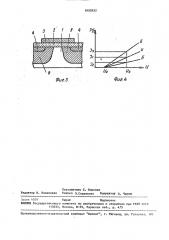

На фиг.l-3 приведены сечения эле.ментов. памяти, находящихся в различных устойчивых состояниях, íà фигo4 их вольт-амперные характеристики (а-в соответственно).

Элемент памяти содержит полупроводниковую подложку l диэлектрический слой 2, проводящую область 3, первую.. и вторую полупроводниковые области 4 ° третью полупроводниковую область 5, четвертую полупроводниковую область б

Проводящая область 3 является зат" вором элемента памяти (ИДП-транзисто" (57) Изобретение относится к вычисли тельной технике и может быть использовано в постоянном запоминающем устройстве на МДП-транзисторах, про" граммируемых технологически, Цель изобретения — повышение надежности элемента памяти — достигается тем, что расстояние между краями первой и третьей полупроводниковых областей . составляет 0,3-0,4 от расстояния между краями первой и второй полупроводниковых областей. 1 э.п. ф-ли, 4 ил. ра с обогащением), диэлектрический слой 2 — подзатворным диэлектриком, области.4 второго типа проводимостистоком, истоком, области 5,6 второго типа проводимости — областями истока и стока, уменьшающими эффективную длину канала при постоянной ширине, области 3.

Элемент памяти {фиг.l) с вольтамперной характеристикой "а" характеризует одно устойчивое состояние.

Элемент памяти {фиг.2) без области

5 второго типа проводимости с наи меньшей крутизной вольт-амперной ха--. рактеристики "б" характеризует другое ®р состояние.

В матричном накопителе для постоянного запоминающего устройства на однобитных элементах памяти, находя» щихся. в одном из двух устойчивых состояний, используют элементы (фиг 1) дпя единичного состояния и

11600552 элементы (Фиг.2) для нулевого состояния с

Работа элемента памяти заключает" ся в следующем, 5

При подаче относительно истока низкого положительного напряжвтия (+5 В) на область 3, на сток - более низкого положительного напряжения (I-2 0) череэ него протекает ток, об- 10 ратно пропорциональный эффективной длине канала. С помощью усилителя считывания величина тока (больщая или малая) преобразуется в двоичную информацию (единичную ипи нулевую).

При подаче нулевого напряжения на область 3 элементы памяти (фиг.1, 2) находятся в закрытом состоянии, ток через нпх пе протекает.

В элементе памяти (Фиг.3) за счет 20 размещения области 6 второго типа проводимости обеспечивается наименьшая эффективная длина канала, наиболь- . шая крутизна вольт-амперной характеристики нв", чем для элементов (фиг.l. 5

2), что характеризует,третье состояние.

Такой элемент памяти {фиг.З) паря" ду с элементами (фиг.l,2) может быть использован в ПЗУ с троичной логикой inn n ПЗУ с двоичной логикой с преобразованием троичной инФормации в двоичную с использованием соответствующих усилителей считывания, при этом информационная емкость накопи" теля увеличиватеся в 1,5 раза. Аормула изобретения

1. Элемент памяти, содержащий полупроводниковую подложку первого 40 типа проводимости, диэлектрический слой, расположенный на поверхности полупроводниковой подложки, первую и вторую полупроводниковые области второго типа проводимости, расположенные в приповерхностном слое полупроводниковой подложки, проводящую область, расположенную на диэлектрическом слое между первой и второй полупроводниковыми.областямИ с перекрЫтием их краев, третью полупроводниковую область второго типа проводимости, расположенную в приповерхностном слое полупроводниковой подложки между первой и второй полупроводниковыми областями с примыканием к краю первой полупроводниковой области, о т и и ч а ю шийся тем, что, с целью повыщения надежности эпе» мента памяти, расстояние между краями первой и третьей полупроводниковых областей составляет 30-40% от расстоя ния между краями первой и второй полупроводниковых областей.

2. Элемент памяти по и.1, о т л и" ч а ю шийся тем, что, с целью увеличения информационной емкости элемента памяти, он содержит четвертую полупроводниковую область второго типа проводимости, расположенную в приповерхностном слое полупроводникь» вой подножки между первой и второй полупроводниковыми областями с примыканием к краю второй полупроводниковой области, причем расстояние между краями второй и четвертой полупровод пиковых областей составляет 30"407, от расстояния между краями первой и . второй лолупроводпиковых областей!

600552

Составитель С.. Королев

Техред Л.Сердюкова Корректор C. Черни

ЮВ ЮВЮ Ю Ol ЮВ В В Ю ВЮВВЮЮВВВФЮЮВЮ Ю»Ю Ю

Тираж . Подписное комитета по изобретениям и открытиям при ГК1П СССР

Москва, Ж-З5, Раушская наб., д. 4/5

Редактор Н. Каменская

Заказ 4059

ВНИИПИ Государственного

113035, «» ВЮ ° Ю ЮВЮ ЮВ ВЮ ° В ° В»»

Производственно-издательский комбинат "Патент", d. Ужгород, ул. Гагарина, 101