Адресный формирователь

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при проектировании постоянных запоминающих устройств. Цель изобретения - расширение области применения формирователя за счет формирования сигнала выборки по нескольким адресам. Это достигается тем, что в каждом элементе 1 памяти формирователя содержится второй запоминающий транзистор 4. Низкое пороговое напряжение одновременно обоих транзисторов 3, 4 обеспечивает сигнал низкого уровня с обоих выходов элемента 1 памяти. В результате блок 2 сравнения выдает сигнал выборки на выходе 6 при произвольном адресном коде на входах 5, соотвествующих данному элементу 1 памяти. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИК (51)5 С 11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР (21) 4631365./24-24 (22) 03.01.89 (62) 4354859/24-24 (23) 04.01.88 (46) 15. 11.90. Бюл, Р 42 (72) Ь.Э.Тенк (53) 681.327.6 (088.8) (56) Зарубежная электронная техника, 1985, К 10, с. 43, рис. 27,б.

Конопелько В,К,, Лосев В.В. Надежное хранение информации в полупроводниковых запоминающих устройствах.

И.: Радио и связь, 1986, с, 79, рис. 3.16. (54) AgPECHbIA ФОРМИРОВАТЕЛЪ (57) Изобретение относится к вычислительной технике и микроэлектронике

„„SU„, 1607013 А 1

2 и может быть использовано при проектировании постоянных запоминающих устройств. Цель изобретения — расширение области применения формирователя за счет формирования сигнала вы- . борки по нескольким адресам. Это достигается тем, что в каждом элементе 1 памяти формирователя содержится вто" рой запоминающий транзистор 4 ° Низкое пороговое напряжение одновременно обоих транзисторов 3, 4 обеспечивает сигнал низкого уровня с обоих выходов элемента 1 памяти. В результате блок

2 сравнения выдает сигнал выборки на выходе б при произвольном адресном коде на входах 5, соответствующих данному элементу 1 памяти. 1 ил.

1607013

Изобретение относится к вычислительной технике и микроэлектронике, а именно к полупроводниковым интегральным микросхемам, и может быть использовано при проектировании постоянных запоминающих устройств (ПЗУ).

Целью изобретения является расширение функциональных возможностей формирователя за счет формирования 10 сигнала выборки по нескольким адресам.

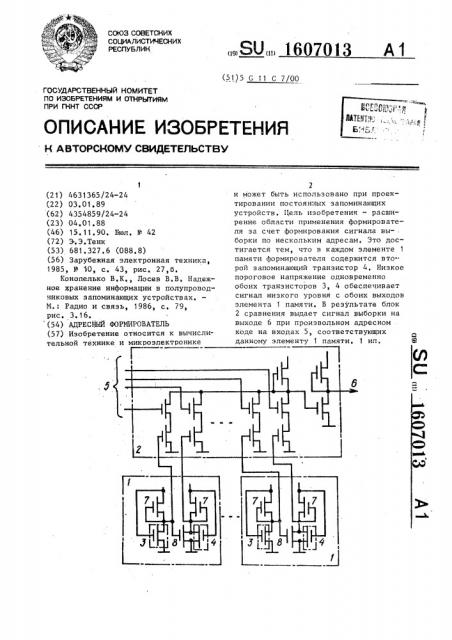

На чертеже представлена электри, ческая схема формирователя.

Адресный формирователь содержит 15 элементы 1 памяти, блок 2 сравнения.

Хранение адреса производится на первых и вторых запоминающих транзисторах 3, 4 элементов 1 памяти. Входы первой группы блока 2 сравнения явля- 20 ются адресными входами 5 формирователя, а выход — выходом 6 формирователя. Кроме запоминающих транзисторов

3, 4 элементы 1 памяти состоят из двух нагрузочных транзисторов 7, клю- 25 чевого транзистора 8.

Формирователь работает следующим образом.

Наибольший выигрыш дает использование формирователя в вычислительных системах, в состав которых входях ПЗУ с "масочным" способом занесения информации, т.е. занесением информациции в.процессе изготовления ПЗУ, В этом случае адресный формирователь размещается на одном кристалле с ПЗУ и программируется одновременно и тем же способом, что и при занесении информации в накопитель ПЗУ. Наиболее распространенным способом занесения 40 информации в накопитель ЗУ является варьирование пороговыми напряжениями транзисторов накопителя. Одновременно и каждый из транзисторов 3, 4 изготавливается с пороговым напряжением, 45 которое превышает или значительно ниже напряжения питания. При этом низкое пороговое напряжение может иметь транзистор 3, либо транзистор

4, либо транзисторы Зи 4 одновремен-" но, что соответствует состояниям элемента 1 памяти "Лог.1", "Лог.О" либо безразличному состоянию. В последнем случае сигнал на выходе 6, разрешающий обращение к ПЗУ, будет вырабатываться при любом коде адреса на.входе

5 данного. элемента 1 памяти.

Если пороговое напряжение транзистора 3 ниже напряжения питания, то

его с ток и подключенный к стоку вход блока 2 находятся в состоянии "Лог.О", а сток транзистора 8 — в состоянии

iс II

Лог. 1, если пороговое напряжение соответствующего транзистора 4 превышает напряжение питания. Если пороговые напряжения и транзистора 3, и транзистора 4 данного элемента 1

7 памяти ниже напряжения источника питания, то оба выхода этого элемента 1 памяти и подключенные к ним входы блока 2 находятся в состоянии "Лог.

Pft

Код адреса, поступающий на входы

5, сравнивается в блоке 2 сравнения с ожидаемым, хранящимся в блоке элементов 1. В случае совпадения указанных кодов на выходе 6 устройства появляется разрешающий сигнал (сигнал выбора, ПЗУ). Если в одном или нескольких элементах 1 хранится безразличное состояние, то разрешающий сигнал на выходе 6 появится независимо от кода на соответствующих входах 5.

Формула изобретения

Адресный формирователь, содержащий блок сравнения, выход которого является выходом формирователя, входы первой группы — адресными входами формирователя, элементы памяти, каждый из которых состоит из двух нагрузочных транзисторов, ключевого транзистора и первого запоминающего транзистора, исток которого соединен с истоком ключевого транзистора и подключен к шине нулевого потенциала формирователя, а сток соединен с затвором ключевого транзистора, с соответствующим входом второй группы блока сравнения и с истоком первого нагрузочного транзистора, сток которого соединен со стоком второго нагрузочного транзистора и подключен к шине питания формирователя, исток второго нагрузочного транзистора соединен со стоком ключевого транзистора и с соответствующим входом второй группы блока сравнения, о т л и ч а ю щ и йс я тем, что, с целью расширения области применения формирователя за счет формирования сигнала выборки по нескольким адресам, он содержит в каждом элементе памяти второй запоминающий транзистор, сток и исток которого соединены со стоком и истоком соответственно ключевого транзистора, 5 1ЬО7013 б а затвор соединен с затвором первого зисторов, затворы которых соединены запоминающего транзистора и стоками с истоками первого и второго нагру" первого и второго нагрузочных тран- зочных транзисторов соответственно.

Составитель С.Королев

Редактор А.Маковская Техред M.Õoäàíè÷ Корректор Л.Бескид

3ак аз 3552 Тираж 487 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101