Матричный накопитель для постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в постоянных запоминающих устройствах. Целью изобретения явля-; ется повышение выхода годных матричного накопителя для постоянного запоминающего устройства. Поставленная цель достигается тем что матри щый накопитель .содержит дополнительную адресную шину и электрически программируемьте ячейки памяти, образ тощие дополнительную строку матрштного накопителя, адресные входы электрически программируемых ячеек памяти объединены и соединены с дополнительной адресной шиной накопителя. 4 шх.

09)%У (Ш

CQO3 СОВЕТСНИХ

COUHAËÈÑÒÈ×ÅÑHÈМ

РЕСПУБЛИН

А1 (51)5 С 11 С 1f 40

ОПИСАНИЕ ИЗОБРЕТЕ

M АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЦИ КОМИТЕТ

Il0 ИЗОБРЕТЕНИЯМ И ОТНЯТИЯМ

ПРИ ГКНТ СССР,(46) 23.09.92. Бюл. Р 35 (? 1) 44 70371/24 (22) 04.08.88 (72) В.И.Овчаренко ,(53) 681.327.66(088.8) (56) Электррника, 1987, Р 14, с.25-32.

Авторское свидетельство СССР

В 683600, кл. G 11 С 11/40, 1979. ,(54) МАТРИЧНЫЙ НАКОПИТЕПЬ ДЛЯ ПОСТО"

ЯННОГО ЗАПОМИНАИЩЕГО. УСТРОЙСТВА (57) Изобретение относится к вычислительной технике и может быть использовано в постоянных запоминающих i

Изобретение относится к вычисли . тельной .технике и может быть использовано в постоянном запоминающем устройстве.

Целью .изобретения является повыше ние выхода годных матричного накопи,теля.

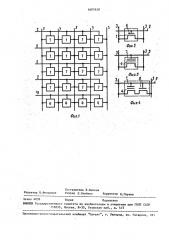

На фиг.1 приведена электрическая схема фрагмента матричного накопителя; на фиг.2 приведена схема ячей-. ки памяти первой и второй групп; на . фиг.3 приведена схема электрически .программируемой ячейки памяти, состоящей из запоминающего лавинно-инжекционного транзистора;Йа фиг.4 приведена схема второго варианта электрически программируемой ячейки па" мяти.

Матричный накопитель содержит ячейки памяти 1 первой и второй групп, адресные шины 2, разрядные шины 3, электрически программируемую

Ф устройствах. Целью изобретения явля" ется повышение выхода годных матричного накопителя для постоянного запоминающего устройства. Поставленная цель достигается тем, что матричный накопитель, содержит дополнительную адресную шину и электрически про.граммируемые ячейки памяти, образующие дополнительную строку матричного. накопителя, адресные входы электрически программируемых ячеек памяти объединены и соединены с дополнительной адресной шиной накопителя. 4 ил. ячейку памяти 4 дополнительную ад- . Св ресную шину 5, МПП-транзистор б ячеек памяти 1, запоминающий лавинноинжекционный транзистор 7 ячейки памяти 4, переключающий транзистор 8 ячейки памяти 4.

Ячейки памяти 1 первой и второй групп программируются технологически и отличаются друг. от друга тем, что их пороговые напряжения разные и устанавливаются в процессе изготовления.

Ячейки памяти 4 программируются электрически и могут быть выполнены, например, в виде запоминающего лавинно-инжекционного транзистора 7 с или без переключающего транзистора 8, или в виде переключающего транзистора с резистором, диодом или конденсатором. (на чертежах не показаны) .

Работа матричного накопителя заключается в.следующем. В режиме с и!

607620 т11113lfttftt ин1формации на адресную шину подают низкое положительное ка пряжение, на остальные шины 2 — нулет1ое напряжение. На вь1браннь1е раз" рядные шины 3 пода1от низкое положигелькое напряжение, а на соседние выбранные шины 3 -- нулевое напряжение, на остальные разряднь1е шины 3 низкое положительное напряжение. Йсли пороговое напряжение транзистора

6 ячейки памяти ) низкое, то через него протекает токр что эквивалент но единичному состоянию. Если пороговое напряжение транзистора 6 высокое, то через него не протекает ток, что эквийалентно нулегому состоянию.

Если npff npnBepf

I приводит к высокому пороговому напряжению выбранного запоминающет о транзистора 7, что эквивалентно нулевому состоянию в режиме считываНИ11 „

Введение дополнительной адресной шины и строки электрически программируемых ячеек памяти позволяет при незначительном увеличении площади накопителя повысить выход годйых накопителяе

Формула изобретейия;

Матричный накопитель для постоянного запоминающего устройства, со"

15 держащий адресные и разрядные шины, в перекрестиях которых расположены . ячейки памяти. первой и второй групп, адресные входы ячеек памяти первой и второй групп, образующие строку .;

20 матричного накопителя, объединены и соедйнены с адресной шиной накопителя, первые и вторые информационные выводы ячеек памяти первой и второй групп, образующие нечетный стСЙбец матричного накопителя, объединены и соединены соответствейно с не-. четной и четной разрядными.шинамй, первые и вторые информационные выводы ячеек памяти. первой и второй

30 групп, образующие четный столбец ма" тричного накопителя, объединены и со единены соответственно с четной и не". четной разрядными шинами матрйчного накопителя, о т л и ч а ю щ и Й с я тем, что, с целью повышения выхода годных матричного накопителя, он содержит дополнительную адресную Шину и электрически программируемые ., ячейки памяти„. образующие дополни40 тельную строку матричного накопителя, адресные входы электрически программируемых ячеек памяти объедмнены и соединены с дополнительной адресной шиной матричного накопйтеля.

1б07620

Составитель В.Венков

Техред Л.Олийнык Корректор В.Гирияк

Редактор В. Фельдман

Заказ 4059 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГХЯТ СССР

113035, Москва, Ж"35 ° Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 г