Способ изготовления матричного накопителя для постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к технологии изготовления полупроводниковых интегральных микросхем, и может быть использовано для изготовления матричного иакопителя электрически перепрограммируемого постоянного запоьшнающего устройства. 1Гёлью изобретения является повьтгение быстродействия матричного накопителя. Преимуществом матричного накопителя является наличие областей малой ширинь1, полученных без использования малой нормы проектирования, и обеспечение малой площади перекрытия выступа диффузионной области без использояания дополнительной фотолитографической операции с малыми размерами.Кроме того, уменьшены размеры ячейки памяти. 8 ил. Г

СО)03 СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕаЪБЛИН

09) 01) (51) 5 11 С 1 1/40

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ .СВИДЕТЕЛЬСТВУ

ГОСУДАРСТОЕННЫЙ НОМИТЕТ

П0 ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ fHHT СССР (46) 23.09.92. Бюл. и 35 (2i) 4495389/24 (22) 17, 10.89 (72) В.И.Овчаренко (53) 681.327.66 1(088.8) (56) Электроника, 1987, Р 21, с.40-43.

Авторское свидетельство СССР

9. 1505295, кл. С 11 С 11/40, 1988.. (54) СПОСОБ ИЗГОТОИ1ЕНИЯ МАТРИЧНОГО

НАКОПИТЕЛЯ ЛЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА (57) Изобретение относится к вычислительной технике, н частности к .технологии изготовления полупроводниковых интегральных микросхем, и

Изобретение относится к вычислительной технике, в частности к техно" логии изготовления полупроводниковых интегральных микросхем, и может быть использовано для изготовления матричного накопителя электрически перепрограммируемого постоянного запоминающего устройства.

Целью изобретения является повьппение быстродействия матричного накопителя.

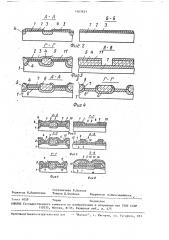

Способ иллюстрируется последовательностью операций, приведенной на фиг.1-8, где использованы следующие условные обозначения: полупроводниковая подложка 1 первого типа проводимости, слой 2 из двуокиси кремния .и слой 3 из витрина кремния, первые диффузнонни» области 4 первого типа

MoKet быть использовано для изготов- ления матричного накопителя электрически перепрограммируемого постоянного запоминающего устройства. Ц))лью изобретения является повышение быстродействия матричного накопителя.

Преимуществом матричного накопителя является наличие областей малой ширины, полученных без использования малой нормы проектирования, и обеспечение малой площади перекрытия выступа диффузионной области без использова- ния дополнительной фотолитографической операции с малыми размерами.Крсме того, уменьшены размеры ячейки памяти. 8 ил. проводимости, первый слой диэлектрика 5 из двуокиси кремния, вторая диффузионная область 6 первого типа проводимости, второй слой диэлектрика

7 из двуокиси кремния, первая группа проводящих областей 8 из поликремния, третий слой диэлектрика 9, вторая группа проводящих- областей 10 из поликремния, слой 11 фоторезиста с отверстиями, третья диффузионная ообласть 12 второго типа проводимости, четвертый слой диэлектрика 13 нз

Anchopo-силикатного стелка, третья группа проводящих областей 14,четвертая группа проводящих областей 15

-нз лоликремння.

При изготовлении матричного накопителя наносят на поверхность полупроводниковой подложки 1 первого ти16076? 1 па проводимости слои 2, 3, легируеот подложку 1 геримесью для -абра зованил первого дифАузиоггного слоя 4 23ервого типа проводимости (фиг. 2) „

Наносяе слой 5 иэ двуокиси крем5 ния 123 ПОЕ3ерхнОсть полупроводHHK023oH нодложки 1. Наносят слой 11 фоторе зиста с отверстиями.на поверхггости слоя 5 и слоя 3 из нитрида кремния, 10 проводят травление первого слоя 5 через отверстия слоя 11 до поверхности полугероводниковой подложки 1 (фиг.3) .

После удаления слоя 11 фоторезиста и слоев 2, 3 проводят легирование подложки 1 примесеыо длл образова- . ния второй диффузионной области 6 первого типа проводимости. Наносят слой 7 из двуокиси кремния на поверх- 20 ность полупроводниковой подложки 1, нанОсят леГHpol3BIIIIbIII. слОЙ 8 иэ поли кремния на поверхности 5, .7 и формируеот в нем области 8 при их травле.Нии — узкие области 15 (фиг.4,сече23ке Г-Г, гееиг.5 сечение Б-Б) .

Узкие области. 15, расположенные на боковой поверхности слоя 5 и поверхности слоя 7, образуются при реактивном ионном травлении слоя 8 за счет большей толщины этого слоя в этих местах.

Наносят третий слой 9 Iia поверхности областей 8, слоя 5 и подложки t.

На поверхность слоя 9 наносят легироиа22нь2й слой иэ поликремнпя (фиг.5„ сечгпеие Л-А, Б-Б) . OopIIIIpyior из него

-зторуео группу областей 10 и группу областей 15.

Проводлт легированне подложки

40 примесью для образования третьего дегфф"е 3HOHHoI О c3102I 12 теровОдимости (фиг . 7,; се ееегие Г -Т"), Наносят слой 13 из фосфора-силикатного стекла на поверхности обла45

creA 10, полупроводниковой подложки

1, слоя 5, формир уеот в сл Ое 1 3 отв ерстия, Наносят мегаллический слой на поверхность слоя 13 н полупроводниковой подложки 1 и формируют в нем.

50 трете:ю группу Обласгеее 14 (фе32,1,8) .

Области Я являются плавающими затвораеги эаггоминающих траееэнсторов, Области 15 — обкнадкат3 кондепсаторОВ, Др Г2232и Обкладi(QIIH — спой 12 Об"i 3(тг 10 — управеегееоеиьгее затворами эаНОМИНаЮЩИХ тРанэнетОРОГг И ЭатВОРаМИ

2 ап23есных ЕЯН rpaII aIIc ropni3 вкеего еенных п»с:3pгlоватепьно с эапоми еаюпоем33 транзисторами, слои 12, с которыми соединены области 14, являются стоками запомннаю22их транзисторов, слой

12, размещенные между областями 10, являются истоками адресных ИДП-транзисторов и обе12ей шиной матричного накопителя.

Работа матричного накопителя закхг2очается в следующем. В режиме считывания информации на выбранную адресную поликремниевую шину 10 подают низкое положительное напряжение

+5 8, на остальные адресные поликремниевые шины 10 и общую диффузионную шину 12 — нулевое напряжение. На выбранные разрядные металлические шины

14 подают низкое положительное напряжение +1 В, на остальные — нуле23ое е

Под. действием этих напряжений адресные ИДП-транзисторы выбранной строки находятся в открытом состоя".. нии, остальные адресные 1ЩП-транзисторы — в закрытом состоянии. Если пороговое напряжение выбранного запоминающего транзистора превышает (не превышает) напряжение на адресггой поликремниее2ойг шине 10, то OH находится в. закрытом (скрытом) состоянии, через . Него, открытый адр е с ный

ИДП-транзистор, разрядную металлическую нину 14, общую диффузионную шину 12 не протекает (протекает) ток, что эквивалентно нулевому (единичному) состоянию. Через остальегьге разрядные металлические шины 1.4 ток не протекает иэ-эа наличия нулевого напряжения на адресной поликремниевой шине 10 или Meталлической разрядной шине 14.

Общее одновременное стирание информации ячеек памяти i avpH;IHoro HIIкопителя осуществляется подачей высокого положительного импульсного на-., пряжения (16 В, 1-3 с) на общую диффузионную пге22еу 12 прн нулевых напряжениях на адресных поликремниевых шинах 10 и разрядньгх металлических . шинах 14.

Под действием высоких напряжений между краем диффузионной шины 12 и вьгстуееами поееикремгеиевьгх электродов.

15 (обкладками одних конденсаторов) заряд электронов через второй диэлектрический слой 7 малой тоеещины удаляется с поликремниевых 3лектродов 8, ь. результате чего IlopnrnIII!e напряжения всех запомиЕеавепех тр;Е езе3сторов

16076

30 б Я f0

Ж

73 становятся отрицательными что эквивалентно единичному состоянию.

Преимуществом матричного накопителя является наличие областей 15 малой иирины, полученных без использования малой нормы проектирования и обеспечения малой площади перекрытия выступа дифАузионной области 10 без. использования дополнительной фотоли тограАической операции с малыми размерами. Кроме этого, в накопителе уменьшены размеры ячейки памяти. Ф о р м у л а изобРетения

Способ изготовления матричного накопителя для постоянного запоминающего устройства, включающий формирование в приповерхностной области полупроводниковой подложки первого тиiia проводимости первых диффуэионйых областей первого типа проводимости, формирование первого слоя диэлектриI ка с отверстиями, расположенного на поверхности первых диффузионных обла стей, Аормирование в приповерхностной области полупроводниковой подложки.второй диффузионной области первого типа проводимости, формирование второго слоя диэлектрика, расположенного на поверхности полупроводниковой подложки, формирование проводящих областей первой группы из поликремния, расположенных на поверхностях первого и второго слоев диэлек"

21 б трика, Аормирование третьего слоя диэлектрика с отверстиями, расположенного на поверхностях первого,второго слоев диэлектрика и проводящих областей первой группы, формирование проводящих областей второй группы, расположенных на поверхности третьего слоя диэлектрика, формирование третьих диАфузионных областей второ-, го типа проводимости в приловерхност" ной области полупроводниковой подложки, Аормирование четвертого слоя диэлектрика с отверстиями, расположенного: на поверхностях третьего слоя диэлектрика и,проводящих областей .второй группы, формирование проводящих областей третьей группы, располо" женных на поверхностях полупроводниковой подложки и четвертого слоя диэлектрика, о т л и ч а ю щ и и с:.я тем, что, с целью повышения быстро" действия матричного накопителя, при формировании проводящих областей первой группы методом реактивного ионного травления формируют проводящую область, расположенную на поверхности второго слоя диэлектрика и прилегаю" щую к боковой поверхности первого;,, слоя диэлектрика, а при формировании проводящих областей второй группй формируют проводящие области четвертой .группы частичным травлением проводящей области, прилегающей к боковой .поверхности первого слоя диэлектрика.

b-6

7д

1607621

ФОГ,О

8 5 1DOa

ФуГ 8

Составитель Б.Венков

Редактор It. Каменская Техред Л,Олийнык Корректор TI.Иаксимнппи еп

3акаэ 4059 Тираж Подписное

ВЦИКИ Государственного комитета по иэобретениям и открытиям при ГКНТ СССР

113035, Москва, И-35,, Раушская наб., д. 4/5

Производственно-нэдатепьскиш ко

Г- Г б

ФШГ. 2 р р

5 4 17

I - Г

7 9 1g 7 g tt g fg

0 У

qy>< д

1б

"Патент", г, Ужгород, уя. Гагарина, 10 1