Устройство для умножения матриц

Иллюстрации

Показать всеРеферат

) 1619304

c,, = с °, i, ) = 1, п.

1 -<< Ф

Вычислительный модуль работает следующим образом. На i-м такте элемента матриц а, Ь и с подаются сппТ<«РТсТ- 5 венно на входы 7-9 и записггг«а;,;cÿ соответственно в регистры 11 — 13. При этом на выходе умножителя 15 формируется значение а b, а на выходе сумматора 16 — значение (с + а Ь), кото — 10 рсе подается на информационный вход регистра 14. Элемент сг с выхода регистра 11 подается íà i-м такте на выход 19, элемент Ъ задерживается узлом

17. задержки на (п+1) тактов и подает-15 ся на выход 19 íà (i+n+1)-м такте, а значение (с + а-Ь) подается на выход 21 на (1+1) ì такте.

Устройство работает следующим об— разом. 20

В исходном состоянии регистры 11—

14 и 17 вычислительных модулей 5, устройства устанавливаются в нулевое состояние. На входы 7-9 подаются соответственно элементы а<,(, Ь„ и 25 с в соответствующие моменты вре1) мени:

12 вычислительного модуля 5< -«,<ïèñû- вается элемент b „, в регистр 182 узла 17 задержки вычислительного модуля 5» — элемент b

На четвертом такте на вход 2 устройства подается элемент b < . При этом в вычислительном модуле 5< в регистр 12 записывается элемент Ъ,, в регистр 18< — элемент Ь„,в регистр 18> — элемент Ь22.

На пятом такте на вход 3 устройства подается элемент с()(верхний ин»2 декс в скобках указывает номер рекуррентного шага). При выполнении операции перемножения матриц А ° В элементы (О1 с(, = О, i,j = 1,п. Устройством может выполняться матричная операция

С + А В, в этом случае элементы

c6) Р О. В вычислительном модуле 5< элемент с, записывается в регистр

13, элемент Ь2< — в регистр 18», элемент Ь <2 — в регистР 182. В вычислительном модуле 52 в регистр 12 записывается элемент Ь

На шестом такте на вход 1 устройства подается элемент а«, на вход

2 устройства — элемент Ь«, на вход

3 устройства — элемент с(о). При этом в вычислительиом модуле 51 формируется значение с(; =с << + a «b „ (<) (о) которое подается на вход регистра 14.

На седьмом такте на вход 1 устройства подается элемент а<2, на вход 2 устроиства — элемент с . При этом (о) соответствующие элементы а,, Ь)< и с, записываются в соответствующие регистры вычислительных модулей 5» и 52 (фиг.5), в вычислительном модуле 52 формируется значение с() = (о)

=с, +а< Ь2<.

На восьмом .такте на вход 3 устройства подается элемент с в вы<)

2< ) числительном модуле 52 формируется значение с„= с „+ à «b« . (2) (<)

На девятом, такте на вход 1 устройства подается элемент а,, в вычислительном модуле 5 формируется значение (2) (<) с,, = с„+ а„Ь„.

1(г+1) +k+2n -?n-2, 2 — (п+1) j-nk+2n +и+1; (1) 30

2 — ni-j+2n -2п+1.

C1)

На выход 6 устройства выдаются эле- менты с; результирующей матрицы с в моменты времени 35

= ni-)+2п + 4п-3 (2)

С1)

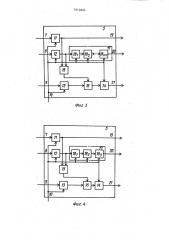

На фиг.1 показана организация подачи входного потока элементов а<<, Ь ), и с в моменты времени в сост- 40 ветствии с выражениями (1) и организация выходного потока элементов с в соответствии с выражением (2).

Рассмотрим работу устройства для. перемножения двух (2г2) матриц 45 (фиг ° 2).

На первом такте на вход 2 устройства подается элемент Ь2 (фиг.2, верхний индекс .без скобок элементов, а, b и с указывает момент пода- 50 чи элементов матриц в устройство).

При этом элемент Ь записывается в регистр 12 вычислительного модуля 5< (фиг.4 и 5).

HR BTopoM TRKTP. элемент Ь22 nocT 5 пает в узел 17 задержки вычислитель<.ого модуля 5<.

На третьем такre на вход ? устрой: тва попается элемент Ь«, в регистр

На десятом такте на вход 1 устройства подается элемент а 2, в вычислительном модуле 5 формируется значение (<) («l с 2< = с 2, + a2< Ь<».

На одиннадцатом такте в вычислительном модуле 5) формируется значе< ) (о) ние с 22 = с 22 + а2<Ь.<2

161

На двенадцатом такте в вычислительном модуле 5ч формируется значе(2) И ние с = с < + агг Ьл

На тринадцатом такте в вычислительном модуле 5 формируется значение o>z = cаг + аг " () (1)

22 cз > с = с(с выхода регистра 14 пода» > ется на выход б устройства.

На выход б устройства подаются

{c) (Я с 22

fz1 с = с соответственно на четырнадл» 21 цатом, пятнадцатом и шестнадцатом тактах.

Время перемножения двух (n n) матриц предлагаемым устройством равно (Зп + 4n-4) тактсв.

Форму л а и з о б р е т е и и я

Устройства для умножения матриц, содержащее Зг-2 (и — размер ность перемножаемых матриц) вычисли— тельных модулей, причем первый и второй информационные входы первого вычислительного модуля являются со ответственно первым и вторым инфор-! мационными входами устройства, пер— вый и второй информационные входы

i-rо вычислительного модуля

2,3п-2) подключены соответственно к первому и второму выходам (i-1) — ro вычислительного модуля, синхровхсд устройства подключен к синхровходам всех вычислительньг модулей, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, тре$3 Q4 6 тий информаци нный вход;с "poéñòíë подключен к третьему информацип.::ному входу первого вычислительного ..одуля,,» третий информационный вход х-го вь 5 числительного модуля подключен к третьему выходу (i-1)-го вьгчислител:.—

° ъ ного модуля, а третий выхоп, гi-2)го вычислительного модуля является выходом устройства.

2, Устройство но и. 1, о т л ич а ю ш е е с я тем, что каж",ыи вычислительный модуль содержит чегыре регистра, умножитечь, сумматор и узел задсржки на и+1 такт, r:pè÷åM информационные входы первого, втсрого и третьего регистров являются noorÂeòoòr.".eííÎ первьч, BTopbIN

v третьим информационны л входами

20 вычислительного модуля,, выход первого регистра подключен к первому гьгхопу вычислительного модуля и и - вом » вхсду умножителя, второй вход хozopnr о подключен к выходу вто25 :or o регистра ч информационному входу узла задержки, выход которо о является вторым выходом вычисли=ельного модуля, "ретий выход Kotopor подкл..:чен к выходу четвертогс регистра, информационный вход которогс подключен к выходу сумматора, первый и второй гходы Koòoðorо to17, ключены соответственно к выходам третьего регистра ч умножителя, синхровход вычислительного модуля подключен к синхровходам всех ре35 гистров и к синхровходу узла залерж—

KH a

1 61 9304! 6! ЧЗ(1

> . д Ч ф . .ф., 1

I ь м 1 о 4

Ф)

В 94 ьщ

1

1619304

Составитель К. Кухаренко

Техред М.Моргентал Корректор М.Самборская

Редактор И.Ъланар

Заказ 50 Тираж Подписное

ЯНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва., Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул, Гагарина, 101