Матричный накопитель для постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

союз сов тсних ссаиллистич усни х щспуьлин (51}5 G 11 С 11/ ОПИСАИИЕ ИЗОБРЕТЕ1-1ИЯ

К А ВТОРСИОМУ СВИДЕТЕЛЬСТВУ В3 РМГЛФ ФКВЧС2ЬФ Й Фч тсъ .Ф:

| °

1

jjgp

47г0

1 ОСУДАРСТВЕННЬ1Й ИОМИТ1:Т по изоБретел1иям и Отнрцтилм

Г11 и гннт сса

{46) 23.09.92. Бюл. 1. - 35 (2I} 4720211 /24 (22) 18.07.89 (71) Научно-исследонательскии институт "Восток" (72) В.И.Овчаренко (53) 681.327.66(088.8) (56) Электроника, 1980, 11 2Э, с.45.

ХЕЕЕ Journal of Solid State

jCircuits. 1988, Р 5, р.1 157-1163, (54) ИАТРИЧН11Й НАКОПИТЕЛЪ ДЛЯ ПОСТОЯННОГО ЗАПОИИНАИЩЕГО УСТРОЙСТВА (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в электрически

Изобретение относится к вычислительной технике и может быть использовано в электрически перепрограммируемом ПЗУ, сохраняющем информаци|о при отключении питания, на лавинноинжекцион33ъ|х транзисторах с плавающими и управляющими затворами, стираемых импульсным «апрлжением через конденсаторы ячеек памяти матр33чного накопителя.

Целью изобретения являетсл поня шение надежности работы накопителя.

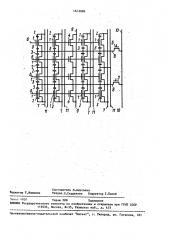

На чертеже приведена электрическая схема фрагме«та матричного накопителя.

На чертеже приняты следующие обозначения: запоминающие (лани!!но-инжекционные) транзисторы 1 с плавающими и управляющими затворами; накопительные конденсаторы 2, 3 этих ячеек памяти; транзисторы выборки 4, 5 первой и второй групп соотнетстзенио; адрес(i9l @ (и) Яя. ?Яо "«4 и ? перепрограммируемом постол«ном запоминающем устройстве «а лавинно-3шжек3|330не|ых запом33«ающнх TpafIaf|сторах с планающ33л33! и управляющими за т|зорамп.

Целью 339OGpeTeIIIIë явллетсл повышение надежности работы матрнч«ого «акопптеля. Для этого в матрич«ом ffa«onffreле длл ПЗУ подключа|от затворы выборки перной группы н строке к адрес«ой шине, Стокн транзисторон выборки пар.ной и второй групп D строке подключают к разрядной шине первой группы, стоки запоминаюи3|х транзисторон смежK Pa 3PffPíÎé шиffe 13TCPOI! группы. 1 ил. ные шины б; раэрлднъ|е шп«ы 7 перной группы шинъ| 8 1 О перноi н I opo1 и третьей групп; разрядные ш3|«ы 11 вторбй груп ъ3.

Матричный накопитель работает следуюшим образом.

В режиме счиTыванпя IIIII1iopi fafjffff f3 a ныбранную адресную шину. 6 подают ««экое положите,|н ное напряжение (5 Б}, на Остальные адрес||ые ffff|ы 6 нуле- " вое напряжение. Прп этом трапзпсторы4 перьой группы гыбранной строки «аходлтсл 33 Открытом состоя«3|н» B pe зультате чего истоки транзистороf> выбран«ой строки через открыгыс транзисторы. 4 подключены к ш«3|е вто-. рой группы (п|нне «уленого потенциала}. На шину 1О третьей группы

От источника Опор«ОгО папрлже ||на If a все истоки транзисторов 1 невыбра|п ых строк подается низкое положительное напрлженне (2-3 В) через Открытые

1642886 транэисторы " второй группы. На выб ранную разрядную шину 7 (11) подают низкое положительное напряжение (2 В), остальные разрядные шины 7 (11) от"

5 ключ ают.

Если цапряжение на выбранной адресной шине 6 превышает (ие превышает) пороговое напряжение гранэисторов l этой строки, то они находятся в открытом (эакрытом) состоянии, через них, открытые транзисторы 4 первой группы, разрядные шины 7 (11), шину 9 нулевог0 потенциала протекает (не протекает) ток, что эквивалентно единичному (нулевому) состоянию, В одном режиме общего стирания информации на все адресные шины 6 подают нулевое напряжение, все разрядные шины 7, 11 отключают. На шину

10 третьей группы подают высокое положительное импульсное напряжение (15 В, 1 с). В результате высокое положительное напвяжение через откры- . тые транзисторы Б второй группы пере- 25 дается на одни обкладки накопительных конденсаторов 3 и истоки всех тран-. зисторов 1 . На управляющие затворы транзисторов 1 и другие обкладки конденсаторов 3 передается пулевое напряжение с адресных шин 6. Под действием этих напряжений избыточный заряд электронов удаляется с плавающих затворов транзисторов 1 через накопительные конденсаторы 3, в результате

„35 чего их пороговое напряжение ста::овит" ся менее l В (до -2 В), что эквивалентно единичному состоянию в режиме считывания информации. В другом режиме общего стирания информации на 40 все адресные шины 6 и шипы 9, 10 подают нулевое напряжение. На разрядные шины 7, il первой и второй групп подают высокое положительное импульс-, ное напряжение (12 В, с). `од деи 45 ствием этих напряжений избыточный заряд электронов удаляется с плавающих затворов транзисторов 1 череэ конденсаторы 3, в, результате чего их пороговые напряжения становятся отрицательными, что эквивалентно единично50 му состоянию в режиме считывания информации.

Следует отметить, что для обеспечения блочного стирания информации в первом режиме через выбранные

55 транзисторы 5 второй группы на выбранные вины 8 подают высокое положительное импульсное напряжение, при этом остальные транзисторы 5 невЪ бранных строк находятся в закрытом состоянии. Через конденсаторы 3 выбранных строк происходит удаление избыточного заряда транзисторов 1 выбранных строк, состояния остальных транзисторов сохраняются неизменнымиь

Дпя обеспечения блочного стирания информации во втором режиме только иа выбранные разрядные шины 7, 11 подают высокое положительное импульсное напряжение, В режиме программирования информации на выбранную адресную шину 6 и через нагрузку на разрядную шину 7 (11) подают высокое положительное импульсное напряжение . (12 В, 0,1 мс), на остальные адресные шины 6 и разрядные шины 7, 11,,шину 9 нулевого потенциала подают нулевое напряжение, иа шину 10 опор ,ное напряжение (3-5 В) °

Под действием этих, напряжений че- . рез выбранные запоминающие транзисто ры 1 и транзисторы 4 первой группы той же строки;протекает ток, вызывая инжекцию горячих электронов в каналах запоминающих транзисторов 1 захват их плавающими затворами этих транзисторов. Это приводит к положитель-: ным пороговым напряжениям запоминающих транзисторов 1 (6-8 В), что эквивалентно нулевому состоянию. Состояния остальных запоминающих транзисторов 1 сохраняются неизменными из-эа отсутствия инжекции горячих электронов в их каналах и малого падення напряжения на конденсаторах ?.

Основным преимуществом предложенного матричного накопителя по отношению к прототипу является повышение его работоспособности, обеспечивающего надежную работу при отрицательных пороговых напряжениях запоминающих транзисторов после стирания информации до -3 В.

Подключение стоков эапомцнаюпцгх транзисторов столбцов соседних четных и нечетных строк к разным разрядным нинам первои и второй групп позволяет исключить влияние запоминающего транзистора соседней строки с отрицательным пороговым напряжением, так как токи протекают через разные разрядные шины 7, 1l

Подключение истоков запоминающих транзисторов 1 остальных певыбраниых строк через траиэпстсоы 5 вто5 264288б 6 рой группы к шине 10 опорного пита- : зисторы выборки первой и второй групп, ния позволяет сместить по истоку эти управляющие затворы запоминающих запоминающие транзисторы (на 2-3 В) транзисторов каждой строки, подклюпри заземленных их управляющих зат- ченные к соответствующей адресной

5 ворах, что эквивалентно подаче отри- шине, стоки запоминающих транзисторов цательного напряжения ((-2)-(-3) B)g столбца нечетных строк, подключенные на управляющие затворы и подложку к разрядной шине первой группы, обье; этих запоминающих транзисторов. В диненние стоки запоминающих транзисрезультате чего эти запоминающие трап" g .торов столбца четных строк,. истоки: зисторы находятся s закрытом состоя- запоминающих транзисторов. смежных нии при отрицательных .пороговых . . строк, подключенные к шине первой напряжениях ((-З)-(-4) В) с учетом группы, истоки транзисторов выборки обратного смещения по подложке . первой и второй групп, подключенные

15 к пйнам второй н третьей групп соотФ о р м у л а и з о. б р е т е н,и я ветственно, отличающийся тем, что, с целью повышения надежМатричный накопитель для постоян- ности работы матричного накопителя, ного запоминающего устройства, содер- затворы транзисторов выборки первой жащнй ячейки памяти, каждая из кото- R группы в строке подключены к адресрых состоит иэ:запоминающего трал- ной шине, стоки транзисторов выборки зистора и первого и второго кондак- . первой и второй групп в строке подклюсаторов, первые обкладки которых под" чены к шине. первой группы, стоки за-ключены к плавающему затвору, а вто- поминающих транзисторов смежных строк рые " соответственно к стоку и исто- 25 подключены к разрядной шине второй ку запоминающего транзисторе.тран- .группы, 1б6.288б

Составитель Л,Аиусьева

Техред Л.Сердокова Корректор Т.Палий

Редактор Т. Клвкииа

Заказ 4059 Тираж 200 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иоскэа, Ж-35р Ра)лаская иаб., gi 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101