Элемент памяти для постоянного запоминающего устройства и способ его изготовления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при изготовлении матричного накопителя для электрически перепрограммируемого постоянного запоминай ще го устройства сохраняющего информацию при отключении источника питания , на лйвинно-инжекциоиных транзисторах с плавающими и управляющими затворами, перепрограммяруемыми импульсами напряжения. Целью изобретения является увеличение количества циклов перепрограммирования. Это достигается за счет введения в элемент памяти для постоянного запоминающего устройства четвертой и пятой диффузионных областей, первой и агорой изолирующих областей. 2 с. и 2 з.По ф-лы, 7 ил.

ОЮ Ш) СОЮЗ СОВЕТСКИХ

СОЦИО ЛИСТИЧЕСИИХ

РЕСПУБЛИН.(5!)5 G 11 С 17/ОО

ГОСУДФРСТВЕНг)ЫЙ HOMHTFf

ПО ИЗОБРЕТЕНИЯМ И О!МРЫТИЩ4

flPN ГКНТ СССР (46) 23.09.92. Бюл. Р 35 (21) 4719908/24 (22) 18.07.89 (71) Научно-исследовательский институт "Восток" (72) В.И.Овчаренко н Н.ввСущева . (53) 68) .327.6(088.8) (56) Патент США ))> 4437172, кл. G )) С )7/09, опублик, 1984, Авторское свидетельство СССР

:Р 153523), кл. G 11 .С 17/ОО, 1988. (54 ). 9ЛБ); НТ m mm;,,Ц))Я nOCTOmHOrO ЗАПОИИНЛИЩЕГО УСТРОЙСТВА И СПОСОБ .КГО. ЙЗГОтоВЛЕНИЯ (57} Изобретение относится к вычислительной технике и может быть использовано при изготовлении матричного

1 Изобретение относится к вычислительной технике, в частности к технологии изготовления полупроводниковь:х интегральньгк схем, и может быть использовано для изготовлений матрич його накопителя для электрически пе- . репрограммйруемого постоянного запоминающего устройства, сохраняющего информацию при отключении источника питания, на лавинно-инжекционных транзисторах с плавающими и управляющими затворами, перепрограммируемыми . импульсами напряжения.

Цель изобре" ения — увеличение ко . личества циклов перепрограммирования: элемента памяти.

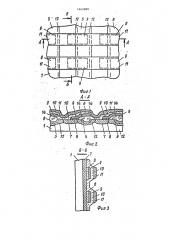

На фиг.l, 2 н 3 представлены топо логия и сечения А-A н Б-Б накопителя на элементах памяти; на фиг.4-7 последовательность выполнения опера- ций по наго-.ов 1:I! .!»it"мента памяти, т накопителя для электрически перепрограммируемого постоянного запоминаю щего устройства, сохраняющего информацию при отключении источника питания, на лавннно-инжекцнонных транзисторах с плавающими и управляющими затворами, перепрограмьжруемыми импульсами напряжения. Целью изобретения является увеличейие количества циклов перепрограммирования. Это достигается за счет введения в элекент памяти для постоянного заломи» нающего устройства четвертой и пятой диффузионных областей, первой и второй изолирующих областей. 2 с. и

2 з.п. ф-лы, 7 ия.

Злемент памяти содержит полупроводниковую подпоику 1 первого типа проводимости, слой 2 двуокиси кремния маски, слой 3 ингрида кремния маски, слой 4 фоторезиста маски, первую и вторую диффузионные области 5, первый диэлектрический слой 6, третью диффузионную область 7, второй диэлектрический спой 8., проводящую область 9, третий диэлектрический слой 10, проводящий слой 1!, четвер и пятую диффузионные области 12, первый изолирующий Слой 13, первую и. .вторую изолирующие области )4, При изготовлении элемента памяти наносят на поверхность полупроводниковой подложки 1 первого типа проводимости маску из диэлектрического слоя. 2 -двуокиси кремния, первого изолирующего слоя 13-иэ поликремния, споя 3 нитрипа кремния и слоя 4

1642888

Фотореэиста. Легируют через отверстия маски примесью с низкой концентрацией для образования диффузионных областей 12 второго типа проводимосTH (сме фнге4)е

После удаления слоя 4 маски гуано сят второй изолирующий слой из фосф0росиликатегого стекла, удаляеот с аланарной пОВерхности Второй Изолирую 1О щж| слой травлением, кроме первой и вт.арой изолирующих областей, примы- кающих к торцам маски.,Легируют примесью с Высокой концентрацией для образования первой и Второй диффузионных Областей 5 Второго типа проВодимости с частичным перекрытием краев областей 14 (см, фиг.5). Нано сят первый диэлектрический слой 6 из . двуокиси кремния локальным окнслеееием 2О. кремниевой полупроводниковой подлож ки 1., удаляют первую маску. Проводят легирование примесью с низкой концентрацией для образования третьей диффузионной облас гн 7 первого типа проводимости (см. фиг.5). Наносят второй диэлектрический слой 8 из двуокиси кремния (малой толщины) на поверхность полупроводниковой Bog» ложки 1. Наносит поликремнневую леги Зо рованную проводящую область 9 на по-верхности нервого и второго диэлектри ческих слоев 6, 8 (см. фиг.7).

Наносят третин диэлектрический слой 10 иэ двуокиси кремния на поверх- ность области 9 полупроводннковой подложки 1, на поверхность которого наносят проводящий слой 11 нэ поликрегяия.

Иатричный накопитель выполнен В АО

Виде элементов памяти, каждый из которых состоит иэ лавинно-инжекционного электрически програгемируемого запоминающег О транзистора с плавающим и управляющим затворами> Включенного по 4 следовательеео с адресным 1!ДП-транзистором, с электрически программируемым конденсатором, соединенным между . плавающим затвором.и стоком запоминающего транзистора.

Ноликремниевые области 9.являются плавающими затворами запоминающих транзисторов, слои 11 - их управляющими затворами, а Области 5, .12 — их стоками. Слои 11 также являются зат ворами адресных ИДИ"транзисторов, об ласти 5, 12 -их истоками и обклад« хами электрически программируемых конденсаторов, а другими обкладками являются поликремниевые слои области.

9, причем второй диэлектрический слой

8 малой толщины размещен между- ними, для одновременного (разрядного) стирания информации на все выбранные разрядные шешы (Области 5, 12) подают высокое положительное импульсное напряжение (12 В, 1 с}. На адресные поликремниевые,шины (слои 11) или невыбранные разрядные шины подают нулевое напряжение относительно полупроводниковой подложки 1. Под дейст-, .вием высокой напряженности электричес-. кого поля во втором днэлектрическом слое 8 электроны инжектируются с ниж- ней поверхности поееикремнневых областей 9, туннелируют через Второй диэлектрический слой 8 и удаляются через Обхеасти 5, 12„ В результате .это го пороговые напряжения запоминающих транзисторов становятся отрицательными, что эквивалентно единичному про водящему состоянию в режиме считыва» ния информации.

3 режиме программирования информа" дни на Выбранную адресную поликремпиевую шину и выбранные разрядные диффузионные шины подают высокое положительное импульсное напряжение (12 В, 1 мс), На соседние разрядные диффузионные шины и остальные адресные шины подают нулевое напряжение, на остальные разрядные диффузнонные - . вппеье — низкое положительное напряжение. При протеканееи тока через открытые Выбранные запоминающие транзисторы и адресные ИДП-транзисторы 3G счет высокой напряженности стокового электрического поля выбранных запомиееаеощих транзисторов "горячие" электроны инжектируются из каналов этих. транзисторов, захватываются поликремниевыми областями 9, что приводит к увеличени)о их пороговых напряжений..

Это эквивалентно нулевому непроводящему состоянию в режиме считывания информации, /

Состоянии остальных невыбранных запоминающих транзисторов сохраняются неизменными из-за нулевого наприженил на адресных поликремниевых ше нах или низкого напряжения на разрядных диффузионных шинах,. в результате чего отсутствует инжекции "горячих". электронов в нх каналах.

3 режиме считывания информации на; адресные поликремниевые шины и разрядные диффузионные шины подают бо5 1642988

6 лее низкое (5 В) напряжение относительно полупроводниковой подложки

1, чем при программировании инфориациие

Через выбранные запоминающие транзисторы ток не протекает (протекает), если они находятся в нулевом (единичном) состоянии. Через невыбранные запоминающие транзисторы ток не протекает.

Формула изобретения

1.Элемент памяти для постоянного запоминающего устройства, содержащий полупроводниковую подложку первого типа .проводимости, первую и вторую диффузионные области второго типа проводимости, расположенные в при- 20 поверхностном слое полупроводниковой подложки, первый диэлектрический слой, расположенный на поверхности полупроводниковой подложки над первой и второй диффузионными областями, 25 третью диффузионную область первого типа проводимости, расположенную в приповерхностном слое полупроводниковой подложки между первой и второй диффузионными областями, второй диэлектрический слой, расположенный на поверхности .полупроводниковой подложки над третьей диффузионной областью, проводящую область, расположенную на поверхностях первого

35 и второго диэлектрических слоев, тре тий диэлектрический слой, расположенный,на поверхности полупроводниковой подложки над третьей диффузионной областью и поверхности проводящей

40 области, проводящий слой, расположенный на поверхности третьего диэлектри» ческого слоя, отличающийся тем, что, с целью увеличения количе-. ства циклов перепрограммирования эле- 45 мента памяти, он содержит четвертую и пятую диффузионные области второго типа проводимости, расположенные в . приповерхностном слое полупроводни- ковой подложки между первой и третьей 5Q диффузионными областями и второй и третьей диффузионными областями соответственно с примыканием к их краям первую изолирующую область, расположенную на поверхности полупроводнико 55 вой подложки над первой и четвертой диффузионными областями с примыканием к краям первого и второго диэлектрических слоев, вторую изолирующую об ласть, расположенную на поверхности полупроводниковой подложки над второй и пятой диффузионными областями с при" мыканием к краям первого и третьего диэлектрических слоев, при этом вто» рой диэлектрический спой расположен с перекрытием края четвертой диффуэиционной области, а проводящая область" йа поверхности первой изолирующай области.

2.Элемент памяти по п,1, о т л и - ч а ю шийся тем, что первая и вторая изолирующие области выполнены из поликремния, фосфоросиликатного стекла, боросиликатного стекла или азотнозакисного окисла. 1

3.Способ изготовления элемента памяти. для постоянного запоминающего устройства, включающий последовательное нанесение на поверхность полупроводниковой подложки слоев двуокиси кремния, нитрида кремния, фоторезис- та, образующих маску, удаление слоя фоторезиста маски, формирование первой и второй диффузионных областей селективным легнрованием по маске, формирование., первого диэлектрического слоя селективным окислением по маске, последовательное удаление слоев нитрида кремния и двуокиси кремния маски, формирование третьей дйффузнонной области, нанесение второго диэлектрического слоя, проводящей области из легированного полнкремния, третьего диэлектрического слоя, проводящего слоя иэ легированного поликремния, о т л и ч а ю m и и с я . тем, что после нанесения слоя двуокиси кремния маски на него наносят первый изолирующий слой, перед формированием первой и второй диффузионных областей формируют четвертую и пятую диффуэион" ные области легированием по маске, удаляют слой фоторезиста маски, наносят второй изолирующий слой, формируют из него первую и вторую изолирующие области, а перед удалением слоя двуокиси кремния маски удаляют цервый изолирующий слой маски.

4,Способ по п,3; о т л н ч а ющ и Й с я т@й, что первый изолирующий слой Выполнен вз поликремння, фосфоросиликвтяаго стекла, боросиликатного стекпв иая азотнозакисного окисла. ! 642838

1642888 фри Я

° . б 14 14 6 14 М 6

Составитель С.Королев

Техред Л.Сердюкова Корректор T.éàëèé

Редактор Н.Федорова

Заказ, 4059 Тираж 198 Подписное

ВНИИЦИ Государственного комитета по изобретениям и открытиям йри ГКНТ СССР

113035, Иосква, Ж-35, Раушская иаб, p,a 4/5

Производственно-издательский комбинат "Натеит", г, Ужгород, ул. Гагарина, 161