Оперативное запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам со встречной коррекцией ошибок, и мохет быть использовано прл создании интегральных схем. Целью изобретения является расширение функциональных возможностей устройства за счет контроля состояния накопителя в процессе эксплуатации. Устройство содержит накопитель, формирователь контрольных разрядов, формирователь синдрома, дешифратор, блок управляемых инверторов , первый, второй и третий мультиплексоры , элемент ИЛИ, триггер и формирователь импульса. Цель изобретения достигается тем, что в процессе эксплуатации сигнал ошибки, формируемый элементом ИЛИ по ненулевому синдрому, фиксируется в триггере . В режиме тестирования состояние триггера через второй и третий мультиплексоры выводится на информационные выходы для анализа. 1 ил.

сааз сОВетских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я>s G 11 С 29/00

ГОСУДАРСТВЕННЫ Я КОМИТЕТ

Г!О ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4609607/24 (22) 24.11.88 (46) 23,04.91. Бюл. М 15 (72) В.B.Áaðàíîâ, A.Ñ.Áåðåsèí, А.Д,Кузьмин, В.В.Маринчук, П,Б.Поплевин и С.В.Сушко (53) 681;327т.6 (088.8) (56) Патент США М4335459,,кл, 37 I/38, 1982.

Патент США ¹ 4561095, кл. 371/38, 1985, (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСтРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК (57) Изобретение относигся к области вычислительной техники, в частности к запоминающим устройствам со встречной коррекцией ошибок, и может быть использовано при создании интегральных схем, Изобретение относится к вычислительной технике, в частности к запоминающим устройствам со встроенной коррекцией ошибок, и может быть использовано при создании интегральных схем.

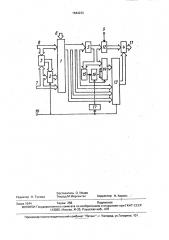

Цель изобретения — расширение функциональных возможностей устройства за счет контроля состояния накопителя в процессе эксплуатации, На чертеже представлена структурная схема оперативного запоминающего устройства с коррекцией ошибок.

Устройство содержит накопитель 1, первый мультиплексор 2, формирователь 3 контрольных разрядов, блок 4 управляемых инвертороа, формирователь 5 синдрома, входы 6 управления накопителем, информационные входы первой 7 и второй 8 групп, „„ Ы„„1644233 Al

Целью изобретения является расширение функциональных возможностей устройства эа счет контроля состояния накопителя в процессе эксплуатации. Устройство содержит накопитель, формирователь контрольных разрядов, формирователь синдрома, дешифратор, блок управляемых инверторов, первый; второй и третий мультиплексоры, элемент ИЛИ, триггер и формирователь импульса. Цель изобретения достигается тем, что в процессе эксплуатации сигнал ошибки, формируемый элементом ИЛИ по ненулевому синдрому, фиксируется в триггере. В режиме тестирования состояние триггера через второй и третий мультиплексоры выводится на информационные выходы для анализа. 1 ил, первый 9 и второй 10 управляющие входы, а информационные выходы 11, дешифратор Q

12, второй 13 и третий 14 мультиплексоры, р элемент ИЛИ 15, триггер 16 и формирователь 17 импульса.

Устройство работает следующим образом.

Ы

Пусть число информационных разрядов (д в записываемом в накопитель 1 слове данных равно восьмн. Следовательно, нрн нспользовании кода Хэмминга число контрольных разрядов, формируемых блоком 3, равно четырем. Тогда шины входных информационных разрядов произвольно разбиваются на две группы 7 и 8, содержащие по четыре шины.

В основном рабочем режиме, при котором на управляющих входах 9 и 10 поддер1644233 живаются, положим, сигналы уровней "1" и

"О" соответственно, мультиплексор 2 пропускает на входы контрольных разрядов накопителя 1 сигналы с выходов формирователя

3 контрольных разрядов, второй мультиплексор 13 — сигнал с выходов информационных разрядов накопителя, а дешифратор

12 осуществляет расшифровку кода синдрома для последующего исправления ошибок в блоке 4 управляемых инверторов.

В тестовых режимах осуществляется проверка работоспособности ЭП накопителя 1 хранения информационных и контрольныхх разрядов слов данных. При этом при поддержании в режиме записи на входе 10 сигнала уровней соответственно "1" или "О" осуществляется запись в ЭП накопителя 1 хранения контрольных разрядов либо с информационных входов 7 первой группы, либо с выходов схемы формирователя контрольных разрядов. Запись информации с входов 7 необходима для прямой проверки работоспособности ЭП контрольных разрядов, В тестовых режимах считывания сигналом входа 9 уровня логического "О" может быть запрещено инвертирование блоком 4 выходных сигналов второго мультиплексора 13, т.е. запрещается коррекция ошибок.

Это необходимо для осуществления собст.венно прямой проверки работоспособности всего накопителя 1. В таком цикле проверки . при поддержании на входе 10 сигнала низкого уровня на выходы 11 через второй мультиплексор 13 сигналы поступают непосредственно с выходов информационных разрядов накопителя 1 (первые две группы входов второго мультиплексора 13), а при установке его равным единице на выходы 11 поступают 4-разрядный код с выходов контрольных разрядов накопителя 1 (третья группа входов второго мультиплексора 13) и

4-разрядный код с выходов третьего мультиплексора 14 (четвертая группа входов второго мультиплексора,13).

Рассмотрим более подробно сигналы, формируемые на выходах третьего мультиплексора 14.

Поскольку в режиме проверки ЭП информационных разрядов накопителя 1 на входы мультиплексора 13 поступает 8-разрядный код, а при проверке ЭП контрольных разрядов — 4-разрядный код, то оставшиеся четыре входа мультиплексора

33 могут быть использованы для вывода полезной для разработчика (пользователя) информации. Такой информацией является, например, 4-разрядный код синдрома, формируемый схемой 5. На этапе тестирования

ОЗУ анализ кодов синдрома позволяет сде15

55 лать вывод с работоспособности схем коррекции сшибок, а при обычной эксплуатации ОЗУ вЂ” о наличии ошибки в считываемом из накопителя слове, Для осуществления контроля за состоянием накопителя и за условиями эксплуатации устройства в состав OBY введен также элемент ИЛИ 15 и триггер 16. Если при считывании слова из накопителя 1 в нем схемой 5 формирования синдрома обнаружена ошибка (ненулевой код синдрома), на выходе элемента ИЛИ 15 будет сформирован сигнал логической "1",;ггер 16 переключится в состояние "1". Такое состояние триггер 16 будет сохранять до момента вывода информации о нем íà выходы 11 устройства. Для этсгс на вход 10 поступает сигнал высоко с уровня, переключающий мультиплексор 13 на вывод информации с выходов мультиплексора 14.

Если на этапе подобной проверки на выходе элемента ИЛИ 15 установлен сигнал уровня логического "О" (т.е„в данный момент из накопителя 1 считывается слово, не содержащее ошибок), то на соответствующие выходы третьего мультиплексора 14 сигналы поступают с выхода трипера 16 ошибки, При этсм, если триггер 16 находится в нулевом состоянии (т.e., с момента предшествующей проверки не были зарегистрированы ошибки в считаннь х словах данных), íà Bbl" ход мультиплексора 14 поступает код ОООО.

Таким образом, наличие кода ОООО на выходах мультиплексора 14 указывает на то, что как на этапе предшествующей г,роверки, так и при данном конкретном обращении к накопителю i ошибки не были зарегистрированы.

Если триггер 16 установлен в состсяние логической "1" (т.е., за время, прошедшее с момента скончания предыдущей проверки, в считанны:;- из накопителя словах была обнаружена пс крайней мере одна ошибка), на выходы мультиплексора 16 поступает код

1111. При этом кодирующая матрица формирования контрольных разрядов всегда может быть выбрана для кода Хэмминга (12,8) такой, что при однократных ошибках код синдрома никогда не будет равен 1111.

Поэтому, если на этапе рассматриваемой проверки на Выходах 11 устройства присутствует подобный код, это однозначно указывает на отсутствие ошибки в выводимом иэ накопителя слове в данный момент и на регистрацию ошибки (или ошибок) на предшествующем этапе проверки.

Если при такой проверке на выходе элемента ИЛИ 15 появляется сигнал логической "1", следовательно, в сч .. таннсм йэ накопителя 1 слове зарегистрирована

1644233 ошибка, и на выходы мультиплексора 14 поступают сигналы кода синдрома (вывод сигнала о состоянии триггера 16 в таком слyчaе не будет сообщать какую-либо дополнительную полезную информацию, поскольку этим же сигналом уровня "1" элемента ИЛИ

15 триггер 16 будет установлен в состояние логической "1").

Установка тригг .ра 16 ошибки происходит сигналом схемы ИЛИ 15 (в начале paGoты устройства он установлен в состояние логического "0"), а сброс осуществляется в конце каждого этапа проверки с помощью сигнала формирователя 17, который выделяет импульс требуемой длительности при поступлении фронта спада сигнала на управляющем входе 10 (такая проверка может занимать как один, -ак и несколько циклов обращения к накопителю 1).

Формула изобретения

Оперативное запоминающее устройство с коррекцией ошибок, содержащее

-накопитель, первый мультиплексор, формирователь контрольных разрядов, формирователь синдрома, блок управляемых инверторов, причем входы информационных разрядов первой и второй групп накопителя являются информационными входами устройства и соединены с вхоцами

- формирователя контрольных разрядов, адресные и управляющие входы накопителя являются одноименными входами устройства, а выходы информационных и контрольных разрядов подключены к входам формирователя синдрома, выходы блока управляемых инверторов являются информационными выходами устройства, о т л и ч аю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет контроля состояния накопителя в процессе эксплуатации, в устройс1во введены второй и третий мультиплексоры, дешифратоо, элемент ИЛИ, триггер и формирователь импульса, причем информа5 ционные входы г.ервой и второй групп первого мультиплексора соединены соответственно с выходами формирователя контрольных разрядов и с информационными входами второй группы накопителя, вхо10 ды контрольных разрядов которого подключены к выхоДам второго мультиплексора, выходы формирователя синхрома соединены с входами элемента ИЛИ, с информационными входами первой группы

15 втооого мультплексора и с информационными входами дешифратора, управляющий вход которого чвляетсч пьрвым управляющим входом устройства, а выходы подклюцены к первым входам блока управляемых

20 инверторов, вторые входы которого соединены с выходами второго мультиплексора, информационные входы первой группы которого подключены K выходам информационных разря,ов накопителя, одни

25 информационные входы второй группы второго мультиплексора соединены с выходами третьего мультиплексора, другие информационные входы второй группы подключены к выходам контрольных разрядов

30 накопителя, а управляющий вход второго. мультиплексора является вторым управляющим входом устройства и соединен с управляющим входам первого мультиплексора и с входом формирователя импульсов, выход

35 которого подключен к синхровходу триггера, информационный вход которого подкл ючен к выходу элемента ИЛИ и к управляющему входу третьего мультиплексора, информационные входы второй груп40 пы которого соединены с выходом триггера.

Составитель О, Исаев

Техред M,Моргентал

Корректор Н, Король

Редактор Н. Тупица

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 1244 Тираж 356 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5