Элемент памяти для постоянного запоминающего устройства и способ его изготовления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к технологии изготовления полупроводниковых интегральных схем, и может быть использовано для изготовления матриц - кого накопителя длл электрически перепрограммируемого ПЗУ, сохраняющего информацию при отключении источника питания, на лавинно-ннжекционных транзисторах с плавающими и управляю-- щими затворами, перепрограммируемых импульсными напряжениями. Целью изобретения является увеличение количества циклов перепрограммирования элемента памяти. Поставленная цель достигается легированием примесью с высокой концентрацией до образования первой и второй диффузионных областей второго типа проводимости под углом к поверхности полупроводниковой подложки и в плоскости, перпендикуляр- . пой продольным отверстиям в маске, после чего проводят легирование примесью с низкой концентрацией через отверстия маски до образования чет- . вертой и пятой диффузионных областей второго типа проводимости. 5 ил. (Л С

ССЮОЭ СОЕЕТСНИХ

РЕСПУБЛИК (51)5 С 11 С 17/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

llPH ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИ „," * " и >

К д 8ТОРСИОМУ СВИДЕТЕЛЬСТВУ (46) 23.09.92. Пюл. Р 35 (2 1) 4752756/24 (22) 30.08.89 (71) Научно-исследовательский институт "Восток" (72) В.И.Овчаренко (53) 681.327 ° 66(088.8) (56) Патент ЕПВ.Р 0286121, кл. С 11 С 17/00, 1988.

Авторское св1гдетельство СССР

Ф 1535231, кл. С 11 С 17/00, 1988. (54) 3JIENE)lT KQ15lTH .JUIfl ПОСТОЯННОГО

ЗАПОКИНЛИИЕГО УСТРОЙСТВА И СПОСОБ

ЕГО ИЗГОТОВЛЕНИЯ (57) Изобретение относится к вычислительной технике, в частности к технологии изготовления полупроводниковых интегральных схем, и может быть использовано для изготовления матрич" ного накопителя для электрически перепрограммируемого ПЗУ, сохраняюИзобретение относится к вычислительной технике, в частности к технологии изготовления полупроводнико" вых интегральных схем, и может быть использовано для изготовления матрич« ного накопителя для электрически пе" репраммируемого постоянного запогагнающего устройства, сохраняющего ипформацию при отключении нсточника питания, на лавинно-инжекционных транзисторах с плавающиии и управ"ляющими затворагаг, перепрограммируемых импульсами напряжения.

Цель изобретения - увеличение количества циклов перепрограммирования элемента памяти.

„„SU„„1655242 А 1 щего информацию при отключении источника питания, на лавинно-инжекционных транзисторах с плавающими и управляю-. щими затворами, перепрограммируемых импульсными напряжениями. Целью изобретения является увеличение количества циклов перепрограммирования эле-— мента памяти. Поставленная цель достигается легированием примесью с высокой концентрацией до образования первой и второй диффузионных областей второго типа. проводимости под углом к поверхности полупроводниковой подложки и в плоскости, перпендикулярной продольным отверстиям в маске, после чего проводят легирование при- g месью с низкой концентрацией через отверстия маски до образования четвертой и пятой диффуэионных областей второго типа проводимости. 5 ил.

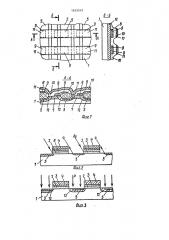

На фиг. 1 представлены топология и разрезы структуры элемента памяти, на фиг.2-5 - разрезы структуры элемента памяти на различных стадиях его изготовления.

Элемент памяти содержит полупро водниковую подложку 1, слой 2 из двуокиси кремния маски, слой 3 из нитрнда кремния масли, слой 4 фоторезиста маски, первую и вторую диффузионные области 5 второго типа проводимости с высокой концентрацией примеси (разрядные диффузионные анны), первый диэлектрический слой 6 из двуокиси кремния, третью диффузионную область 7 первого типа

1655242 проводимости с низкой концентрацией примеси, второй диэлектрический слой

8 из ДВуОкиси кремния проводящую область 9 из легированного паликрем5 ния, третий диэлектрический слой 10 из двуокиси кремния, проводящ гй слой

11 из легированного поликремггия, четвертую и пятую диффузионные области

12 второго типа проводггмости с низкой 10 концентрацггей примеси.

Элемент памяти состоит hs лавин но-инжекцнонного электрически программируемого запоминающего транзистора с плавающим и управляющим эатво- 15 рани, включеггного последовательно с адресным MjgI-транзистором, с электрически программируемым конденсатором, включенным между ггланагощим затвором и стоком запомиггающего тран- 20 зистора.

Поликремниевые области 9 являются плавающими затворами запоминающих транзисторов, поликремниевые слои Il « их управляющими затворами, разрядньа 25 диффузионные шины - их стоками . Лд» ресные полнкремниевые шины также являются затворами адресных ИДП-транзисторов, разрядные диффузионные шины « их истоками и Обкладками З0 электрически программируемых кондейсаторов.

Работа матричного накопителя иа элементах памяти заключается в сле- дующем. Для одновременного (разрядного) стирания информации на все выбранные разрядные шины подают высокое положительное импульсное на» пряжение (12 В, 1 с). На адресные . преиевые шаны или невыбра н е 40 разрядные шины подают нулевое напряжение относительно полупроводниковой подлоаки 1.

Под действием высокой напряженности ВО 45 диэлектрическом слое 8 электроны инжектируются с нижней поверхности поликремниевых областей 9, туннелируют через второй диэлектрический слой 8 и удаляются через разрядные диффузионные шины. В результате этого пороговые напряжения эапоми»

Вающих траг1зисторов становятся отрицательными, что эквивалентно единично .му» проводящему, состояггггю s режиме считывания информации, В режиМЕ программирования иггфоО-; нации на выбранную адресную поликрем« ггиевую шину и выбранные разрялггые диффузионные шины подают высокое положительное импульсное напряжение (12 В, 1 мс), на соседние разрядные диффузионные шггггы, Остальные адресные шины подают нулевое напряжение, на остальггые разрядггые дггффузиоггные шиныниэкое положительное ггаггряжеггие.

При протекании тока через открытие выбранные запоминающие транзисторы и адресные ИДП-транзисторы за счет высокой напряженности стокового электрического поля выбранггых запоминаю щнх транзисторов "горячие" электроны инжектируются из каналов этих транзисторов, захвятьгваются полнкремниевыыи областями, чТО приводит к повьппению их пороговых напряжений. Это эквивалентно нулевому непроводящему состоянию в режнгге считывания информации.

Состояния остальных невыбранных запоминающих транзисторов сохраняются неиэыеггггыми иэ-эа нулеВого напря» жения гга адресных поликремниевых плгпах илп низкого напряжения на разрядных диффузионных шинах, в результате чего Отсутствует инжекция "горячих" электронов в их каналах.

В режиме считывания информации на . адресные поликремниевые шины и разрядные диффузионные гпнны подают более низкое (5 В) напряжение относи» тельно полупроводниковой подложки 1 чем при программироваггии нггформаций.

Через выбранные запоминающие траиэисторы ток не протекает (протекает), если они находятся в нулевом (единичном) состоянии. Через невыбранные запоминающие транзисторы ток не протекает.

При изготовлении элемента памяти на поверхность полупроводниковой подлозли 1 первого типа проводииостгг наносят маску из диэлектрическо

ro слоя 2 из двуокиси кремния, диэлектрического слоя 3 из иитрида крем-" . ния, слоя 4 фоторезиста.

Легируют примесью с высокой кбн" центрацпей под углом к поверхности полупроводниковой подложки и и плоскости, ерпеггдикулярггой продольным .

Отверстиям В маске, до Образования первой и Второй диффузионных обла- стей 5 второго типа проводимости, цИзрядных диффуэионггьвшин,удаленных . от первых краев йаски (фнг.2). После

165 этого легируют примесью с низкой 1,онцентрлцией через отверстия маски ло образования четвертой и пятой диффузионных областей 12 второго типл пронодимости (фиг, f).

После удаления слоя 4 фоторезистл маски наносят перный диэлектрический слой 6 иэ двуокиси кремния локальным окислением кремниевой полупроволниконой подложки 1, удаляют маску. Проводят легировлние прииесью с низкой концентрацией до обрлзонания третьей диффузионной области 7 первого типа проводимости (фиг,4) °

На понерхность полупроводниковой подложки 1 наносят второй диэлектрический слой 8 из двуокиси кремния иллой толщины. Нл поверхности первого и второго диэлектрических слоев 6, 8 наносят первый поликреиниеньв1 легированный слой 9, Формируют в неи поликремниевые шины (фиг.5), На поверхности поликреиниевых шин, полупроводниковой подложки 1 плносят третий диэлектрический слой 10 иэ двуокиси кремния, ил поверхность которого наносят второй легированный слой 11 иэ поликреиния, формируют в пем адресные поликреиниевые шины, торцы в диэлектрическом слое 8 и иэ поликреиниевых шин — поликремниевые элекТроды, совмещенные с краяии адресных поликреиниевых шин (фиг.1).

5242

f5

l0

Формула изобретения

1. Элемент плмяти для постоянного запоминающего устройства, содержащий полупроводниковую подложку первого тина проводимости, первую и вторую диффузионные области второго типа проводимости, расположенные в приповерхностном слое подложки, верный диэлектрический слой, расположенный на поверхности подложки над первой

H второй диффузионными областями, третью диффузионную область первого типа проводимости, расположенную в приповерхностном слое подлоши| между первой и второй диффузионными областями, второй диэлектрический слой, расположенный на поверхности подложки нлл третьей диффузионной областью, проводящую обллсть, расположенную на поверхности первого и нторого диэлектрических слоев, третий диэлектрический слой, расположенный нл поверхности подложки нлд третьей диффузионной областью и на поверхности проводящей области, проводящий слой, расположенный на поверхности треть""ão диэлектрического слоя, о т л и ч л ю шийся тем, что, с целью увеличения количества циклов перепрогрлмииронайия элемента памяти, ои содержит четвертую и пятую диффузионные обл",ñòf второго типа проводимости, расположенные и припонерхностном слое полупроводниковой подложки между первой и третьей и между второй и третьей диффузионными областяии соответственно с примыклнием к их крали, в диэлектрический слой расположен нл поверхности четвертой и пятой диффузионных областей, первый диэлектрическ п слой расположен с перекрытием краев первой и второй диффузионных областей.

2. Способ изготовления элемента памяти для постоянного запоминающего устройства, включающий последовательное нанесение нл поверхность полупроводниковой подложки слоев двуокиси кремния, нитрида кремния, фоторезиста, образующих маску, формирование первой и второй диффузионных областей селектинным легиронлниеи по млске, удаление слоя фотореэиста маски, формирование первого диэлектрического слоя селектинным окислением по маске, последовательное удаление слоев нитрида кремния и двуокиси кремния маски, формирование третьей диффузионной области, нанесение второго диэлектрического слоя, формирование проводящей области иэ легированного поликремния, отличающийся тем, что, что при формировании первой и второй диффузионных областей пеги" рование проводят под углом к поверхности полупроводниковой подложки, а затеи фориируют четнертую к пятую диффузионные области селективым легнрованием по иаске.

1655242

5 127

12! 655242 ц З 12S

Фиг,5

Составитель Л.Аиусье а

Текред Л,0лиднык Корректор Л.Патаи

Уедактор В.Федотов

Закаэ 4060 Тираа Подписное

ЙЯИИПИ Государственного ковеютета по изобретениям и открмтияи при ГЕНТ СССР

113035, Москва, И-35, Рауаская наб., д. 4/5

Йроиаводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, f01