Способ контроля ттл итегральных схем

Иллюстрации

Показать всеРеферат

Изобретение относится к контролю интегральных схем и может быть использовано для отбраковки дефектных ТТЛ интегральных схем. Цель изобретения - повышение достоверности контроля за счет выявления утечек и объемных дефектов в области эмиттерного перехода транзисторов ТТЛ интегральной схемы. Способ состоит в следующем. На вход контролируемой ТТЛ интегральной схемы задают номинальное входное напряжение UBX и текущие значения Ucc(l) напряжения питания в соответствии с формулой UCc(0 UCCH -i AUcc. где (i) 0- n; UCCH - номинальное значение напряжения питания; Д Dec - шаг уменьшения напряжения питания, уменьшают входное напряжение UBx от номинального значения до значения, при котором напряжение логической 1 на выходе контролируемой ТТЛ интегральной схемы принимает минимально допустимое значение, измеряют текущие значения напряжения логической 1 UHn(l) на выходе контролируемой ТТЛ интегральной схемы, соответствующие заданному значению Ucc(i), определяют значения приращений этого напряжения по формуле А Онп(0 I Umi(l + 1) - -йнпО), сравнивают текущие значения АУнпО 1 п) с эталонным значением UHn(l 0), в случае Д UHn 0 1,... п) Д U Hn(i 0) измеряют значение напряжения Uccnop питания контролируемой ТТЛ интегральной схемы и при UCCH - Uccnop A (A - заданная величина) считают контролируемую ТТЛ интегральной схемы негодной по объемным дефектам эмиттерного перехода, а при UCCH - Uccnop В (В - заданная величина) - негодной по утечкам коллекторного и эмиттерного переходов. Обнаружение объемных дефектов и утечек эмиттерного перехода транзисторов ТТЛ интегральной схемы повышает достоверность контроля,2 ил. (Л С а vi ел 00 2

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 6 01 R 31/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4744411/21 (22) 02.10.89 (46) 07.09.91. Бюл. М 33 (72) С.С.Кураченко, В,В.Воинов и В.В.Макеев (53) 621,317.799 (088.8) (56) Авторское свидетельство СССР

N 1056088, кл. G 01 R 31/26, 1983.

Репкин В.Ф. Основы надежности и эксплуатации радиоэлектронных схем. — Киев:

КВИРТУ, 1975, с. 220-222. (54) СПОСОБ КОНТРОЛЯ ТТЛ ИНТЕГРАЛЬНЫХ СХЕМ (57) Изобретение относится к контролю интегральных схем и может быть использовано для отбраковки дефектных ТТЛ интегральных схем. Цель изобретения — повышение достоверности контроля за счет выявления утечек и объемных дефектов в области эмиттерного перехода транзисторов TTJI интегральной схемы. Способ состоит в следующем. На вход контролируемой

ТТЛ интегральной схемы задают номинальное входное напряжение U>< и текущие значения U«(l) нап ряжения питания в соответствии с формулой Ucc(i) = 0ссн—

-1 Л0сс, где (l) = 0 —; Осси — номинальное

Изобретение относится к контролю интегральных схем и может быть использовано для отбраковки . дефектных ТТЛ интегральных схем (ИС).

Цель изобретения — повышение достоверности контроля путем выявления утечек и объемных дефектов в области эмиттерного перехода транзисторов ТТЛ интегральной схемы.

„„5U„„1675804 А1 значение напряжения питания; ЛОсс — шаг уменьшения напряжения питания. уменьшают входное напряжение 0 от номинального значения до значения, при котором напряжение логической "1" на выходе контролируемой ТТЛ интегральной схемы принимает минимально допустимое значение, измеряют текущие значения напряжения логической ".1" Uen(l) на выходе контролируемой ТТЛ интегральной схемы, соответствующие заданному значению Ucc(i), определяют значения приращений этого напряжения по формуле Л U«(i) =(Онп(1 + 1)—

-Uqo(l) I, сравнивают текущие значения

Лu«(l = 1„... n) с эталонным значением

U«(i=0), в случае AU«(i=1,...,п) < Л Онф=

= О) измеряют значение напряжения U««p питания контролируемой ТТЛ интегральной схемы и при 0ссн Uccnop > А (А — заданная величина) считают контролируемую ТТЛ интегральной схемы негодной по обьемным дефектам эмиттерного перехода, а при 0ссн—

Uccnop < В ( — заданная величина) — негодной по утечкам коллекторного и эмиттерного переходов. Обнаружение объемных дефектов и утечек эмиттерного перехода транзисторов ТТЛ интегральной схемы повышает достоверность контроля. 2 ил.

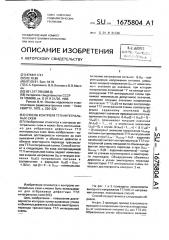

На фиг, 1 и 2 приведены зависимости ъ выходного напряжения ТТЛ ИС от напряжения питания, поясняющие способ.

Способ осуществляется следующим образом.

На фиг. 2 приведен пример зависимости выходного напряжения логической единицы

0л от напряжения питания Ucc для ТТЛ ИС.

Образование утечек обусловлено явления167 ми на поверхности р — n-переходов и особенно существенно сказывается на работе обратносмещенных коллекторных переходов, При снижении напряжения питания сопротивление коллектора должно уменьшаться. Однако наличие утечек приводит к тому, что сопротивление коллектора при снижении напряжения питания может даже увеличиваться. Результатом этого является аномальная зависимость выходного напряжения логической единицы от величины напряжения питания. Аномалия г1роявляется в виде более быстрого. по сравнению с бездефектной ИС, снижения выходного напряжения логической единицы при снижении напряжения питания (фиг. 1).

Вместе с тем утечки, локализованные в области эмиттерного перехода из-за его мал6го сопротивления и достаточно высокого переходного сопротивления утечки, аналиэрм зависимостей (фиг. 1) могут быть обнаружены в крайних редких случаях. Кроме тОго, следует учитывать, что для прямосмещенных р — п-переходов существенную роль играют объемные дефекты, которые обусловлены переходом атома легирующей приМеси из узла кристаллической решетки в междоузлие. Объемные дефекты развиваются из точечных и образуют области с повышенным удельным сопротивлением. В результате этого в прямосмещенном р — ппереходе образуются каналы проводимости со значительной величиной плотности тока в них. Это приводит к локальному разогреву решетки и стимулирует процесс ионизации.

Результатом является катастрофический отказ прибора.

Эти дефекты также не обнаруживаются анализом зависимостей (фиг, 1). Причиной этого является то, что измерения производятся при достаточно низком (порядка де,RTKoB ом) сопротивление эмиттерного перехода, Повышение достоверности отбраковки достигается повышением информативности режима измерения выходного параметра

ПЛ ИС, в частности напряжения логиче:кой единицы. Для решения этой задачи выбирают такой режим измерения, при котором сопротивление змиттерного перехода становится соизмеримым с переходными

".oïðîòèâëåíèÿìè утечки в области объемных дефектов. Поэтому после подачи на ТТЛ

ИС номинального напряжения питания U« и номинального входного воздействия Usx, дающего на выходе ИС напряжение логической "1", уменьшают величину входного воздействия О х до тех пор, пока выходное

5804 4 напряжение логической "1" не достигает минимального значения допускаемого техническими условиями 0«н, При этом токи через эмиттерные переходы транзисторов

5 ИС минимальны, а их сопротивления максимальны. Постепенно с шагом ЛОСС снижают напряжение питания, Выбор шага Л U«обусловлен следую10 щими требованиями. Требуется минимальное значение шага для обнаружения сколь угодно малых аномалий и существуют естественная погрешность измерений напряжений измерительной установки и

15 естественно малая (до 0,0005 В) неравномерность хода зависимости U - f(Ucc) — выходного напряжеНия логической "1" от напряжения питания. Поэтому шаг снижения напряжения питания выбирается по

20 крайней мере в 2 раза больше погрешности . измерительной установки, Реальные погрешности блоков функционального контроля составляют 0;0001 — 0,0002 B.

Экспериментально установлено, что для до25 стоверного контроля достаточен, например, uvar 0,01 В, а измеряемая аномалия составляет 30- 40 изменения напряжения питания, что обеспечивает ее превышение над уровнем погрешности измерительной уста30 новки, Величина шага ЛОсс устанавливается экспериментально. При достижении порогового напряжения питания Uccnop в зависимости напряжения логической единицы 0

35 от напряжения питания 0«проявляется аномалия (фиг. 2). Она заключается в том, что при изменении напряжения питания на один шаг(ЛО« -0,01 B) изменение выходного напряжения логической единицы

40 AU«< ЛОн, где ЛОНП вЂ” изменение напряжения логической "1" при снижении напряжения питания на шаг меньше порогового, ЛΠ— изменение напряжения логической единицы при изменении на шаг напряжения

45 питания, которое больше порогового. Причем для всех значений

0 > 0

50 при изменении Осс на одну и ту же величину

Л Он- const. (1) Исходя иэ условия (1), в качестве эталон55 ного значения выбирается величина Л Онэ, равная изменению напряжения логической

"1" при первом шаге снижения напряжения питания. Для определения величины порогового напряжения осуществляется сравне1675804

Ucc(l) = U ссн — Л Ucc, 15 ние изменения выходного напряжения логической "1" с эталонным при каждом шаге снижения напряжения питания. О достижении порогового напряжения судят по тому, что его снижение на шаг приводит к уменьшению изменения U по сравнению с эталонным.

Основным информативным параметром о наличии дефектов является разность между номинальным и пороговым напряжениями питания. Для определения пороговых значений информативного параметра берут

Л0н = 0ссн 0сспор (2) где U«H — номинальное напряжение питания;

Л UH — информативный параметр, Производят определительные испытания ограниченной выборки ТТЛ ИС. Для каждой, ТТЛ ИС устанавливают ЛUH. Определяют среднее значение параметра Л0н и его среднеквадратическое отклонение о. Установлено экспериментально, что закон распределения информативного параметра

Л0н близок к нормальному, следовательно, отбраковываются микросхемы в соответствии с критерием

ЛЦ, -au . ЛU. Au. +oW, (3) где Цф.— табличное значение квантиля нормального распределения с уровнем эначимьсти а.

Для а-0,05 величина 0са =3.

Экспериментально установлено, например, что для микросхем 1533 ЛАЗ Л U

- 1,8 В, ст 0,06 В, тогда условие (3) принимает вид

1,62 В Л0н 1,98 В.

Микросхемы 1533 ЛАЗ, у которых

ЛОн < 162В, имеют сильные утечки как в области коллекторного и эмиттерного переходов, так и замыкающие оба перехода между собой и на подложку. Микросхемы, у которых

Л0н > 1,98 В, имеют развитые объемные дефекты эмиттерного перехода, Таким образом, отбраковка ТТЛ ИС по значениям Л0н позволяет выявить утечки

5 эмиттерного перехода входящих транзисторов, что повышает достоверность контроля.

Формула изобретения

Способ контроля ТТЛ интегральных схем, в соответствии с которым на вход кон10 тролируемой ТТЛ интегральной схемы задают номинальное входное напряжение U» и текущие значения U«(i) напряжения питания в соответствии с формулой где l = 0 — n;

0ссн — номинальное значение напряжения питания;

20 Л 0« — шаг уменьшения напряжения питания, о т л и ч а ю щ. и и с я тем, что, с целью повышения достоверности контроля, уменьшают входное напряжение от номинального значения О» до значения, при ко25 тором напряжение логической единицы на выходе контролируемой ТТЛ интегральной схемы принимает минимально допустимое текущее значение, измеряют текущие значения напряжения логической единицы

30. 0«(l) на выходе контролируемой ТТЛ интегральной схемы и определяют значения приращений этого напряжения по формуле

Л0нп(1) = Uíï(l+ 1) — Uíï(l) 1, сравнивают значения ЛU«(l = 1,..., л) с эталонным зна35 чением Л Uнп(1 = О) и в случае Л U>+=1)...„ë)<

<Л 0нл(! — — О) измеряют значение напряжения питания контролируемой ТТЛ интегральной схемы Uccoop и в случае, если 0ссн—

Осспор > А считают контролируемую ТТЛ

40 интегральную схему негодной по объемным дефектам эмиттерного перехода, а при UccH—

0«п»<  — негодной по утечкам коллекторного и эмиттерного переходов, причем величины А и В определяются как нижняя и верхняя статистические границы по статической обработке измеренных значений

0ссн — Uccoop на партии ТТЛ интегральных схем.

1675804

3,5

3,0

2,D

Uce

2,8 3,0 3,5

Редактор Н.Бобкова

Корректор В.Гирняк

Заказ 2999 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 П

9,0

„l ф Ф,Х

Pa z.Z

Составитель В,Дворкин

Техред M.Моргентал