Блок формирования переноса

Иллюстрации

Показать всеРеферат

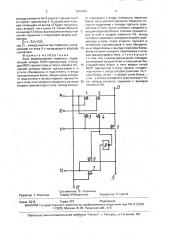

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ. Цель изобретения - уменьшение площади, занимаемой на кристалле, и повышение быстродействия. Блок формирования переноса содержит шину 15 питания, общую шину 14, вход 11 распространения переноса, вход 10 генерации переноса, входы 9 переноса, выход 13 переноса, вход 12 синхронизации, пять МОП-транзисторов 1-5 n-типа, два МОП- транзистора 6, 7 р-типа и элемент НЕ 8. 1 ил.

СОЮЗ СОВЕ (СКИХ

СОЦИАЛИСТИЧЕ СКИХ

РЕСПУБЛИК (sн5 G 06 F 7/50

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

",.с с .с ° > с с

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«» сс (21) 4630705/24 (22) 03.01.89 (46) 23.09.91. Бюл, ¹ 35 (72) В.П. Горский, В.В. Ковалев, С,С. Коваленко и М,В, Кривега (53) 681.325(088.8) (56) Патент США N 4016546, кл. G 06 F 7/50, 1977, Патент США ¹ 4471455, кл. G 06 F 7/50, 1984. (54) БЛОК ФОРМИРОВАНИЯ ПЕРЕНОСА

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ.

Целью изобретения является уменьшение площади, занимаемой на кристалле, и повышение быстродействия блока формирования переноса.

На чертеже приведена схема блока формирования переноса, Блок формирования переноса содержит

МОП-транзисторы и-типа 1 — 5 и р-типа 6, 7, элемент НЕ 8, имеет входы переноса 9, генерации переноса 10, распространения переноса 11 и синхронизации 12, выход переноса 13, подключен к общей шине 14 и шине питания 15, Блок работает следующим образом.

В исходном состоянии на вход синхронизации 12 подается нулевой сигнал. При этом закрывается транзистор 1 и открывается транзистор 7. Единичный потенциал с шины 15 поступает на вход элемента НЕ 8 и вход 9 данного блока. Нулевой сигнал с выхода элемента Н Е 8 закрывает транзистор 4 и открывает транзистор 6. В результате на выходе переноса 13 блока переноса пред„., Ц„„1679482 А1 (57) Изобретение относится к вычисгительной технике и может быть использовано в арифметических устройствах ЭВМ, Цель изобретения — уменьшение площади, занимаемой на кристалле, и повышение быстродействия. Блок формирования переноса содержит шину 15 питания, общую шину

14, вход 11 распространения переноса, вход

10 генерации переноса, входы 9 переноса, выход 13 переноса, вход 12 синхронизации, пять МОП-транзисторов 1 — 5 п-типа, два МОПтранзистора 6, 7 р-типа и элемент НЕ 8. 1 ил.

ыдущего разряда арифметического устройства, который подключен к входу переноса

9 данного блока, устанавливается единичн ы и поте н цивл.

В рабочем состоянии на вход 12 подается единичный сигнал, который открывает транзистор 1 и закрывает транзистор 7, э на входы 10 и 11 — сигналы генерации GI=XIYI и распространения PI=XI+YI переноса, где XI u

YI — i-e разряды входных слагаемых, Если

6;=0 и Р =О, то транзисторы 2, 3 и 5 будут закрыты и на выходе переноса 13 останется единичный потенциал, так как открыт транзистор 6 блока переноса предыдущего разряда. Если GI=1 и PI=0, то транзисторы 3 и 5 будут закрыты, но откроется транзистор 2, и нулевой потенциал с шины 14 поступит на выход 13. Если GI=O и PI=1, то транзистор 2 будет закрыт, но откроются транзисторы 3 и

5, и сигнал с входа 9 поступит на выход 13

Сопротивление открытого транзистора 6 значительно меньше сопротивления открытых транзисторов и-типа 1 — 5. Поэтому при подаче на вход 9 нулевого сигнала на входе элемента НЕ 8 установится потенциал, близкий к нулевому, и единичный сигнал с

1679482

Составитель В. Черников

Редактор Т, Иванова Техред M,Ìîðãåíòàë Корректор О. Ципле

Заказ 3215 Тираж 372 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 выхода элемента Н Е 8 закроет транзистор 6 и откроет транзистор 4. В результате нулевой потенциал на выход 13 будет поступать как с входа 9, так и шины 14, Таким образом на выходе 13 блока формируется инверсный 5 сигнал переноса в следующий разряд сумматора:

Ci+1= С Р +О Рь где С вЂ” инверсный сигнал переноса, поступающий на вход 9 с предыдущего разряда 10 сумматора.

Формула изобретения

Блок формирования переноса, содержащий четыре МОП-транзистора п-типа, два MOll-транзистора р-типа и элемент НЕ. 15 причем затворы первых транзисторов и- и р-типа объединены и подключены к входу синхронизации блока, общая шина которого подключена к истоку первого транзистора и-типа. сток которого соединен с истоком 20 второго транзистора п-типа, затвор которого подключен к входу генерации переноса блока, вход распространения переноса которого подключен к затвору третьего транзистора п-типа, исток которого соединен с входом переноса блока, стоками транзисторов р-типа и входом элемента НЕ, выход которого соединен с затвором второго транзистора р-типа, стоки второго, третьего и четвертого транзисторов и-типа объединены и подключены к выходу переноса блока, шина питания которого подключена к истокам транзисторов р-типа, о т л и ч а ю щ и йс я тем, что, с целью уменьшения площади, занимаемой на кристалле, и повышения быстродействия блока. в него введен пятый

МОП транзистор п-типа, затвор котодогс подключен к входу распространения пе.- с носа блока, исток — к общей шине блока, . сток — к истоку четвертого транзистора п-типа, затвор которого соединен с выходом элемента НЕ, а